This generational list of Intel processors attempts to present all of

Intel's

processors from the pioneering

4-bit 4004

The Intel 4004 is a 4-bit central processing unit (CPU) released by Intel Corporation in 1971. Sold for US$60, it was the first commercially produced microprocessor, and the first in a long line of Intel CPUs.

The 4004 was the first significa ...

(1971) to the present high-end offerings. Concise technical data is given for each product.

Latest

13th generation Core

Desktop (codenamed " Raptor Lake")

12th generation Core

Desktop (codenamed " Alder Lake")

Mobile (codenamed " Alder Lake")

11th generation Core

Desktop (codenamed " Rocket Lake")

Mobile (codenamed " Tiger Lake")

10th generation Core

Desktop (codenamed " Comet Lake")

Mobile (codenamed " Comet Lake", " Ice Lake", and " Amber Lake")

9th generation Core

Desktop (codenamed "

Coffee Lake Refresh

Coffee Lake is Intel's codename for its eighth generation Core microprocessor family, announced on September 25, 2017. It is manufactured using Intel's second 14 nm process node refinement. Desktop Coffee Lake processors introduced i5 and ...

")

8th generation Core

Desktop (codenamed " Coffee Lake")

Mobile (codenamed " Coffee Lake", " Amber Lake" and "

Whiskey Lake

Whiskey Lake is Intel's codename for a family of third 14 nm generation Skylake low-power mobile processors. Intel announced Whiskey Lake on August 28, 2018.

Changes

* 14++ nm process, same as Coffee Lake

* Increased turbo clocks (300� ...

")

7th generation Core

Desktop (codenamed " Kaby Lake" and " Skylake-X")

Mobile (codenamed " Kaby Lake" and "

Apollo Lake

Goldmont is a microarchitecture for low-power Atom, Celeron and Pentium branded processors used in systems on a chip (SoCs) made by Intel. They allow only one thread per core.

The ''Apollo Lake'' platform with 14 nm Goldmont core was unv ...

")

All processors

All processors are listed in chronological order.

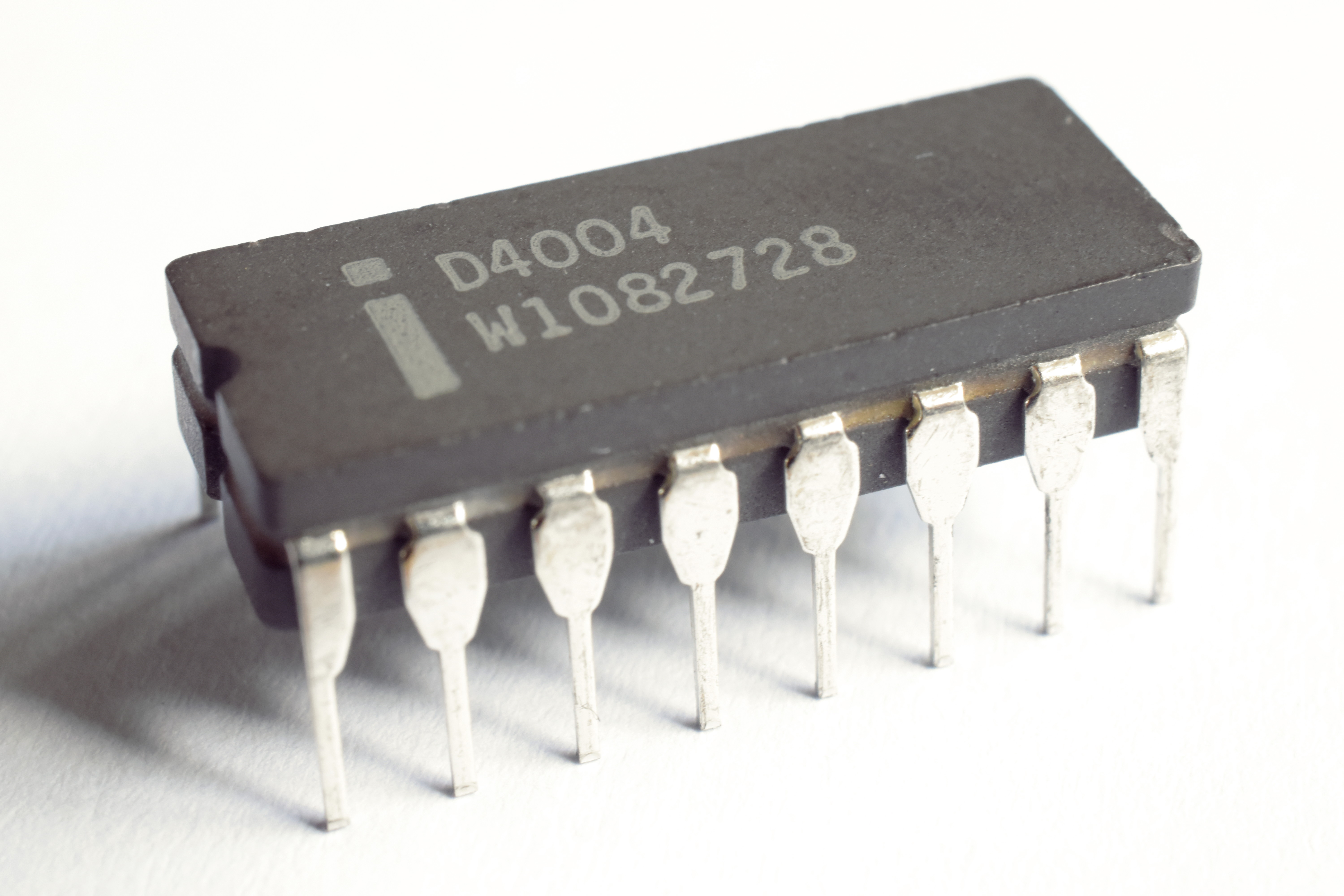

The 4-bit processors

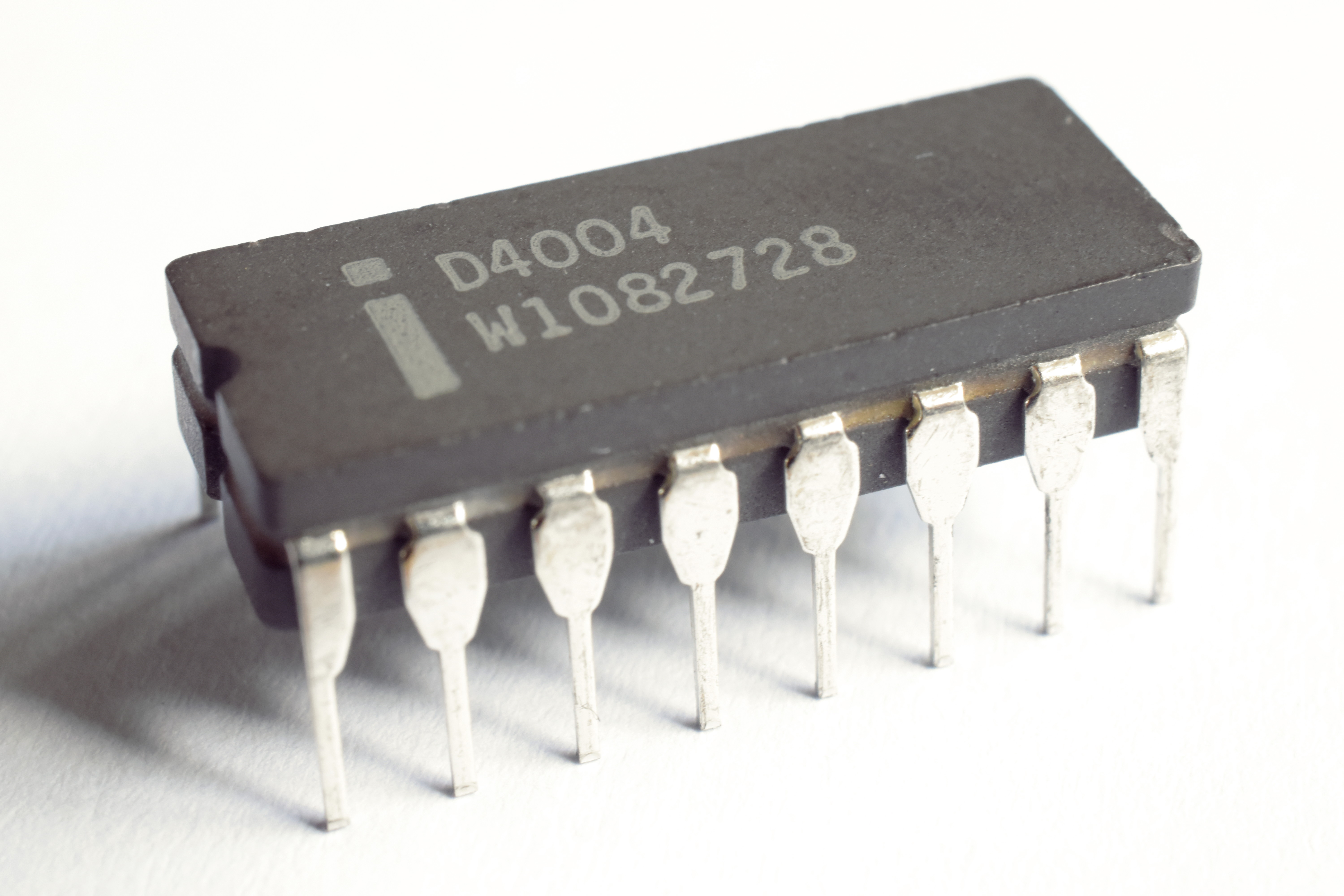

Intel 4004

First

microprocessor (single-chip IC processor)

* Introduced November 15, 1971

* Clock rate 740

kHz

* 0.07

MIPS

* Bus width: 4 bits (multiplexed address/data due to limited pins)

*

PMOS

* 2,300 transistors at 10

μm

The micrometre ( international spelling as used by the International Bureau of Weights and Measures; SI symbol: μm) or micrometer (American spelling), also commonly known as a micron, is a unit of length in the International System of Unit ...

*

Addressable memory 640

bytes

*

Program memory 4

KB (4096 B)

* Originally designed to be used in

Busicom

was a Japanese company that manufactured and sold computer-related products headquartered in Taito, Tokyo. It owned the rights to Intel's first microprocessor, the Intel 4004, which they created in partnership with Intel in 1970.

Busicom ask ...

calculator

MCS-4 family:

* 4004 –

CPU

A central processing unit (CPU), also called a central processor, main processor or just processor, is the electronic circuitry that executes instructions comprising a computer program. The CPU performs basic arithmetic, logic, controlling, and ...

* 4001 –

ROM & 4-bit Port

* 4002 –

RAM & 4-bit Port

* 4003 – 10-bit Shift Register

* 4008 – Memory+I/O Interface

* 4009 – Memory+I/O Interface

* 4211 – General Purpose Byte I/O Port

* 4265 – Programmable General Purpose I/O Device

* 4269 – Programmable Keyboard Display Device

* 4289 – Standard Memory Interface for MCS-4/40

* 4308 – 8192-bit (1024 × 8) ROM w/ 4-bit I/O Ports

* 4316 – 16384-bit (2048 × 8) Static ROM

* 4702 – 2048-bit (256 × 8) EPROM

* 4801 – 5.185 MHz Clock Generator Crystal for 4004/4201A or 4040/4201A

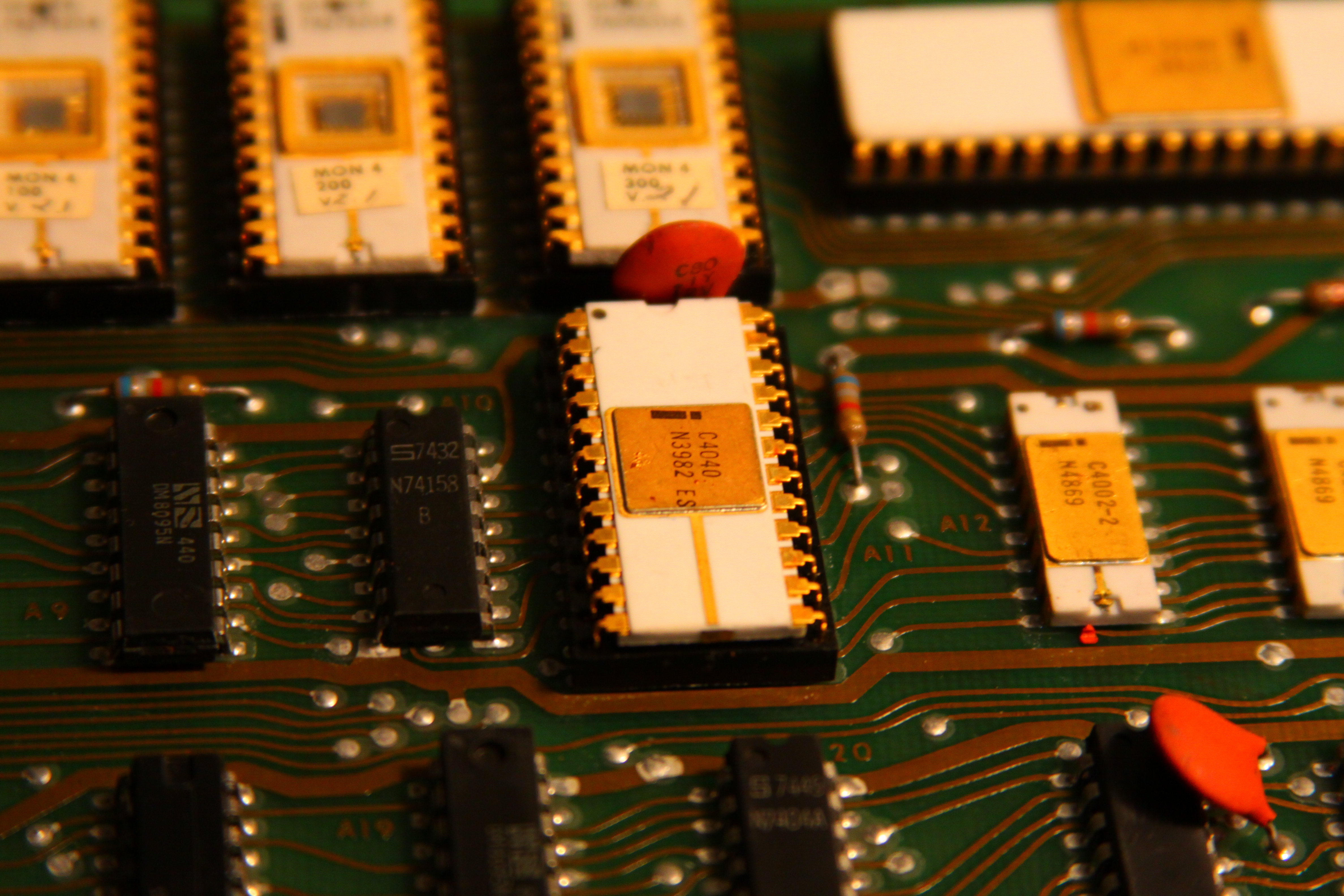

Intel 4040

* Introduced in 1974 by Intel

* Clock speed was 740 kHz (same as the 4004 microprocessor)

* 3,000 transistors

* Interrupt features were available

* Programmable memory size: 8 KB (8192 B)

* 640 bytes of data memory

* 24-pin DIP

The

8-bit

In computer architecture, 8-bit Integer (computer science), integers or other Data (computing), data units are those that are 8 bits wide (1 octet (computing), octet). Also, 8-bit central processing unit (CPU) and arithmetic logic unit (ALU) arc ...

processors

8008

* Introduced April 1, 1972

* Clock rate 500 kHz (8008-1: 800 kHz)

* 0.05 MIPS

* Bus width: 8 bits (multiplexed address/data due to limited pins)

* Enhancement load

PMOS logic

* 3,500 transistors at 10 μm

* Addressable memory 16 KB

* Typical in early 8-bit microcomputers, dumb terminals, general calculators, bottling machines

* Developed in tandem with 4004

* Originally intended for use in the

Datapoint 2200 microcomputer

* Key volume deployment in Texas Instruments 742 microcomputer in >3,000 Ford dealerships

8080

* Introduced April 1, 1974

* Clock rate 2 MHz (very rare 8080B: 3 MHz)

* 0.29 MIPS

* Data bus width: 8 bits, address bus: 16 bits

* Enhancement load

NMOS logic

* 4,500 transistors at 6 μm

*

Assembly language

In computer programming, assembly language (or assembler language, or symbolic machine code), often referred to simply as Assembly and commonly abbreviated as ASM or asm, is any low-level programming language with a very strong correspondence be ...

downward compatible with 8008

* Addressable memory 64 KB (64 × 1024 B)

* Up to 10× the performance of the 8008

* Used in e.g. the

Altair 8800

The Altair 8800 is a microcomputer designed in 1974 by MITS and based on the Intel 8080 CPU. Interest grew quickly after it was featured on the cover of the January 1975 issue of Popular Electronics and was sold by mail order through advertiseme ...

,

traffic light controller,

cruise missile

A cruise missile is a guided missile used against terrestrial or naval targets that remains in the atmosphere and flies the major portion of its flight path at approximately constant speed. Cruise missiles are designed to deliver a large warhe ...

* Required six support chips versus 20 for the 8008

8085

* Introduced March 1976

* Clock rate 3 MHz

* 0.37

MIPS

* Data bus width: 8 bits, address bus: 16 bits

* Depletion load

NMOS logic

* 6,500 transistors at

3 μm

*

Binary compatible downward with the 8080

* Used in

Toledo scales. Also used as a computer peripheral controller – modems, hard disks, printers, etc.

*

CMOS

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss", ) is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFE ...

80C85 in

Mars Sojourner

''Sojourner'' is a robotic Mars rover that landed in the Ares Vallis channel in the Chryse Planitia region of the Oxia Palus quadrangle on July 4, 1997. ''Sojourner'' was operational on Mars for 92 sols (95 Earth days). It was the first whee ...

,

Radio Shack Model 100 portable

Microcontrollers

They are ICs with CPU, RAM, ROM (or PROM or EPROM), I/O Ports, Timers & Interrupts

Intel 8048

The MCS-48 microcontroller series, Intel's first microcontroller, was originally released in 1976. Its first members were 8048, 8035 and 8748. The 8048 is probably the most prominent member of the family. Initially, this family was produced u ...

* Single

accumulator Harvard architecture

MCS-48 family:

* Intel 8020 – Single-Component 8-bit Microcontroller, 1 KB ROM, 64 Byte RAM, 13 I/O ports

* Intel 8021 – Single-Component 8-bit Microcontroller, 1 KB ROM, 64 Byte RAM, 21 I/O ports

* Intel 8022 – Single-Component 8-bit Microcontroller, With On-Chip A/D Converter

* Intel 8035 – Single-Component 8-bit Microcontroller, 64 Byte RAM

* Intel 8039 – Single-Component 8-bit Microcontroller, 128 Byte RAM

* Intel 8040 – Single-Component 8-bit Microcontroller, 256 Byte RAM

* Intel 8048 – Single-Component 8-bit Microcontroller, 1 KB ROM, 64 byte RAM, 27 I/O ports, 0.73 MIPS @ 11 MHz

* Intel 8049 – Single-Component 8-bit Microcontroller, 2 KB ROM, 128 byte RAM, 27 I/O ports,

* Intel 8050 – Single-Component 8-bit Microcontroller, 4 KB ROM, 256 byte RAM, 27 I/O ports,

* Intel 8748 – Single-Component 8-bit Microcontroller, 1 KB EPROM, 64 byte RAM, 27 I/O ports,

* Intel 8749 – Single-Component 8-bit Microcontroller, 2 KB EPROM, 128 byte RAM, 27 I/O ports,

* Intel 87P50 – Single-Component 8-bit Microcontroller, ext. ROM socket (2758/2716/2732), 256 byte RAM, 27 I/O ports

* Intel 8648 – Single-Component 8-bit Microcontroller, 1 KB OTP EPROM, 64 byte RAM, 27 I/O ports

* Intel 8041 – Universal Peripheral Interface 8-bit Slave Microcontroller, 1 KB ROM, 64 byte RAM

* Intel 8041AH – Universal Peripheral Interface 8-bit Slave Microcontroller, 1 KB ROM, 128 byte RAM

* Intel 8641 – Universal Peripheral Interface 8-bit Slave Microcontroller ?

* Intel 8741 – Universal Peripheral Interface 8-bit Slave Microcontroller, 1 KB EPROM, 64 byte RAM

* Intel 8741AH – Universal Peripheral Interface 8-bit Slave Microcontroller, 1 KB EPROM, 128 byte RAM

* Intel 8042 – Universal Peripheral Interface 8-bit Slave Microcontroller, 2 KB ROM, 256 byte RAM

* Intel 8742 – Universal Peripheral Interface 8-bit Slave Microcontroller, 2 KB EPROM, 128 byte RAM

* Intel 8742AH – Universal Peripheral Interface 8-bit Slave Microcontroller, 2 KB OTP EPROM, 256 byte RAM

* Intel 8243 – Input/Output Expander. The available 28-pin

PLCC version in sampling for first quarter of 1986.

* Intel 8244 – General Purpose Graphics Display Device (ASIC NTSC/SECAM)

* Intel 8245 – General Purpose Graphics Display Device (ASIC PAL)

Intel 8051

* Single

accumulator Harvard architecture

MCS-51

The Intel MCS-51 (commonly termed 8051) is a single chip microcontroller (MCU) series developed by Intel in 1980 for use in embedded systems. The architect of the Intel MCS-51 instruction set was John H. Wharton. Intel's original versions were p ...

family:

* 8031 – 8-bit Control-Oriented Microcontroller

* 8032 – 8-bit Control-Oriented Microcontroller

* 8044 – High Performance 8-bit Microcontroller

* 8344 – High Performance 8-bit Microcontroller

* 8744 – High Performance 8-bit Microcontroller

* 8051 – 8-bit Control-Oriented Microcontroller

* 8052 – 8-bit Control-Oriented Microcontroller

* 8054 – 8-bit Control-Oriented Microcontroller

* 8058 – 8-bit Control-Oriented Microcontroller

* 8351 – 8-bit Control-Oriented Microcontroller

* 8352 – 8-bit Control-Oriented Microcontroller

* 8354 – 8-bit Control-Oriented Microcontroller

* 8358 – 8-bit Control-Oriented Microcontroller

* 8751 – 8-bit Control-Oriented Microcontroller

* 8752 – 8-bit Control-Oriented Microcontroller

* 8754 – 8-bit Control-Oriented Microcontroller

* 8758 – 8-bit Control-Oriented Microcontroller

Intel 80151

The Intel MCS-51 (commonly termed 8051) is a single chip microcontroller (MCU) series developed by Intel in 1980 for use in embedded systems. The architect of the Intel MCS-51 instruction set was John H. Wharton. Intel's original versions were po ...

* Single

accumulator Harvard architecture

MCS-151

The Intel MCS-51 (commonly termed 8051) is a single chip microcontroller (MCU) series developed by Intel in 1980 for use in embedded systems. The architect of the Intel MCS-51 instruction set was John H. Wharton. Intel's original versions were po ...

family:

* 80151 – High Performance 8-bit Control-Oriented Microcontroller

* 83151 – High Performance 8-bit Control-Oriented Microcontroller

* 87151 – High Performance 8-bit Control-Oriented Microcontroller

* 80152 – High Performance 8-bit Control-Oriented Microcontroller

* 83152 – High Performance 8-bit Control-Oriented Microcontroller

Intel 80251

The Intel MCS-51 (commonly termed 8051) is a single chip microcontroller (MCU) series developed by Intel in 1980 for use in embedded systems. The architect of the Intel MCS-51 instruction set was John H. Wharton. Intel's original versions were po ...

* Single

accumulator Harvard architecture

MCS-251 family:

* 80251 – 8/16/

32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculation ...

Microcontroller

* 80252 – 8/16/32-bit Microcontroller

* 80452 – 8/16/32-bit Microcontroller

* 83251 – 8/16/32-bit Microcontroller

* 87251 – 8/16/32-bit Microcontroller

* 87253 – 8/16/32-bit Microcontroller

MCS-96 family

* 8061 – 16-bit Microcontroller (parent of MCS-96 family ROMless With A/D, most sold to Ford)

* 8094 –

16-bit

16-bit microcomputers are microcomputers that use 16-bit microprocessors.

A 16-bit register can store 216 different values. The range of integer values that can be stored in 16 bits depends on the integer representation used. With the two mos ...

Microcontroller (48-Pin ROMLess Without A/D)

* 8095 – 16-bit Microcontroller (48-Pin ROMLess With A/D)

* 8096 – 16-bit Microcontroller (68-Pin ROMLess Without A/D)

* 8097 – 16-bit Microcontroller (68-Pin ROMLess With A/D)

* 8394 – 16-bit Microcontroller (48-Pin With ROM Without A/D)

* 8395 – 16-bit Microcontroller (48-Pin With ROM With A/D)

* 8396 – 16-bit Microcontroller (68-Pin With ROM Without A/D)

* 8397 – 16-bit Microcontroller (68-Pin With ROM With A/D)

* 8794 – 16-bit Microcontroller (48-Pin With EROM Without A/D)

* 8795 – 16-bit Microcontroller (48-Pin With EROM With A/D)

* 8796 – 16-bit Microcontroller (68-Pin With EROM Without A/D)

* 8797 – 16-bit Microcontroller (68-Pin With EROM With A/D)

* 8098 – 16-bit Microcontroller

* 8398 – 16-bit Microcontroller

* 8798 – 16-bit Microcontroller

* 80196 – 16-bit Microcontroller

* 83196 – 16-bit Microcontroller

* 87196 – 16-bit Microcontroller

* 80296 – 16-bit Microcontroller

The bit-slice processor

3000 family

Introduced in the third quarter of 1974, these

bit-slicing

Bit slicing is a technique for constructing a Processor (computing), processor from modules of processors of smaller bit width, for the purpose of increasing the word length; in theory to make an arbitrary ''n''-bit central processing unit ( ...

components used

bipolar

Bipolar may refer to:

Astronomy

* Bipolar nebula, a distinctive nebular formation

* Bipolar outflow, two continuous flows of gas from the poles of a star

Mathematics

* Bipolar coordinates, a two-dimensional orthogonal coordinate system

* Bipolar ...

Schottky transistors. Each component implemented two bits of a processor function; packages could be interconnected to build a processor with any desired word length.

Members of the family:

* 3001 – Microcontrol Unit

* 3002 – 2-bit Arithmetic Logic Unit slice

* 3003 – Look-ahead Carry Generator

* 3205 – High-performance 1 of 8 Binary Decoder

* 3207 – Quad Bipolar-to-MOS Level Shifter and Driver

* 3208 – Hex Sense Amp and Latch for MOS Memories

* 3210 – TTL-to-MOS Level Shifter and High Voltage Clock Driver

* 3211 – ECL-to-MOS Level Shifter and High Voltage Clock Driver

* 3212 – Multimode Latch Buffer

* 3214 – Interrupt Control Unit

* 3216 – Parallel, Inverting Bi-Directional Bus Driver

* 3222 – Refresh Controller for 4K (4096 B) NMOS DRAMs

* 3226 – Parallel, Inverting Bi-Directional Bus Driver

* 3232 – Address Multiplexer and Refresh Counter for 4K DRAMs

* 3242 – Address Multiplexer and Refresh Counter for 16K (16 × 1024 B) DRAMs

* 3245 – Quad Bipolar TTL-to-MOS Level Shifter and Driver for 4K

* 3246 – Quad Bipolar ECL-to-MOS Level Shifter and Driver for 4K

* 3404 – High-performance 6-bit Latch

* 3408 – Hex Sense Amp and Latch for MOS Memories

* 3505 – Next generation processor

Bus width 2''n'' bits data/address (depending on number ''n'' of slices used)

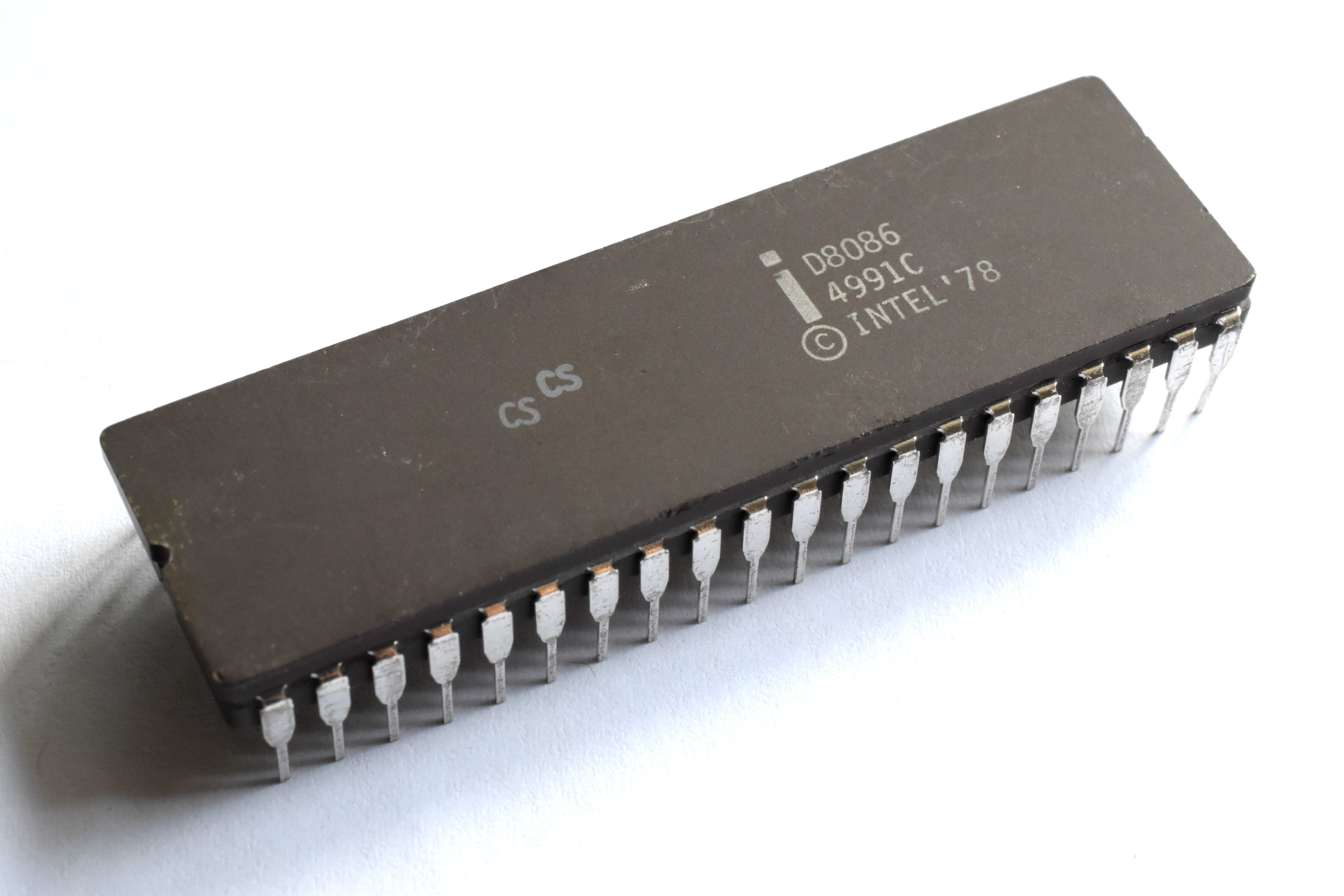

The

16-bit

16-bit microcomputers are microcomputers that use 16-bit microprocessors.

A 16-bit register can store 216 different values. The range of integer values that can be stored in 16 bits depends on the integer representation used. With the two mos ...

processors: MCS-86 family

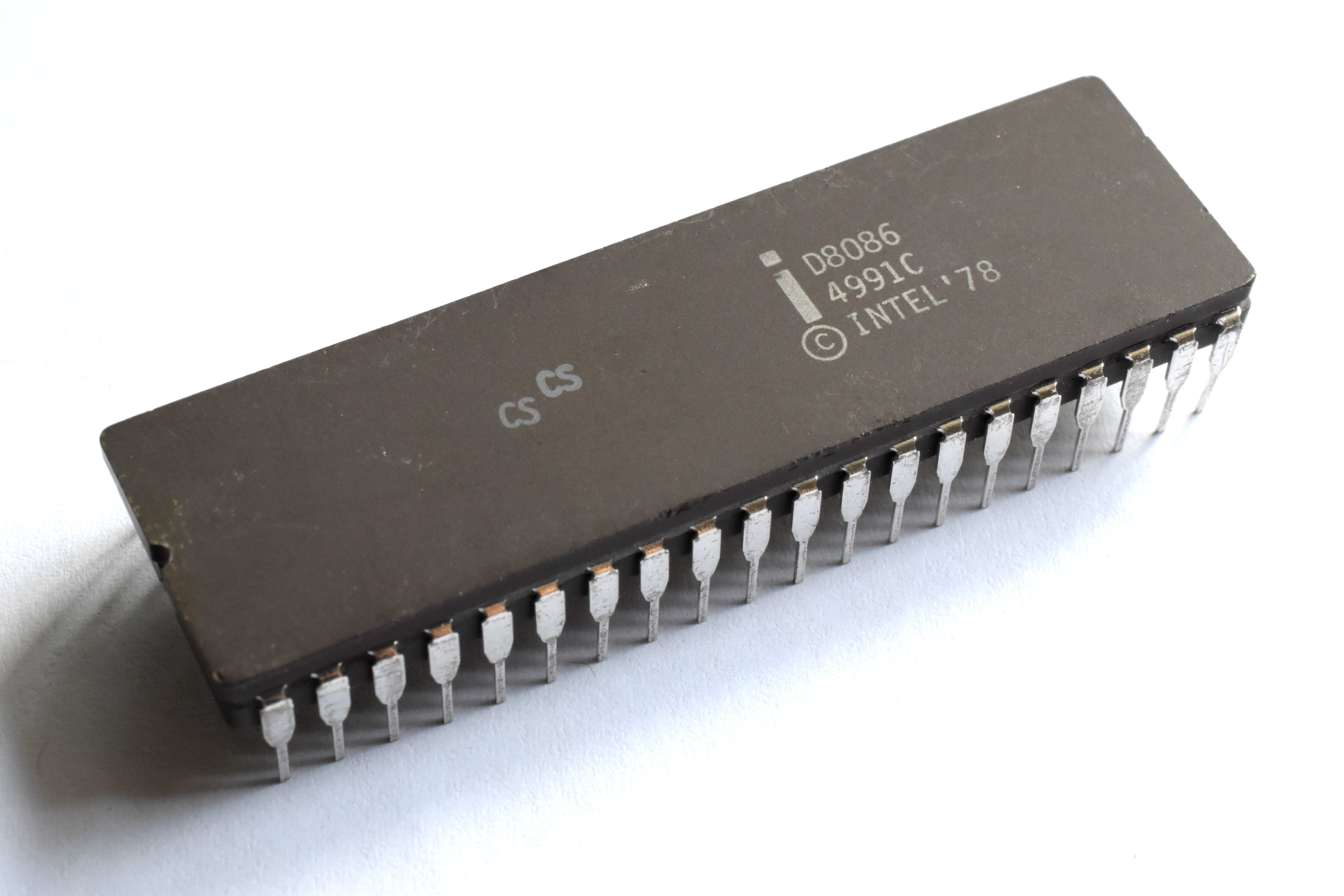

8086

* Introduced June 8, 1978

* Clock rates:

** 5 MHz, 0.33 MIPS

** 8 MHz, 0.66 MIPS

** 10 MHz, 0.75 MIPS

* The memory is divided into odd and even banks. It accesses both banks concurrently to read 16 bits of data in one clock cycle

* Data bus width: 16 bits, address bus: 20 bits

* 29,000 transistors at 3 μm

* Addressable memory 1 megabyte (1024B)

* Up to 10× the performance of 8080

* First used in the Compaq Deskpro IBM PC-compatible computers. Later used in portable computing, and in the

IBM PS/2

The Personal System/2 or PS/2 is IBM's second generation of personal computers. Released in 1987, it officially replaced the IBM PC, XT, AT, and PC Convertible in IBM's lineup. Many of the PS/2's innovations, such as the 16550 UART (serial po ...

Model 25 and

Model 30. Also used in the

AT&T PC6300 / Olivetti M24, a popular IBM PC-compatible (predating the IBM PS/2 line)

* Used

segment register

Memory segmentation is an operating system memory management technique of division of a computer's primary memory into segments or sections. In a computer system using segmentation, a reference to a memory location includes a value that identifie ...

s to access more than 64 KB of data at once, which many programmers complained made their work excessively difficult.

* The first x86 CPU

* Later renamed the iAPX 86

[Intel IAPX 86,88 User's Manual, August 1981, Intel order number 210201-001]

8088

* Introduced June 1, 1979

* Clock rates:

** 4.77 MHz, 0.33 MIPS

** 8 MHz, 0.66 MIPS

* 16-bit internal architecture

* External data bus width: 8 bits, address bus: 20 bits

* 29,000 transistors at 3 μm

* Addressable memory 1 megabyte

* Identical to 8086 except for its 8-bit external bus (hence an ''8'' instead of a ''6'' at the end); identical Execution Unit (EU), different Bus Interface Unit (BIU)

* Used in

IBM PC

The IBM Personal Computer (model 5150, commonly known as the IBM PC) is the first microcomputer released in the IBM PC model line and the basis for the IBM PC compatible de facto standard. Released on August 12, 1981, it was created by a team ...

and PC-XT and compatibles

* Later renamed the iAPX 88

80186

* Introduced 1982

* Clock rates

** 6 MHz, > 1 MIPS

* 55,000 transistors

* Included two timers, a

DMA controller, and an

interrupt controller on the chip in addition to the processor (these were at fixed addresses which differed from the IBM PC, although it was used by several PC compatible vendors such as Australian company Cleveland)

* Added a few opcodes and exceptions to the 8086 design, otherwise identical instruction set to 8086 and 8088

** BOUND, ENTER, LEAVE

** INS, OUTS

** IMUL imm, PUSH imm, PUSHA, POPA

** RCL/RCR/ROL/ROR/SHL/SHR/SAL/SAR reg, imm

* Address calculation and shift operations are faster than 8086

* Used mostly in embedded applications – controllers, point-of-sale systems, terminals, and the like

* Used in several non-PC compatible

DOS computers including

RM Nimbus,

Tandy 2000, and CP/M 86 Televideo PM16 server

* Later renamed to iAPX 186

80188

The Intel 80188 microprocessor was a variant of the Intel 80186. The 80188 had an 8-bit external data bus instead of the 16-bit bus of the 80186; this made it less expensive to connect to peripherals. The 16-bit registers and the one megabyte add ...

* A version of the 80186 with an 8-bit external data bus

* Later renamed the iAPX 188

80286

* Introduced February 2, 1982

* Clock rates:

** 6 MHz, 0.9 MIPS

** 8 MHz, 10 MHz, 1.5 MIPS

** 12.5 MHz, 2.66 MIPS

** 16 MHz, 20 MHz and 25 MHz available.

* Data bus width: 16 bits, address bus: 24 bits

* Included memory protection hardware to support multitasking operating systems with per-process address space.

* 134,000 transistors at

1.5 μm

* Addressable memory 16

MB

* Added protected-mode features to 8086 with essentially the same instruction set

* 3–6× the performance of the 8086

* Widely used in

IBM PC AT and AT clones contemporary to it

32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculation ...

processors: the non-x86 microprocessors

iAPX 432

The iAPX 432 (''Intel Advanced Performance Architecture'') is a discontinued computer architecture introduced in 1981. It was Intel's first 32-bit processor design. The main processor of the architecture, the ''general data processor'', is impl ...

* Introduced January 1, 1981 as Intel's first

32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculation ...

microprocessor

* Multi-chip CPU

* Object/capability architecture

* Microcoded operating system primitives

* One terabyte virtual address space

* Hardware support for fault tolerance

* Two-chip General Data Processor (GDP), consists of 43201 and 43202

* 43203 Interface Processor (IP) interfaces to I/O subsystem

* 43204 Bus Interface Unit (BIU) simplifies building multiprocessor systems

* 43205 Memory Control Unit (MCU)

* Architecture and execution unit internal data base paths: 32 bits

* Clock rates:

** 5 MHz

** 7 MHz

** 8 MHz

i960 a.k.a. 80960

* Introduced April 5, 1988

*

RISC

In computer engineering, a reduced instruction set computer (RISC) is a computer designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set comput ...

-like

32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculation ...

architecture

* Predominantly used in embedded systems

* Evolved from the capability processor developed for the

BiiN joint venture with

Siemens

Siemens AG ( ) is a German multinational conglomerate corporation and the largest industrial manufacturing company in Europe headquartered in Munich with branch offices abroad.

The principal divisions of the corporation are ''Industry'', '' ...

* Many variants identified by two-letter suffixes

i860 a.k.a. 80860

* Introduced February 26, 1989

*

RISC

In computer engineering, a reduced instruction set computer (RISC) is a computer designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set comput ...

32/

64-bit architecture, with floating point pipeline characteristics very visible to programmer

* Used in the

Intel iPSC/860 Hypercube

In geometry, a hypercube is an ''n''-dimensional analogue of a square () and a cube (). It is a closed, compact, convex figure whose 1- skeleton consists of groups of opposite parallel line segments aligned in each of the space's dimensions, ...

parallel supercomputer

* Mid-life kicker in the i870 processor (primarily a speed bump, some refinement/extension of instruction set)

* Used in the

Intel Delta

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 series ...

massively parallel supercomputer prototype, emplaced at

California Institute of Technology

* Used in the

Intel Paragon

The Intel Paragon is a discontinued series of massively parallel supercomputers that was produced by Intel in the 1990s. The Paragon XP/S is a productized version of the experimental ''Touchstone Delta'' system that was built at Caltech, launched ...

massively parallel supercomputer, emplaced at

Sandia National Laboratory

XScale

* Introduced August 23, 2000

*

32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculation ...

RISC

In computer engineering, a reduced instruction set computer (RISC) is a computer designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set comput ...

microprocessor based on the

ARM architecture

ARM (stylised in lowercase as arm, formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a family of reduced instruction set computer (RISC) instruction set architectures for computer processors, configured ...

* Many variants, such as the PXA2xx applications processors, IOP3xx I/O processors and IXP2xxx and IXP4xx network processors

32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculation ...

processors: the 80386 range

80386DX

* Introduced October 17, 1985

* Clock rates:

** 16 MHz, 5 MIPS

** 20 MHz, 6 to 7 MIPS, introduced February 16, 1987

** 25 MHz, 7.5 MIPS, introduced April 4, 1988

** 33 MHz, 9.9 MIPS (9.4 SPECint92 on Compaq/i 16 KB L2), introduced April 10, 1989

* Data bus width: 32 bits, address bus: 32 bits

* 275,000 transistors at 1 μm

* Addressable memory 4

GB (4 × 1024 B)

*

Virtual memory 64

TB (64 × 1024 B)

* First x86 chip to handle

32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculation ...

data sets

* Reworked and expanded memory protection support including

paged virtual memory and virtual-86 mode, features required at the time by

Xenix and

Unix. This memory capability spurred the development and availability of

OS/2 and is a fundamental requirement for modern operating systems like

Linux,

Windows, and

macOS

* First used by Compaq in the

Deskpro 386. Used in desktop computing

* Unlike the DX naming convention of the 486 chips, it had no math co-processor

* Later renamed Intel386 DX

80386SX

* Introduced June 16, 1988

* Clock rates:

** 16 MHz, 2.5 MIPS

** 20 MHz, 3.1 MIPS, introduced January 25, 1989

** 25 MHz, 3.9 MIPS, introduced January 25, 1989

** 33 MHz, 5.1 MIPS, introduced October 26, 1992

* 32-bit internal architecture

* External data bus width: 16 bits

* External address bus width: 24 bits

* 275,000 transistors at 1 μm

* Addressable memory 16 MB

* Virtual memory 64 TB

* Narrower buses enable low-cost 32-bit processing

* Used in entry-level desktop and portable computing

* No math co-processor

* No commercial software used protected mode or virtual storage for many years

* Later renamed Intel386 SX

80376

* Introduced January 16, 1989; discontinued June 15, 2001

* Variant of 386SX intended for embedded systems

* No "real mode", starts up directly in "protected mode"

* Replaced by much more successful

80386EX from 1994

80386SL

* Introduced October 15, 1990

* Clock rates:

** 20 MHz, 4.21 MIPS

** 25 MHz, 5.3 MIPS, introduced September 30, 1991

* 32-bit internal architecture

* External bus width: 16 bits

* 855,000 transistors at 1 μm

* Addressable memory 4 GB

* Virtual memory 64 TB

* First chip specifically made for portable computers because of low power consumption of chip

* Highly integrated, includes cache, bus, and memory controllers

80386EX

* Introduced August 1994

* Variant of 80386SX intended for

embedded systems

* Static core (i.e. may run as slowly (and thus, power efficiently) as desired) down to full halt

* On-chip peripherals:

** Clock and power management

** Timers/counters

**

Watchdog timer

** Serial I/O units (sync and async) and parallel I/O

**

DMA

DMA may refer to:

Arts

* ''DMA'' (magazine), a defunct dance music magazine

* Dallas Museum of Art, an art museum in Texas, US

* Danish Music Awards, an award show held in Denmark

* BT Digital Music Awards, an annual event in the UK

* Doctor of M ...

** RAM refresh

**

JTAG

JTAG (named after the Joint Test Action Group which codified it) is an Technical standard, industry standard for verifying designs and testing printed circuit boards after manufacture.

JTAG implements standards for on-chip instrumentation in ele ...

test logic

* Significantly more successful than the 80376

* Used aboard several orbiting satellites and microsatellites

* Used in NASA's

FlightLinux project

32-bit processors: the 80486 range

80486DX

* Introduced April 10, 1989

* Clock rates:

** 25 MHz, 20 MIPS (16.8 SPECint92, 7.40 SPECfp92)

** 33 MHz, 27 MIPS (22.4 SPECint92 on Micronics M4P 128 KB L2), introduced May 7, 1990

** 50 MHz, 41 MIPS (33.4 SPECint92, 14.5 SPECfp92 on Compaq/50L 256 KB L2), introduced June 24, 1991

* Bus width: 32 bits

* 1.2 million transistors at 1 μm; the 50 MHz was at 0.8 μm

* Addressable memory 4 GB

* Virtual memory 64 TB

*

Level 1 cache of 8 KB on chip

* Math coprocessor on chip

* 50× performance of the 8088

* Officially named Intel486 DX

* Used in desktop computing and servers

* Family 4 model 1

80486SX

The Intel 486, officially named i486 and also known as 80486, is a microprocessor. It is a higher-performance follow-up to the Intel 386. The i486 was introduced in 1989. It represents the fourth generation of binary compatible CPUs following the ...

* Introduced April 22, 1991

* Clock rates:

** 16 MHz, 13 MIPS

** 20 MHz, 16.5 MIPS, introduced September 16, 1991

** 25 MHz, 20 MIPS (12 SPECint92), introduced September 16, 1991

** 33 MHz, 27 MIPS (15.86 SPECint92), introduced September 21, 1992

* Bus width: 32 bits

* 1.185 million transistors at 1 μm and 900,000 at 0.8 μm

* Addressable memory 4 GB

* Virtual memory 64 TB

* Identical in design to 486DX but without a math coprocessor. The first version was an 80486DX with disabled math coprocessor in the chip and different pin configuration. If the user needed math coprocessor capabilities, he must add 487SX which was actually a 486DX with different pin configuration to prevent the user from installing a 486DX instead of 487SX, so with this configuration 486SX+487SX you had 2 identical CPU's with only 1 effectively turned on

* Officially named Intel486 SX

* Used in low-cost entry to 486 CPU desktop computing, as well as extensively in low cost mobile computing

* Upgradable with the

Intel OverDrive processor

* Family 4 model 2

80486DX2

The Intel i486DX2, rumored as 80486DX2 (later renamed IntelDX2) is a CPU produced by Intel that was first introduced in 1992. The i486DX2 was nearly identical to the i486DX, but it had additional clock multiplier circuitry. It was the first chi ...

* Introduced March 3, 1992

* Runs at twice the speed of the external bus (FSB)

* Fits in Socket 3

* Clock rates:

** 40 MHz

** 50 MHz, 41 MIPS

** 66 MHz, 54 MIPS

* Officially named Intel486 DX2

* Family 4 model 3

80486SL

* Introduced November 9, 1992

* Clock rates:

** 20 MHz, 15.4 MIPS

** 25 MHz, 19 MIPS

** 33 MHz, 25 MIPS

* Bus width: 32 bits

* 1.4 million transistors at 0.8 μm

* Addressable memory 4 GB

* Virtual memory 64 TB

* Officially named Intel486 SL

* Used in notebook computers

* Family 4 model 4

80486DX4

* Introduced March 7, 1994

* Clock rates:

** 75 MHz, 53 MIPS (41.3 SPECint92, 20.1 SPECfp92 on Micronics M4P 256 KB L2)

** 100 MHz, 70.7 MIPS (54.59 SPECint92, 26.91 SPECfp92 on Micronics M4P 256 KB L2)

* 1.6 million transistors at 0.6 μm

* Bus width: 32 bits

* Addressable memory 4 GB

* Virtual memory 64 TB

*

Socket 3 168-pin

PGA Package, or 208

sq. ftP package

* Officially named Intel486 DX4

* Used in high performance entry-level desktops and value notebooks

* Family 4 model 8

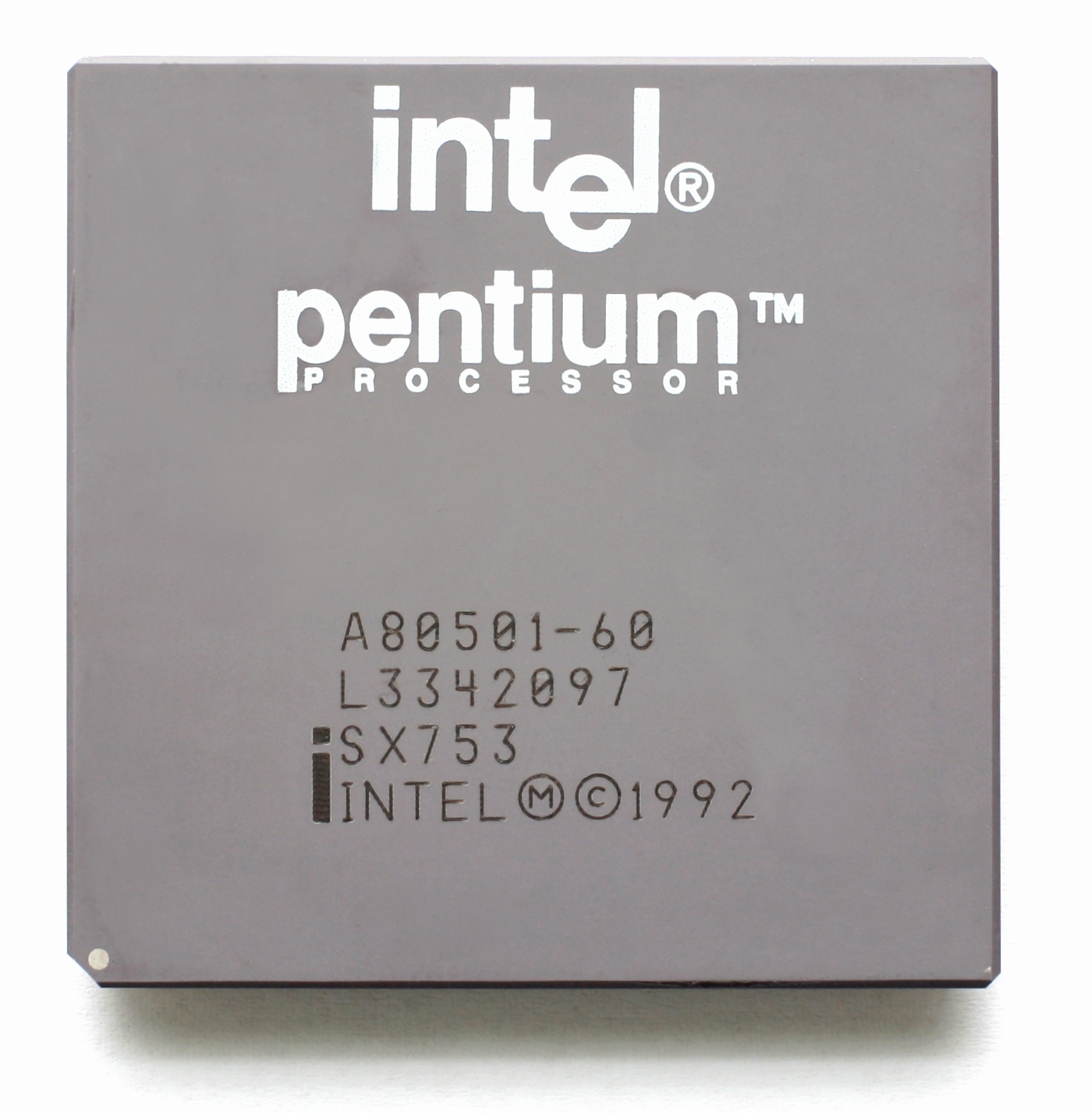

32-bit processors: P5 microarchitecture

Original Pentium

* Bus width: 64 bits

* System bus clock rate 60 or 66 MHz

* Address bus: 32 bits

* Addressable memory 4 GB

* Virtual memory 64 TB

*

Superscalar

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a sup ...

architecture

* Runs on 3.3 volts (except the very first generation "P5")

* Used in desktops

* 8 KB of instruction

cache

* 8 KB of data cache

* P5 –

0.8 μm process technology

** Introduced March 22, 1993

** 3.1 million transistors

** The only Pentium to run on 5 Volts

**

Socket 4 273 pin PGA Package

** Package dimensions 2.16 in × 2.16 in

** Family 5 model 1

** Variants

*** 60 MHz, 100 MIPS (70.4 SPECint92, 55.1 SPECfp92 on Xpress 256 KB L2)

*** 66 MHz, 112 MIPS (77.9 SPECint92, 63.6 SPECfp92 on Xpress 256 KB L2)

* P54 –

0.6 μm process technology

**

Socket 5 296/320-pin PGA package

** 3.2 million transistors

** Variants

*** 75 MHz, 126.5 MIPS (2.31 SPECint95, 2.02 SPECfp95 on Gateway P5 256K L2)

**** Introduced October 10, 1994

*** 90, 100 MHz, 149.8 and 166.3 MIPS respectively (2.74 SPECint95, 2.39 SPECfp95 on Gateway P5 256K L2 and 3.30 SPECint95, 2.59 SPECfp95 on Xpress 1ML2 respectively)

**** Introduced March 7, 1994

* P54CQS –

0.35 μm process technology

**

Socket 5 296/320 pin PGA package

** 3.2 million transistors

** Variants

*** 120 MHz, 203 MIPS (3.72 SPECint95, 2.81 SPECfp95 on Xpress 1 MB L2)

**** Introduced March 27, 1995

*

P54CS –

0.35 μm process technology

** 3.3 million transistors

** 90 mm

2 die size

** Family 5 model 2

** Variants

**

Socket 5 296/320-pin PGA package

*** 133 MHz, 218.9 MIPS (4.14 SPECint95, 3.12 SPECfp95 on Xpress 1 MB L2)

**** Introduced June 12, 1995

*** 150, 166 MHz, 230 and 247 MIPS respectively

**** Introduced January 4, 1996

**

Socket 7 296/321-pin PGA package

*** 200 MHz, 270 MIPS (5.47 SPECint95, 3.68 SPECfp95)

**** Introduced June 10, 1996

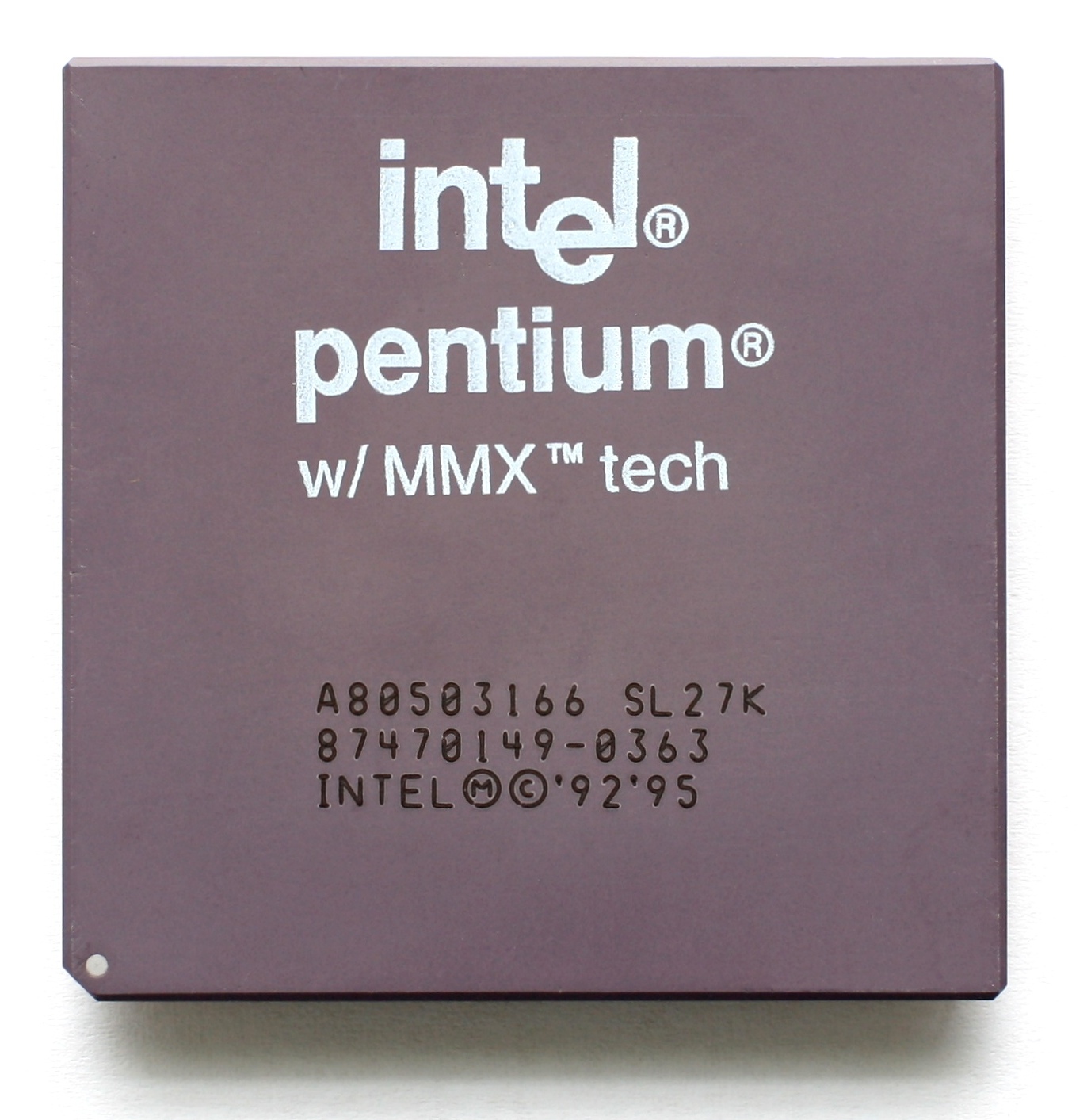

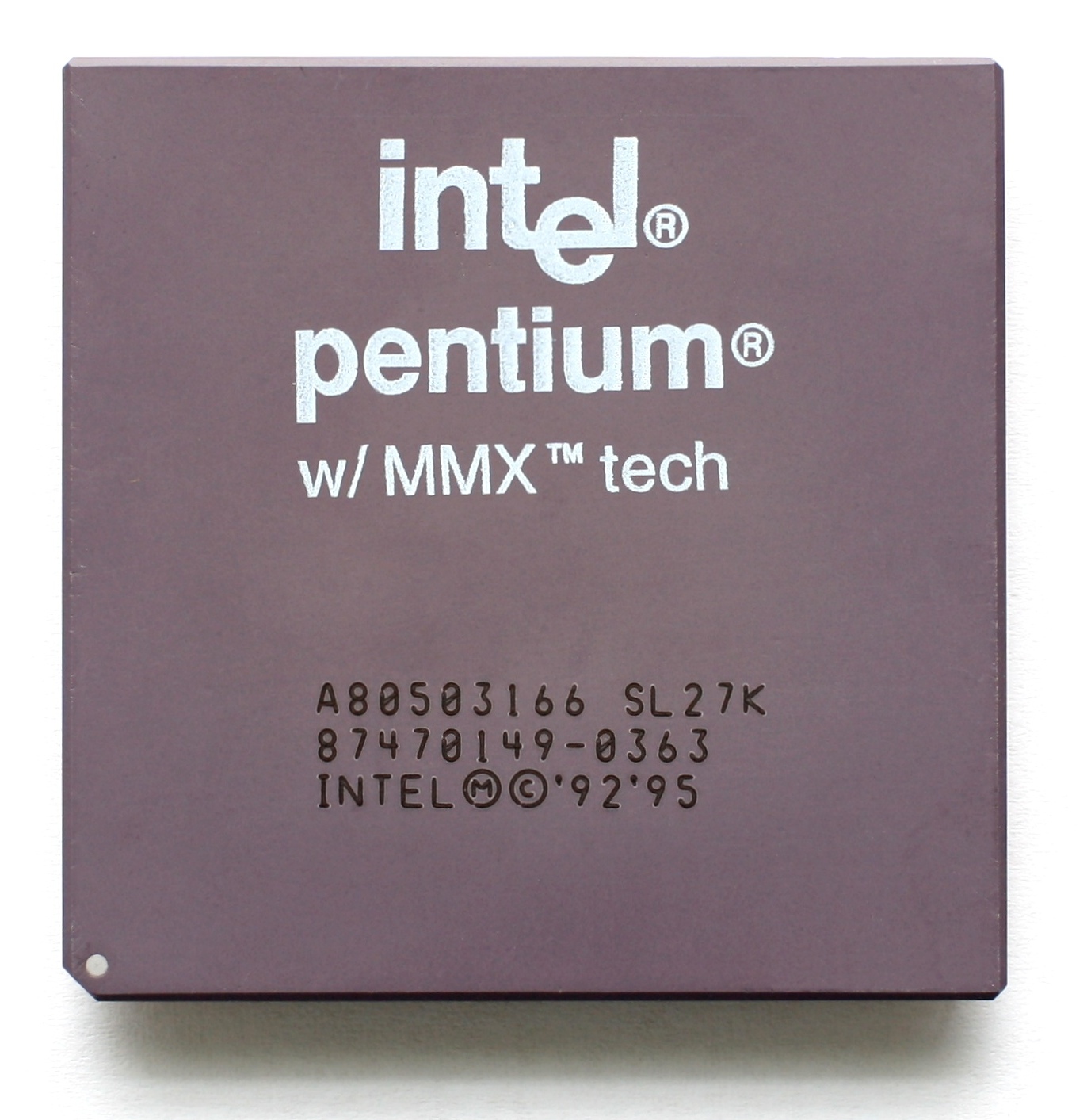

Pentium with MMX Technology

* P55C –

0.35 μm process technology

** Introduced January 8, 1997

** Intel

MMX (instruction set) support

**

Socket 7 296/321 pin PGA (pin grid array) package

** 16 KB L1 instruction cache

** 16 KB data cache

** 4.5 million transistors

** System bus clock rate 66 MHz

** Basic P55C is family 5 model 4, mobile are family 5 model 7 and 8

** Variants

*** 166, 200 MHz introduced January 8, 1997

*** 233 MHz introduced June 2, 1997

*** 133 MHz (Mobile)

*** 166, 266 MHz (Mobile) introduced January 12, 1998

*** 200, 233 MHz (Mobile) introduced September 8, 1997

*** 300 MHz (Mobile) introduced January 7, 1999

32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculation ...

processors:

P6/

Pentium M microarchitecture

Pentium Pro

* Introduced November 1, 1995

* Multichip Module (2 die)

* Precursor to Pentium II and III

* Primarily used in server systems

*

Socket 8 processor package (387 pins; Dual SPGA)

* 5.5 million transistors

* Family 6 model 1

*

0.6 μm process technology

** 16 KB L1 cache

** 256 KB integrated

L2 cache

** 60 MHz system bus clock rate

** Variants

*** 150 MHz

*

0.35 μm process technology, (two die, a 0.35 μm CPU with 0.6 μm L2 cache)

** 5.5 million transistors

** 512 KB or 256 KB integrated L2 cache

** 60 or 66 MHz system bus clock rate

** Variants

*** 150 MHz (60 MHz bus clock rate, 256 KB 0.5 μm cache) introduced November 1, 1995

*** 166 MHz (66 MHz bus clock rate, 512 KB 0.35 μm cache) introduced November 1, 1995

*** 180 MHz (60 MHz bus clock rate, 256 KB 0.6 μm cache) introduced November 1, 1995

*** 200 MHz (66 MHz bus clock rate, 256 KB 0.6 μm cache) introduced November 1, 1995

*** 200 MHz (66 MHz bus clock rate, 512 KB 0.35 μm cache) introduced November 1, 1995

*** 200 MHz (66 MHz bus clock rate, 1 MB 0.35 μm cache) introduced August 18, 1997

Pentium II

* Introduced May 7, 1997

* Pentium Pro with

MMX and improved

16-bit

16-bit microcomputers are microcomputers that use 16-bit microprocessors.

A 16-bit register can store 216 different values. The range of integer values that can be stored in 16 bits depends on the integer representation used. With the two mos ...

performance

* 242-pin

Slot 1 (SEC) processor package

* Voltage identification pins

* 7.5 million transistors

* 32 KB L1 cache

* 512 KB frequency external L2 cache

* The ''Performance Enhanced'' mobile Pentium II (codenamed Dixon) had a full-speed 256 KB L2 cache

* Klamath –

0.35 μm process technology (233, 266, 300 MHz)

** 66 MHz system bus clock rate

** Family 6 model 3

** Variants

*** 233, 266, 300 MHz introduced May 7, 1997

* Deschutes –

0.25 μm process technology (333, 350, 400, 450 MHz)

** Introduced January 26, 1998

** 66 MHz system bus clock rate (''333 MHz variant''), 100 MHz system bus clock rate for all subsequent models

** Family 6 model 5

** Variants

*** 333 MHz introduced January 26, 1998

*** 350, 400 MHz introduced April 15, 1998

*** 450 MHz introduced August 24, 1998

*** 233, 266 MHz (Mobile) introduced April 2, 1998

*** 333 MHz Pentium II Overdrive processor for Socket 8 Introduced August 10, 1998

*** 300 MHz (Mobile) introduced September 9, 1998

*** 333 MHz (Mobile) introduced January 25, 1999

Celeron (Pentium II-based)

* Covington –

0.25 μm process technology

** Introduced April 15, 1998

** 242-pin

Slot 1 SEPP (Single Edge Processor Package)

** 7.5 million transistors

** 66 MHz system bus clock rate

** Slot 1

** 32 KB L1 cache

** No L2 cache

** Variants

*** 266 MHz introduced April 15, 1998

*** 300 MHz introduced June 9, 1998

* Mendocino –

0.25 μm process technology

** Introduced August 24, 1998

** 242-pin

Slot 1 SEPP (Single Edge Processor Package),

Socket 370 PPGA package

** 19 million transistors

** 66 MHz system bus clock rate

** Slot 1, Socket 370

** 32 KB L1 cache

** 128 KB integrated cache

** Family 6 model 6

** Variants

*** 300, 333 MHz introduced August 24, 1998

*** 366, 400 MHz introduced January 4, 1999

*** 433 MHz introduced March 22, 1999

*** 466 MHz

*** 500 MHz introduced August 2, 1999

*** 533 MHz introduced January 4, 2000

*** 266 MHz (Mobile)

*** 300 MHz (Mobile)

*** 333 MHz (Mobile) introduced April 5, 1999

*** 366 MHz (Mobile)

*** 400 MHz (Mobile)

*** 433 MHz (Mobile)

*** 450 MHz (Mobile) introduced February 14, 2000

*** 466 MHz (Mobile)

*** 500 MHz (Mobile) introduced February 14, 2000

Pentium II Xeon ''(chronological entry)''

* Introduced June 29, 1998

Pentium III

* Katmai –

0.25 μm process technology

** Introduced February 26, 1999

** Improved PII (i.e. P6-based core) now including

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data (SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in their Pentium III series of Central processing units (CPUs) ...

(SSE)

** 9.5 million transistors

** 512 KB (512 × 1024 B) bandwidth L2 External cache

** 242-pin

Slot 1 SECC2 (Single Edge Contact cartridge 2) processor package

** System bus clock rate 100 MHz, 133 MHz (B-models)

** Slot 1

** Family 6 model 7

** Variants

*** 450, 500 MHz introduced February 26, 1999

*** 550 MHz introduced May 17, 1999

*** 600 MHz introduced August 2, 1999

*** 533, 600 MHz introduced (133 MHz bus clock rate) September 27, 1999

* Coppermine –

0.18 μm process technology

** Introduced October 25, 1999

** 28.1 million transistors

** 256 KB (512 × 1024 B) Advanced Transfer L2 cache (integrated)

** 242-pin Slot-1 SECC2 (Single Edge Contact cartridge 2) processor package, 370-pin

FC-PGA (flip-chip pin grid array) package

** System Bus clock rate 100 MHz (E-models), 133 MHz (EB models)

** Slot 1, Socket 370

** Family 6 model 8

** Variants

*** 500 MHz (100 MHz bus clock rate)

*** 533 MHz

*** 550 MHz (100 MHz bus clock rate)

*** 600 MHz

*** 600 MHz (100 MHz bus clock rate)

*** 650 MHz (100 MHz bus clock rate) introduced October 25, 1999

*** 667 MHz introduced October 25, 1999

*** 700 MHz (100 MHz bus clock rate) introduced October 25, 1999

*** 733 MHz introduced October 25, 1999

*** 750, 800 MHz (100 MHz bus clock rate) introduced December 20, 1999

*** 850 MHz (100 MHz bus clock rate) introduced March 20, 2000

*** 866 MHz introduced March 20, 2000

*** 933 MHz introduced May 24, 2000

*** 1000 MHz introduced March 8, 2000 (not widely available at time of release)

*** 1100 MHz

*** 1133 MHz (first version recalled, later re-released)

*** 400, 450, 500 MHz (Mobile) introduced October 25, 1999

*** 600, 650 MHz (Mobile) introduced January 18, 2000

*** 700 MHz (Mobile) introduced April 24, 2000

*** 750 MHz (Mobile) introduced June 19, 2000

*** 800, 850 MHz (Mobile) introduced September 25, 2000

*** 900, 1000 MHz (Mobile) introduced March 19, 2001

* Tualatin –

0.13 μm process technology

** Introduced July 2001

** 28.1 million transistors

** 32 KB (32 × 1024 B) L1 cache

** 256 KB or 512 KB Advanced Transfer L2 cache (integrated)

** 370-pin

FC-PGA2

A pin grid array (PGA) is a type of integrated circuit packaging. In a PGA, the package is square or rectangular, and the pins are arranged in a regular array on the underside of the package. The pins are commonly spaced 2.54 mm (0.1") a ...

(flip-chip pin grid array) package

** 133 MHz system bus clock rate

** Socket 370

** Family 6 model 11

** Variants

*** 1133 MHz (256 KB L2)

*** 1133 MHz (512 KB L2)

*** 1200 MHz

*** 1266 MHz (512 KB L2)

*** 1333 MHz

*** 1400 MHz (512 KB L2)

Pentium II Xeon and Pentium III Xeon

* PII Xeon

** Variants

*** 400 MHz introduced June 29, 1998

*** 450 MHz (512 KB L2 cache) introduced October 6, 1998

*** 450 MHz (1 MB and 2 MB L2 cache) introduced January 5, 1999

* PIII Xeon

** Introduced October 25, 1999

** 9.5 million transistors at 0.25 μm or 28 million at 0.18 μm

** L2 cache is 256 KB, 1 MB, or 2 MB Advanced Transfer Cache (Integrated)

** Processor Package Style is Single Edge Contact Cartridge (S.E.C.C.2) or SC330

** System Bus clock rate 133 MHz (256 KB L2 cache) or 100 MHz (1–2 MB L2 cache)

** System Bus width: 64 bits

** Addressable memory: 64 GB

** Used in two-way servers and workstations (256 KB L2) or 4- and 8-way servers (1–2 MB L2)

** Family 6 model 10

** Variants

*** 500 MHz (

0.25 μm process) introduced March 17, 1999

*** 550 MHz (0.25 μm process) introduced August 23, 1999

*** 600 MHz (

0.18 μm process, 256 KB L2 cache) introduced October 25, 1999

*** 667 MHz (0.18 μm process, 256 KB L2 cache) introduced October 25, 1999

*** 733 MHz (0.18 μm process, 256 KB L2 cache) introduced October 25, 1999

*** 800 MHz (0.18 μm process, 256 KB L2 cache) introduced January 12, 2000

*** 866 MHz (0.18 μm process, 256 KB L2 cache) introduced April 10, 2000

*** 933 MHz (0.18 μm process, 256 KB L2 cache)

*** 1000 MHz (0.18 μm process, 256 KB L2 cache) introduced August 22, 2000

*** 700 MHz (0.18 μm process, 1–2 MB L2 cache) introduced May 22, 2000

Celeron (Pentium III Coppermine-based)

* Coppermine-128, 0.18 μm process technology

** Introduced March, 2000

**

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data (SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in their Pentium III series of Central processing units (CPUs) ...

(SSE)

**

Socket 370,

FC-PGA processor package

** 28.1 million transistors

** 66 MHz system bus clock rate, 100 MHz system bus clock rate from January 3, 2001

** 32 KB L1 cache

** 128 KB Advanced Transfer L2 cache

** Family 6 model 8

** Variants

*** 533 MHz

*** 566 MHz

*** 600 MHz

*** 633, 667, 700 MHz introduced June 26, 2000

*** 733, 766 MHz introduced November 13, 2000

*** 800 MHz introduced January 3, 2001

*** 850 MHz introduced April 9, 2001

*** 900 MHz introduced July 2, 2001

*** 950, 1000, 1100 MHz introduced August 31, 2001

*** 550 MHz (Mobile)

*** 600, 650 MHz (Mobile) introduced June 19, 2000

*** 700 MHz (Mobile) introduced September 25, 2000

*** 750 MHz (Mobile) introduced March 19, 2001

*** 800 MHz (Mobile)

*** 850 MHz (Mobile) introduced July 2, 2001

*** 600 MHz (LV Mobile)

*** 500 MHz (ULV Mobile) introduced January 30, 2001

*** 600 MHz (ULV Mobile)

XScale ''(chronological entry – non-x86 architecture)''

* Introduced August 23, 2000

Pentium 4 (not 4EE, 4E, 4F), Itanium, P4-based Xeon, Itanium 2 ''(chronological entries)''

* Introduced April 2000 – July 2002

Pentium III Tualatin-based

* Tualatin –

0.13 μm process technology

** 32 KB L1 cache

** 512KB Advanced Transfer L2 cache

** 133 MHz system bus clock rate

** Socket 370

** Variants

*** 1.0 GHz

*** 1.13 GHz

*** 1.26 GHz

*** 1.4 GHz

Celeron (Pentium III Tualatin-based)

* Tualatin Celeron –

0.13 μm process technology

** 32 KB L1 cache

** 256 KB Advanced Transfer L2 cache

** 100 MHz system bus clock rate

** Socket 370

** Family 6 model 11

** Variants

*** 1.0 GHz

*** 1.1 GHz

*** 1.2 GHz

*** 1.3 GHz

*** 1.4 GHz

Pentium M

* Banias

0.13 μm process technology

** Introduced March 2003

** 64 KB L1 cache

** 1 MB L2 cache (integrated)

** Based on Pentium III core, with

SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier Streamin ...

SIMD instructions and deeper pipeline

** 77 million transistors

**

Micro-FCPGA,

Micro-FCBGA processor package

** Heart of the Intel mobile ''

Centrino'' system

** 400 MHz Netburst-style system bus

** Family 6 model 9

** Variants

*** 900 MHz (ultra-low voltage)

*** 1.0 GHz (ultra-low voltage)

*** 1.1 GHz (low voltage)

*** 1.2 GHz (low voltage)

*** 1.3 GHz

*** 1.4 GHz

*** 1.5 GHz

*** 1.6 GHz

*** 1.7 GHz

* Dothan 0.09 μm (

90 nm) process technology

** Introduced May 2004

** 2 MB L2 cache

** 140 million transistors

** Revised data prefetch unit

** 400 MHz Netburst-style system bus

** 21 W

TDP

** Family 6 model 13

** Variants

*** 1.00 GHz (Pentium M 723) (ultra-low voltage, 5 W TDP)

*** 1.10 GHz (Pentium M 733) (ultra-low voltage, 5 W TDP)

*** 1.20 GHz (Pentium M 753) (ultra-low voltage, 5 W TDP)

*** 1.30 GHz (Pentium M 718) (low voltage, 10 W TDP)

*** 1.40 GHz (Pentium M 738) (low voltage, 10 W TDP)

*** 1.50 GHz (Pentium M 758) (low voltage, 10 W TDP)

*** 1.60 GHz (Pentium M 778) (low voltage, 10 W TDP)

*** 1.40 GHz (Pentium M 710)

*** 1.50 GHz (Pentium M 715)

*** 1.60 GHz (Pentium M 725)

*** 1.70 GHz (Pentium M 735)

*** 1.80 GHz (Pentium M 745)

*** 2.00 GHz (Pentium M 755)

*** 2.10 GHz (Pentium M 765)

* Dothan 533 0.09 μm (

90 nm) process technology

** Introduced Q1 2005

** Same as Dothan except with a 533 MHz NetBurst-style system bus and 27 W

TDP

** Variants

*** 1.60 GHz (Pentium M 730)

*** 1.73 GHz (Pentium M 740)

*** 1.86 GHz (Pentium M 750)

*** 2.00 GHz (Pentium M 760)

*** 2.13 GHz (Pentium M 770)

*** 2.26 GHz (Pentium M 780)

* Stealey 0.09 μm (

90 nm) process technology

** Introduced Q2 2007

** 512 KB L2, 3 W TDP

** Variants

*** 600 MHz (A100)

*** 800 MHz (A110)

Celeron M

* Banias-512

0.13 μm process technology

** Introduced March 2003

** 64 KB L1 cache

** 512 KB L2 cache (integrated)

**

SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier Streamin ...

SIMD instructions

** No

SpeedStep technology, is not part of the '

Centrino' package

** Family 6 model 9

** Variants

*** 310, 1.20 GHz

*** 320, 1.30 GHz

*** 330, 1.40 GHz

*** 340, 1.50 GHz

* Dothan-1024

90 nm process technology

** 64 KB L1 cache

** 1 MB L2 cache (integrated)

**

SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier Streamin ...

SIMD instructions

** No

SpeedStep technology, is not part of the '

Centrino' package

** Variants

*** 350, 1.30 GHz

*** 350J, 1.30 GHz, with Execute Disable bit

*** 360, 1.40 GHz

*** 360J, 1.40 GHz, with Execute Disable bit

*** 370, 1.50 GHz, with Execute Disable bit

**** Family 6, Model 13, Stepping 8

*** 380, 1.60 GHz, with Execute Disable bit

*** 390, 1.70 GHz, with Execute Disable bit

*

Yonah-1024

65 nm process technology

** 64 KB L1 cache

** 1 MB L2 cache (integrated)

**

SSE3 SIMD instructions, 533 MHz front-side bus, execute-disable bit

** No

SpeedStep technology, is not part of the '

Centrino' package

** Variants

*** 410, 1.46 GHz

*** 420, 1.60 GHz,

*** 423, 1.06 GHz (ultra-low voltage)

*** 430, 1.73 GHz

*** 440, 1.86 GHz

*** 443, 1.20 GHz (ultra-low voltage)

*** 450, 2.00 GHz

Intel Core

*

Yonah 0.065 μm (

65 nm) process technology

** Introduced January 2006

** 533/667 MHz

front-side bus

** 2 MB (Shared on Duo) L2 cache

**

SSE3 SIMD instructions

** 31W

TDP (T versions)

** Family 6, Model 14

** Variants:

*** Intel Core Duo T2700 2.33 GHz

*** Intel Core Duo T2600 2.16 GHz

*** Intel Core Duo T2500 2 GHz

*** Intel Core Duo T2450 2 GHz

*** Intel Core Duo T2400 1.83 GHz

*** Intel Core Duo T2300 1.66 GHz

*** Intel Core Duo T2050 1.6 GHz

*** Intel Core Duo T2300e 1.66 GHz

*** Intel Core Duo T2080 1.73 GHz

*** Intel Core Duo L2500 1.83 GHz (low voltage, 15 W

TDP)

*** Intel Core Duo L2400 1.66 GHz (low voltage, 15 W TDP)

*** Intel Core Duo L2300 1.5 GHz (low voltage, 15 W TDP)

*** Intel Core Duo U2500 1.2 GHz (ultra-low voltage, 9 W TDP)

*** Intel Core Solo T1350 1.86 GHz (533 FSB)

*** Intel Core Solo T1300 1.66 GHz

*** Intel Core Solo T1200 1.5 GHz

Dual-Core Xeon LV

*

Sossaman 0.065 μm (

65 nm) process technology

** Introduced March 2006

** Based on Yonah core, with

SSE3 SIMD instructions

** 667 MHz

frontside bus

A front-side bus (FSB) is a computer communication interface ( bus) that was often used in Intel-chip-based computers during the 1990s and 2000s. The EV6 bus served the same function for competing AMD CPUs. Both typically carry data between the ...

** 2 MB shared L2 cache

** Variants

*** 2.0 GHz

32-bit processors: NetBurst microarchitecture

Pentium 4

* 0.18 μm process technology (1.40 and 1.50 GHz)

** Introduced November 20, 2000

** L2 cache was 256 KB Advanced Transfer cache (integrated)

** Processor package Style was PGA423, PGA478

** System bus clock rate 400 MHz

**

SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier Streamin ...

SIMD Extensions

** 42 million transistors

** Used in desktops and entry-level workstations

* 0.18 μm process technology (1.7 GHz)

** Introduced April 23, 2001

** See the 1.4 and 1.5 chips for details

* 0.18 μm process technology (1.6 and 1.8 GHz)

** Introduced July 2, 2001

** See 1.4 and 1.5 chips for details

** Core voltage is 1.15 volts in Maximum Performance Mode; 1.05 volts in battery optimized mode

** Power <1 watt in battery optimized mode

** Used in full-size and then light mobile PCs

* 0.18 μm process technology Willamette (1.9 and 2.0 GHz)

** Introduced August 27, 2001

** See 1.4 and 1.5 chips for details

* Family 15 model 1

* Pentium 4 (2 GHz, 2.20 GHz)

** Introduced January 7, 2002

* Pentium 4 (2.4 GHz)

** Introduced April 2, 2002

* 0.13 μm process technology Northwood A (1.7, 1.8, 1.9, 2, 2.2, 2.4, 2.5, 2.6, 2.8 (OEM), 3.0 (OEM) GHz)

** Improved branch prediction and other microcodes tweaks

** 512 KB integrated L2 cache

** 55 million transistors

** 400 MHz system bus

* Family 15 model 2

* 0.13 μm process technology Northwood B (2.26, 2.4, 2.53, 2.66, 2.8, 3.06 GHz)

** 533 MHz system bus. (3.06 includes Intel's

Hyper-Threading technology)

* 0.13 μm process technology Northwood C (2.4, 2.6, 2.8, 3.0, 3.2, 3.4 GHz)

** 800 MHz system bus (all versions include Hyper-Threading)

** 6500 to 10,000 MIPS

Itanium ''(chronological entry – new non-x86 architecture)''

* Introduced 2001

Xeon (32-bit NetBurst)

* Official designation now Xeon; i.e. not "Pentium 4 Xeon"

* Xeon 1.4, 1.5, 1.7 GHz

** Introduced May 21, 2001

** L2 cache was 256 KB Advanced Transfer cache (integrated)

** Processor package

Organic Land Grid Array

Organic may refer to:

* Organic, of or relating to an organism, a living entity

* Organic, of or relating to an anatomical organ

Chemistry

* Organic matter, matter that has come from a once-living organism, is capable of decay or is the product o ...

603 (OLGA 603)

** System bus clock rate 400 MHz

** SSE2 SIMD Extensions

** Used in high-performance and mid-range dual processor enabled workstations

* Xeon 2.0 GHz and up to 3.6 GHz

** Introduced September 25, 2001

Itanium 2 ''(chronological entry – new non-x86 architecture)''

* Introduced July 2002

* ''See

main entry''

Mobile Pentium 4-M

* 0.13 μm process technology

* 55 million transistors

* 512 KB L2 cache

* BUS a 400 MHz

* Supports up to 1 GB of

DDR 266 MHz memory

* Supports

ACPI 2.0 and

APM APM, apm, or Apm may refer to:

Technology Computer technology

* Active policy management, a discipline within enterprise software

*Advanced Power Management, a legacy technology in personal computers

* Apple Partition Map, computer disk partit ...

1.2 System Power Management

* 1.3–1.2 V (

SpeedStep)

* Power: 1.2 GHz 20.8 W, 1.6 GHz 30 W, 2.6 GHz 35 W

* Sleep power 5 W (1.2 V)

* Deeper sleep power 2.9 W (1.0 V)

** 1.40 GHz – 23 April 2002

** 1.50 GHz – 23 April 2002

** 1.60 GHz – 4 March 2002

** 1.70 GHz – 4 March 2002

** 1.80 GHz – 23 April 2002

** 1.90 GHz – 24 June 2002

** 2.00 GHz – 24 June 2002

** 2.20 GHz – 16 September 2002

** 2.40 GHz – 14 January 2003

** 2.50 GHz – 16 April 2003

** 2.60 GHz – 11 June 2003

Pentium 4 EE

* Introduced September 2003

* "Extreme Edition"

* Built from the Xeon's "Gallatin" core, but with 2 MB cache

Pentium 4E

* Introduced February 2004

* Built on 0.09 μm (

90 nm) process technology Prescott (2.4 A, 2.8, 2.8 A, 3.0, 3.2, 3.4, 3.6, 3.8 ) 1 MB L2 cache

* 533 MHz system bus (2.4A and 2.8A only)

* 800 MHz system bus (all other models)

* 125 million transistors in 1 MB models

* 169 million transistors in 2 MB models

*

Hyper-Threading support is only available on CPUs using the 800 MHz system bus.

* The processor's integer

instruction pipeline has been increased from 20 stages to 31 stages, which theoretically allows for even greater bandwidth

* 7500 to 11,000 MIPS

*

LGA 775 versions are in the 5xx series (32-bit) and 5''x''1 series (with Intel 64)

* The 6xx series has 2 MB L2 cache and

Intel 64

64-bit processors: IA-64

* New instruction set, not at all related to x86

* Before the feature was eliminated (

Montecito, July 2006) IA-64 processors supported 32-bit x86 in hardware, but

slowly (see its 2001

market reception and 2006

architectural changes)

Itanium

* Code name Merced

* Family 7

* Released May 29, 2001

* 733 MHz and 800 MHz

* 2 MB cache

* All recalled and replaced by Itanium 2

Itanium 2

Itanium ( ) is a discontinued family of 64-bit Intel microprocessors that implement the Intel Itanium architecture (formerly called IA-64). Launched in June 2001, Intel marketed the processors for enterprise servers and high-performance computin ...

* Family 0x1F

* Released July 2002

* 900 MHz – 1.6 GHz

* McKinley 900 MHz 1.5 MB cache, Model 0x0

* McKinley 1 GHz, 3 MB cache, Model 0x0

* Deerfield 1 GHz, 1.5 MB cache, Model 0x1

* Madison 1.3 GHz, 3 MB cache, Model 0x1

* Madison 1.4 GHz, 4 MB cache, Model 0x1

* Madison 1.5 GHz, 6 MB cache, Model 0x1

* Madison 1.67 GHz, 9 MB cache, Model 0x1

* Hondo 1.4 GHz, 4 MB cache,

dual-core MCM, Model 0x1

64-bit processors: Intel 64 – NetBurst microarchitecture

* Intel Extended Memory 64 Technology

* Mostly compatible with

AMD's

AMD64 architecture

* Introduced Spring 2004, with the Pentium 4F (D0 and later P4 steppings)

Pentium 4F

* Prescott-2M built on 0.09 μm (

90 nm) process technology

* 2.8–3.8 GHz (model numbers 6''x''0)

* Introduced February 20, 2005

* Same features as Prescott with the addition of:

** 2 MB cache

** Intel

64-bit

** Enhanced Intel

SpeedStep Technology (EIST)

* Cedar Mill built on 0.065 μm (

65 nm) process technology

* 3.0–3.6 GHz (model numbers 6''x''1)

* Introduced January 16, 2006

* Die shrink of Prescott-2M

* Same features as Prescott-2M

* Family 15 Model 4

Pentium D

*

Dual-core microprocessor

* No Hyper-Threading

* 800 (4×200) MHz

front-side bus

*

LGA 775 (Socket T)

* Smithfield (Pentium D) –

90 nm process technology (2.66–3.2 GHz)

** Introduced May 26, 2005

** 2.66–3.2 GHz (model numbers 805–840)

** 230 million transistors

** 1 MB × 2 (non-shared, 2 MB total) L2 cache

** Cache coherency between cores requires communication over the FSB

** Performance increase of 60% over similarly clocked Prescott

** 2.66 GHz (533 MHz FSB) Pentium D 805 introduced December 2005

** Contains 2× Prescott dies in one package

** Family 15 Model 4

*

Presler

Pentium D is a range of desktop 64-bit x86-64 processors based on the NetBurst microarchitecture, which is the dual-core variant of the Pentium 4 manufactured by Intel. Each CPU comprised two dies, each containing a single core, residing next to e ...

(Pentium D) –

65 nm process technology (2.8–3.6 GHz)

** Introduced January 16, 2006

** 2.8–3.6 GHz (model numbers 915–960)

** 376 million transistors

** 2× 2 MB (non-shared, 4 MB total) L2 cache

** Contains 2× Cedar Mill dies in one package

** Variants

*** Pentium D 945

Pentium Extreme Edition

* Dual-core microprocessor

* Enabled Hyper-Threading

* 800 (4×200) MHz

front-side bus

* Smithfield (Pentium Extreme Edition) –

90 nm process technology (3.2 GHz)

** Variants

*** Pentium 840 EE – 3.20 GHz (2 × 1 MB L2)

* Presler (Pentium Extreme Edition) –

65 nm process technology (3.46, 3.73)

** 2 MB × 2 (non-shared, 4 MB total) L2 cache

** Variants

*** Pentium 955 EE – 3.46 GHz, 1066 MHz

front-side bus

*** Pentium 965 EE – 3.73 GHz, 1066 MHz

front-side bus

*** Pentium 969 EE – 3.73 GHz, 1066 MHz

front-side bus

Xeon (64-bit NetBurst)

* Nocona

** Introduced 2004

* Irwindale

** Introduced 2004

* Cranford

** Introduced April 2005

** MP version of Nocona

* Potomac

** Introduced April 2005

** Cranford with 8 MB of L3 cache

* Paxville DP (2.8 GHz)

** Introduced October 10, 2005

** Dual-core version of Irwindale, with 4 MB of L2 cache (2 MB per core)

** 2.8 GHz

** 800 MT/s front-side bus

* Paxville MP – 90 nm process (2.67 – 3.0 GHz)

** Introduced November 1, 2005

** Dual-core Xeon 7000 series

** MP-capable version of Paxville DP

** 2 MB of L2 cache (1 MB per core) or 4 MB of L2 (2 MB per core)

** 667 MT/s FSB or 800 MT/s FSB

* Dempsey – 65 nm process (2.67–3.73 GHz)

** Introduced May 23, 2006

** Dual-core Xeon 5000 series

** MP version of Presler

** 667 MT/s or 1066 MT/s FSB

** 4 MB of L2 cache (2 MB per core)

**

LGA 771 (Socket J).

* Tulsa – 65 nm process (2.5–3.4 GHz)

** Introduced August 29, 2006

** Dual-core Xeon 7100-series

** Improved version of Paxville MP

** 667 MT/s or 800 MT/s FSB

64-bit processors: Intel 64 – Core microarchitecture

Xeon (64-bit Core microarchitecture)

*

Woodcrest –

65 nm process technology

** Server and Workstation CPU (SMP support for dual CPU system)

** Introduced June 26, 2006

**

Intel VT-x, multiple

OS support

** EIST (Enhanced Intel

SpeedStep Technology) in 5140, 5148LV, 5150, 5160

**

Execute Disable Bit

**

TXT, enhanced security hardware extensions

**

SSSE3 SIMD instructions

** iAMT2 (Intel Active Management Technology), remotely manage computers

** Variants

*** Xeon 5160, 3.00 GHz (4 MB L2, 1333 MHz FSB, 80 W)

*** Xeon 5150, 2.66 GHz (4 MB L2, 1333 MHz FSB, 65 W)

*** Xeon 5140, 2.33 GHz (4 MB L2, 1333 MHz FSB, 65 W)

*** Xeon 5130, 2.00 GHz (4 MB L2, 1333 MHz FSB, 65 W)

*** Xeon 5120, 1.86 GHz (4 MB L2, 1066 MHz FSB, 65 W)

*** Xeon 5110, 1.60 GHz (4 MB L2, 1066 MHz FSB, 65 W)

*** Xeon 5148LV, 2.33 GHz (4 MB L2, 1333 MHz FSB, 40 W) (low voltage edition)

*

Clovertown –

65 nm process technology

** Server and Workstation CPU (SMP support for dual CPU system)

** Introduced December 13, 2006

**

Quad-core

**

Intel VT-x, multiple

OS support

** EIST (Enhanced Intel

SpeedStep Technology) in E5365, L5335

**

Execute Disable Bit

**

TXT, enhanced security hardware extensions

**

SSSE3 SIMD instructions

** iAMT2 (Intel Active Management Technology), remotely manage computers

** Variants

*** Xeon X5355, 2.66 GHz (2×4 MB L2, 1333 MHz FSB, 105 W)

*** Xeon E5345, 2.33 GHz (2×4 MB L2, 1333 MHz FSB, 80 W)

*** Xeon E5335, 2.00 GHz (2×4 MB L2, 1333 MHz FSB, 80 W)

*** Xeon E5320, 1.86 GHz (2×4 MB L2, 1066 MHz FSB, 65 W)

*** Xeon E5310, 1.60 GHz (2×4 MB L2, 1066 MHz FSB, 65 W)

*** Xeon L5320, 1.86 GHz (2×4 MB L2, 1066 MHz FSB, 50 W) (low voltage edition)

Intel Core 2

*

Conroe –

65 nm process technology

** Desktop CPU (SMP support restricted to 2 CPUs)

** Two cores on one die

** Introduced July 27, 2006

**

SSSE3 SIMD instructions

** 291 million transistors

** 64 KB of L1 cache per core (32+32 KB 8-way)

**

Intel VT-x, multiple

OS support

**

TXT, enhanced security hardware extensions

**

Execute Disable Bit

** EIST (Enhanced Intel

SpeedStep Technology)

** iAMT2 (Intel Active Management Technology), remotely manage computers

**

Intel Management Engine introduced

**

LGA 775

** Variants

*** Core 2 Duo E6850, 3.00 GHz (4 MB L2, 1333 MHz FSB)

*** Core 2 Duo E6800, 2.93 GHz (4 MB L2, 1066 MHz FSB)

*** Core 2 Duo E6750, 2.67 GHz (4 MB L2, 1333 MHz FSB, 65 W)

*** Core 2 Duo E6700, 2.67 GHz (4 MB L2, 1066 MHz FSB)

*** Core 2 Duo E6600, 2.40 GHz (4 MB L2, 1066 MHz FSB, 65 W)

*** Core 2 Duo E6550, 2.33 GHz (4 MB L2, 1333 MHz FSB)

*** Core 2 Duo E6420, 2.13 GHz (4 MB L2, 1066 MHz FSB)

*** Core 2 Duo E6400, 2.13 GHz (2 MB L2, 1066 MHz FSB)

*** Core 2 Duo E6320, 1.86 GHz (4 MB L2, 1066 MHz FSB) Family 6, Model 15, Stepping 6

*** Core 2 Duo E6300, 1.86 GHz (2 MB L2, 1066 MHz FSB)

*

Conroe XE –

65 nm process technology

** Desktop Extreme Edition CPU (SMP support restricted to 2 CPUs)

** Introduced July 27, 2006

** Same features as Conroe

**

LGA 775

** Variants

*** Core 2 Extreme X6800 – 2.93 GHz (4 MB L2, 1066 MHz FSB)

*

Allendale (Intel Core 2) –

65 nm process technology

** Desktop CPU (SMP support restricted to 2 CPUs)

** Two CPUs on one die

** Introduced January 21, 2007

**

SSSE3 SIMD instructions

** 167 million transistors

**

TXT, enhanced security hardware extensions

**

Execute Disable Bit

** EIST (Enhanced Intel

SpeedStep Technology)

** iAMT2 (Intel Active Management Technology), remotely manage computers

**

LGA 775

** Variants

*** Core 2 Duo E4700, 2.60 GHz (2 MB L2, 800 MHz FSB)

*** Core 2 Duo E4600, 2.40 GHz (2 MB L2, 800 MHz FSB)

*** Core 2 Duo E4500, 2.20 GHz (2 MB L2, 800 MHz FSB)

*** Core 2 Duo E4400, 2.00 GHz (2 MB L2, 800 MHz FSB)

*** Core 2 Duo E4300, 1.80 GHz (2 MB L2, 800 MHz FSB) Family 6, Model 15, Stepping 2

*

Merom –

65 nm process technology

** Mobile CPU (SMP support restricted to 2 CPUs)

** Introduced July 27, 2006

** Family 6, Model 15

** Same features as Conroe

**

Socket M /

Socket P

** Variants

*** Core 2 Duo T7800, 2.60 GHz (4 MB L2, 800 MHz FSB) (

Santa Rosa platform)

*** Core 2 Duo T7700, 2.40 GHz (4 MB L2, 800 MHz FSB)

*** Core 2 Duo T7600, 2.33 GHz (4 MB L2, 667 MHz FSB)

*** Core 2 Duo T7500, 2.20 GHz (4 MB L2, 800 MHz FSB)

*** Core 2 Duo T7400, 2.16 GHz (4 MB L2, 667 MHz FSB)

*** Core 2 Duo T7300, 2.00 GHz (4 MB L2, 800 MHz FSB)

*** Core 2 Duo T7250, 2.00 GHz (2 MB L2, 800 MHz FSB)

*** Core 2 Duo T7200, 2.00 GHz (4 MB L2, 667 MHz FSB)

*** Core 2 Duo T7100, 1.80 GHz (2 MB L2, 800 MHz FSB)

*** Core 2 Duo T5600, 1.83 GHz (2 MB L2, 667 MHz FSB) Family 6, Model 15, Stepping 6

*** Core 2 Duo T5550, 1.83 GHz (2 MB L2, 667 MHz FSB, no VT)

*** Core 2 Duo T5500, 1.66 GHz (2 MB L2, 667 MHz FSB, no VT)

*** Core 2 Duo T5470, 1.60 GHz (2 MB L2, 800 MHz FSB, no VT) Family 6, Model 15, Stepping 13

*** Core 2 Duo T5450, 1.66 GHz (2 MB L2, 667 MHz FSB, no VT)

*** Core 2 Duo T5300, 1.73 GHz (2 MB L2, 533 MHz FSB, no VT)

*** Core 2 Duo T5270, 1.40 GHz (2 MB L2, 800 MHz FSB, no VT)

*** Core 2 Duo T5250, 1.50 GHz (2 MB L2, 667 MHz FSB, no VT)

*** Core 2 Duo T5200, 1.60 GHz (2 MB L2, 533 MHz FSB, no VT)

*** Core 2 Duo L7500, 1.60 GHz (4 MB L2, 800 MHz FSB) (low voltage)

*** Core 2 Duo L7400, 1.50 GHz (4 MB L2, 667 MHz FSB) (low voltage)

*** Core 2 Duo L7300, 1.40 GHz (4 MB L2, 800 MHz FSB) (low voltage)

*** Core 2 Duo L7200, 1.33 GHz (4 MB L2, 667 MHz FSB) (low voltage)

*** Core 2 Duo U7700, 1.33 GHz (2 MB L2, 533 MHz FSB) (ultra low voltage)

*** Core 2 Duo U7600, 1.20 GHz (2 MB L2, 533 MHz FSB) (ultra low voltage)

*** Core 2 Duo U7500, 1.06 GHz (2 MB L2, 533 MHz FSB) (ultra low voltage)

*

Kentsfield –

65 nm process technology

** Two dual-core CPU dies in one package

** Desktop CPU quad-core (SMP support restricted to 4 CPUs)

** Introduced December 13, 2006

** Same features as Conroe but with 4 CPU cores

** 586 million transistors

**

LGA 775

** Family 6, Model 15, Stepping 11

** Variants

*** Core 2 Extreme QX6850, 3 GHz (2×4 MB L2 cache, 1333 MHz FSB)

*** Core 2 Extreme QX6800, 2.93 GHz (2×4 MB L2 cache, 1066 MHz FSB) (April 9, 2007)

*** Core 2 Extreme QX6700, 2.66 GHz (2×4 MB L2 cache, 1066 MHz FSB) (November 14, 2006)

*** Core 2 Quad Q6700, 2.66 GHz (2×4 MB L2 cache, 1066 MHz FSB) (July 22, 2007)

*** Core 2 Quad Q6600, 2.40 GHz (2×4 MB L2 cache, 1066 MHz FSB) (January 7, 2007)

*

Wolfdale –

45 nm

Per the International Technology Roadmap for Semiconductors, the 45 nm process is a MOSFET technology node referring to the average half-pitch of a memory cell manufactured at around the 2007–2008 time frame.

Matsushita and Intel started mass ...

process technology

** Die shrink of Conroe

** Same features as Conroe with the addition of:

*** 50% more cache, 6 MB as opposed to 4 MB

*** Intel Trusted Execution Technology

***

SSE4

SSE4 (Streaming SIMD Extensions 4) is a SIMD CPU instruction set used in the Intel Core microarchitecture and AMD K10 (K8L). It was announced on September 27, 2006, at the Fall 2006 Intel Developer Forum, with vague details in a white paper; more ...

SIMD instructions

** 410 million transistors

** Variants

*** Core 2 Duo E8600, 3.33 GHz (6 MB L2, 1333 MHz FSB)

*** Core 2 Duo E8500, 3.16 GHz (6 MB L2, 1333 MHz FSB)

*** Core 2 Duo E8435, 3.07 GHz (6 MB L2, 1066 MHz FSB)

*** Core 2 Duo E8400, 3.00 GHz (6 MB L2, 1333 MHz FSB)

*** Core 2 Duo E8335, 2.93 GHz (6 MB L2, 1066 MHz FSB)

*** Core 2 Duo E8300, 2.83 GHz (6 MB L2, 1333 MHz FSB)

*** Core 2 Duo E8235, 2.80 GHz (6 MB L2, 1066 MHz FSB)

*** Core 2 Duo E8200, 2.66 GHz (6 MB L2, 1333 MHz FSB)

*** Core 2 Duo E8135, 2.66 GHz (6 MB L2, 1066 MHz FSB)

*** Core 2 Duo E8190, 2.66 GHz (6 MB L2, 1333 MHz FSB, no TXT, no VT)

*

Wolfdale-3M (Intel Core 2) –

45 nm

Per the International Technology Roadmap for Semiconductors, the 45 nm process is a MOSFET technology node referring to the average half-pitch of a memory cell manufactured at around the 2007–2008 time frame.

Matsushita and Intel started mass ...

process technology

** Intel Trusted Execution Technology

** Variants

*** Core 2 Duo E7600, 3.06 GHz (3 MB L2, 1066 MHz FSB)

*** Core 2 Duo E7500, 2.93 GHz (3 MB L2, 1066 MHz FSB)

*** Core 2 Duo E7400, 2.80 GHz (3 MB L2, 1066 MHz FSB)

*** Core 2 Duo E7300, 2.66 GHz (3 MB L2, 1066 MHz FSB)

*** Core 2 Duo E7200, 2.53 GHz (3 MB L2, 1066 MHz FSB)

*

Yorkfield

Yorkfield is the code name for some Intel processors sold as Core 2 Quad and Xeon.

In Intel's Tick-Tock cycle, the 2007/2008 "Tick" was Penryn microarchitecture, the shrink of the Core microarchitecture to 45 nanometers as CPUID model 23, repla ...

,

45 nm

Per the International Technology Roadmap for Semiconductors, the 45 nm process is a MOSFET technology node referring to the average half-pitch of a memory cell manufactured at around the 2007–2008 time frame.

Matsushita and Intel started mass ...

process technology

** Quad-core CPU

** Die shrink of Kentsfield

** Contains 2× Wolfdale dual-core dies in one package

** Same features as Wolfdale

** 820 million transistors

** Variants

*** Core 2 Extreme QX9770, 3.20 GHz (2×6 MB L2, 1600 MHz FSB)

*** Core 2 Extreme QX9650, 3.00 GHz (2×6 MB L2, 1333 MHz FSB)

*** Core 2 Quad Q9705, 3.16 GHz (2×3 MB L2, 1333 MHz FSB)

*** Core 2 Quad Q9700, 3.16 GHz (2×3 MB L2, 1333 MHz FSB)

*** Core 2 Quad Q9650, 3 GHz (2×6 MB L2, 1333 MHz FSB)

*** Core 2 Quad Q9550, 2.83 GHz (2×6 MB L2, 1333 MHz FSB, 95 W TDP)

*** Core 2 Quad Q9550s, 2.83 GHz (2×6 MB L2, 1333 MHz FSB, 65 W TDP)

*** Core 2 Quad Q9450, 2.66 GHz (2×6 MB L2, 1333 MHz FSB, 95 W TDP)

*** Core 2 Quad Q9505, 2.83 GHz (2×3 MB L2, 1333 MHz FSB, 95 W TDP)

*** Core 2 Quad Q9505s, 2.83 GHz (2×3 MB L2, 1333 MHz FSB, 65 W TDP)

*** Core 2 Quad Q9500, 2.83 GHz (2×3 MB L2, 1333 MHz FSB, 95 W TDP, no TXT)

*** Core 2 Quad Q9400, 2.66 GHz (2×3 MB L2, 1333 MHz FSB, 95 W TDP)

*** Core 2 Quad Q9400s, 2.66 GHz (2×3 MB L2, 1333 MHz FSB, 65 W TDP)

*** Core 2 Quad Q9300, 2.50 GHz (2×3 MB L2, 1333 MHz FSB, 95 W TDP)

*** Core 2 Quad Q8400, 2.66 GHz (2×2 MB L2, 1333 MHz FSB, 95 W TDP)

*** Core 2 Quad Q8400s, 2.66 GHz (2×2 MB L2, 1333 MHz FSB, 65 W TDP)

*** Core 2 Quad Q8300, 2.50 GHz (2×2 MB L2, 1333 MHz FSB, 95 W TDP)

*** Core 2 Quad Q8300s, 2.50 GHz (2×2 MB L2, 1333 MHz FSB, 65 W TDP)

*** Core 2 Quad Q8200, 2.33 GHz (2×2 MB L2, 1333 MHz FSB, 95 W TDP)

*** Core 2 Quad Q8200s, 2.33 GHz (2×2 MB L2, 1333 MHz FSB, 65 W TDP)

*** Core 2 Quad Q7600, 2.70 GHz (2×1 MB L2, 800 MHz FSB, no SSE4) (no Q7600 liste

here

* Intel Core2 Quad Mobile processor family –

45 nm

Per the International Technology Roadmap for Semiconductors, the 45 nm process is a MOSFET technology node referring to the average half-pitch of a memory cell manufactured at around the 2007–2008 time frame.

Matsushita and Intel started mass ...

process technology

** Quad-core CPU

** Variants

*** Core 2 Quad Q9100, 2.26 GHz (2×6 MB L2, 1066 MHz FSB, 45 W TDP)

*** Core 2 Quad Q9000, 2.00 GHz (2×3 MB L2, 1066 MHz FSB, 45 W TDP)

Pentium Dual-Core

*