|

SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revision of their Pentium 4 CPU. In April 2005, AMD introduced a subset of SSE3 in revision E (Venice and San Diego) of their Athlon 64 CPUs. The earlier SIMD instruction sets on the x86 platform, from oldest to newest, are MMX, 3DNow! (developed by AMD, but not supported by Intel processors), SSE, and SSE2. SSE3 contains 13 new instructions over SSE2. Changes The most notable change is the capability to work horizontally in a register, as opposed to the more or less strictly vertical operation of all previous SSE instructions. More specifically, instructions to add and subtract the multiple values stored within a single register have been added. These instructions can be used to speed up the implementation of a number of DSP and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD 10h

The AMD Family 10h, or K10, is a microprocessor microarchitecture by AMD based on the K8 microarchitecture. Though there were once reports that the K10 had been canceled,AMD's K10 is delayed or dead The Inquirer the first third-generation Opteron products for servers were launched on September 10, 2007, with the Phenom processors for desktops following and launching on November 11, 2007 as the immediate successors to the K8 series of processors ( |

Athlon 64

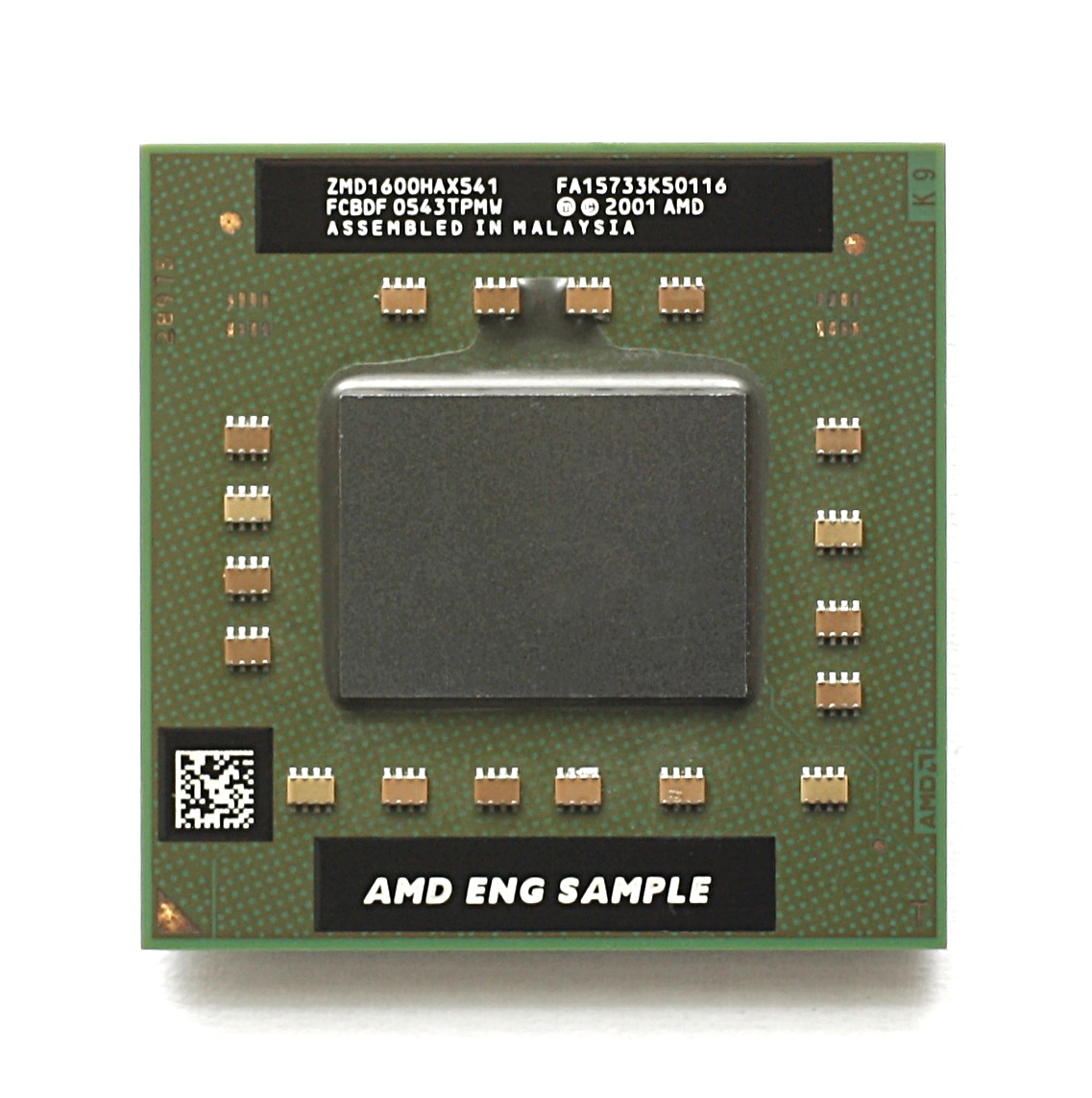

The Athlon 64 is a ninth-generation, AMD64-architecture microprocessor produced by Advanced Micro Devices (AMD), released on September 23, 2003. It is the third processor to bear the name '' Athlon'', and the immediate successor to the Athlon XP. The second processor (after the Opteron) to implement the AMD64 architecture and the first 64-bit processor targeted at the average consumer, it was AMD's primary consumer CPU, and primarily competed with Intel's Pentium 4, especially the ''Prescott'' and ''Cedar Mill'' core revisions. It is AMD's first K8, eighth-generation processor core for desktop and mobile computers. Despite being natively 64-bit, the AMD64 architecture is backward-compatible with 32-bit x86 instructions. Athlon 64s have been produced for Socket 754, Socket 939, Socket 940, and Socket AM2. The line was succeeded by the dual-core Athlon 64 X2 and Athlon X2 lines. Background The Athlon 64 was originally codenamed ''ClawHammer'' by AMD, and was referred ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data (SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in their Pentium III series of Central processing units (CPUs) shortly after the appearance of Advanced Micro Devices (AMD's) 3DNow!. SSE contains 70 new instructions (65 unique mnemonics using 70 encodings), most of which work on single precision floating-point data. SIMD instructions can greatly increase performance when exactly the same operations are to be performed on multiple data objects. Typical applications are digital signal processing and graphics processing. Intel's first IA-32 SIMD effort was the MMX instruction set. MMX had two main problems: it re-used existing x87 floating-point registers making the CPUs unable to work on both floating-point and SIMD data at the same time, and it only worked on integers. SSE floating-point instructions operate on a new independent register set, the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Athlon 64 X2

The Athlon 64 X2 is the first native dual-core desktop central processing unit (CPU) designed by Advanced Micro Devices (AMD). It was designed from scratch as native dual-core by using an already multi-CPU enabled Athlon 64, joining it with another functional core on one die, and connecting both via a shared dual-channel memory controller/north bridge and additional control logic. The initial versions are based on the E stepping model of the Athlon 64 and, depending on the model, have either 512 or 1024 KB of L2 cache per core. The Athlon 64 X2 can decode instructions for Streaming SIMD Extensions 3 (SSE3), except those few specific to Intel's architecture. The first Athlon 64 X2 CPUs were released in May 2005, in the same month as Intel's first dual-core processor, the Pentium D. In June 2007, AMD released low-voltage variants of their low-end 65 nm Athlon 64 X2, named "Athlon X2". The Athlon X2 processors feature reduced thermal design power (TDP) of 45 Watt (W). The na ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sempron

Sempron has been the marketing name used by AMD for several different budget desktop CPUs, using several different technologies and CPU socket formats. The Sempron replaced the AMD Duron processor and competed against Intel's Celeron series of processors. AMD coined the name from the Latin '' semper'', which means "always", to suggest the Sempron is suitable for "daily use, practical, and part of everyday life". The last Semprons were launched in April 2014. The brand was retired with the launch of the AMD A-Series APUs. History and features The first Sempron CPUs were based on the Athlon XP architecture using the ''Thoroughbred'' or ''Thorton'' core. These models were equipped with the Socket A interface, 256 KiB L2 cache and 166 MHz Front side bus (FSB 333). Thoroughbred cores natively had 256 KiB L2 cache, but Thortons had 512 KiB L2 cache, half of which was disabled and could sometimes be reactivated with a slight physical modification to the chip. Lat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD Turion

AMD Turion is the brand name AMD applies to its x86-64 low-power consumption (''mobile'') processors codenamed ''K8L''. The Turion 64 and Turion 64 X2/Ultra processors compete with Intel's mobile processors, initially the '' Pentium M'' and the Intel Core and Intel Core 2 processors. Features Turion 64 Earliest Turion 64 processors are plugged into AMD's Socket 754. They are equipped with 512 or 1024 KiB of L2 cache, a 64-bit single channel on-die DDR-400 memory controller, and an 800 MHz HyperTransport bus. Battery saving features, like '' PowerNow!'', are central to the marketing and usefulness of these CPUs. The newer "Richmond" models are designed for AMD's Socket S1 and have a double-channel DDR2 controller. Turion 64 X2 Turion 64 X2 is AMD's 64-bit dual-core mobile CPU, intended to compete with Intel's Core and Core 2 CPUs. The Turion 64 X2 was launched on May 17, 2006, after several delays. These processors use Socket S1 and feature DDR2 memory. The ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SIMD

Single instruction, multiple data (SIMD) is a type of parallel processing in Flynn's taxonomy. SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it should not be confused with an ISA. SIMD describes computers with multiple processing elements that perform the same operation on multiple data points simultaneously. Such machines exploit data level parallelism, but not concurrency: there are simultaneous (parallel) computations, but each unit performs the exact same instruction at any given moment (just with different data). SIMD is particularly applicable to common tasks such as adjusting the contrast in a digital image or adjusting the volume of digital audio. Most modern CPU designs include SIMD instructions to improve the performance of multimedia use. SIMD has three different subcategories in Flynn's 1972 Taxonomy, one of which is SIMT. SIMT should not be confused with software thr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier SSE instruction set, and is intended to fully replace MMX. Intel extended SSE2 to create SSE3 in 2004. SSE2 added 144 new instructions to SSE, which has 70 instructions. Competing chip-maker AMD added support for SSE2 with the introduction of their Opteron and Athlon 64 ranges of AMD64 64-bit CPUs in 2003. Features Most of the SSE2 instructions implement the integer vector operations also found in MMX. Instead of the MMX registers they use the XMM registers, which are wider and allow for significant performance improvements in specialized applications. Another advantage of replacing MMX with SSE2 is avoiding the mode switching penalty for issuing x87 instructions present in MMX because it is sharing register space with the x87 FPU. The SSE2 als ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Celeron D

Celeron is Intel's brand name for low-end IA-32 and x86-64 computer microprocessor models targeted at low-cost personal computers. Celeron processors are compatible with IA-32 software. They typically offer less performance per clock speed compared to flagship Intel CPU lines, such as the Pentium or Core brands. Celeron branded processors often have less cache or intentionally disabled advanced features, with variable impact on performance. While some Celeron designs have achieved strong performance for their segment, most of the Celeron line has exhibited noticeably degraded performance. This has been the primary justification for the higher cost of other Intel CPU brands versus the Celeron range. Introduced in April 1998, the first Celeron-branded CPU was based on the Pentium II. Subsequent Celeron-branded CPUs were based on the Pentium III, Pentium 4, Pentium M, and Intel Core. In September 2022, Intel announced that the Celeron brand, along with Pentium, will be replaced ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Opteron

Opteron is AMD's x86 former server and workstation processor line, and was the first processor which supported the AMD64 instruction set architecture (known generically as x86-64 or AMD64). It was released on April 22, 2003, with the ''SledgeHammer'' core (K8) and was intended to compete in the server and workstation markets, particularly in the same segment as the Intel Xeon processor. Processors based on the AMD K10 microarchitecture (codenamed ''Barcelona'') were announced on September 10, 2007, featuring a new quad-core configuration. The most-recently released Opteron CPUs are the Piledriver-based Opteron 4300 and 6300 series processors, codenamed "Seoul" and "Abu Dhabi" respectively. In January 2016, the first ARMv8-A based Opteron-branded SoC was released, though it is unclear what, if any, heritage this Opteron-branded product line shares with the original Opteron technology other than intended use in the server space. Technical description Two key capabilitie ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Pentium 4

Pentium 4 is a series of single-core CPUs for desktops, laptops and entry-level servers manufactured by Intel. The processors were shipped from November 20, 2000 until August 8, 2008. The production of Netburst processors was active from 2000 until May 21, 2010. All Pentium 4 CPUs are based on the NetBurst microarchitecture. The Pentium 4 '' Willamette'' (180 nm) introduced SSE2, while the '' Prescott'' (90 nm) introduced SSE3. Later versions introduced Hyper-Threading Technology (HTT). The first Pentium 4-branded processor to implement 64-bit was the ''Prescott'' (90 nm) (February 2004), but this feature was not enabled. Intel subsequently began selling 64-bit Pentium 4s using the ''"E0" revision'' of the Prescotts, being sold on the OEM market as the Pentium 4, model F. The E0 revision also adds eXecute Disable (XD) (Intel's name for the NX bit) to Intel 64. Intel's official launch of Intel 64 (under the name EM64T at that time) in mainstream de ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Celeron

Celeron is Intel's brand name for low-end IA-32 and x86-64 computer microprocessor models targeted at low-cost personal computers. Celeron processors are compatible with IA-32 software. They typically offer less performance per clock speed compared to flagship Intel CPU lines, such as the Pentium or Core brands. Celeron branded processors often have less cache or intentionally disabled advanced features, with variable impact on performance. While some Celeron designs have achieved strong performance for their segment, most of the Celeron line has exhibited noticeably degraded performance. This has been the primary justification for the higher cost of other Intel CPU brands versus the Celeron range. Introduced in April 1998, the first Celeron-branded CPU was based on the Pentium II. Subsequent Celeron-branded CPUs were based on the Pentium III, Pentium 4, Pentium M, and Intel Core. In September 2022, Intel announced that the Celeron brand, along with Pentium, will be replaced w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

_(JPG).jpg)