Sempron on:

[Wikipedia]

[Google]

[Amazon]

Sempron has been the marketing name used by AMD for several different budget desktop

* L1-Cache: 64 + 64 KiB (Data + Instructions)

* L2-Cache: 128/256 KiB, full speed

* MMX, Extended

* L1-Cache: 64 + 64 KiB (Data + Instructions)

* L2-Cache: 128/256 KiB, full speed

* MMX, Extended

AMD: Sempron CPUs, FM2/FM2+ Model Number Comparison

Accessed 8 September 2015 *Model 250, 3.6 GHz/3.2 GHz, 1MB cache, 65W, Piledriver microarchitecture, Richland core

AMD K7 Sempron technical specifications

AMD K8 Sempron technical specifications

AMD's Desktop Sempron product page

{{AMD processors AMD x86 microprocessors

CPU

A central processing unit (CPU), also called a central processor, main processor or just processor, is the electronic circuitry that executes instructions comprising a computer program. The CPU performs basic arithmetic, logic, controlling, and ...

s, using several different technologies and CPU socket formats. The Sempron replaced the AMD Duron processor and competed against Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California, Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the devel ...

's Celeron series of processors. AMD coined the name from the Latin '' semper'', which means "always", to suggest the Sempron is suitable for "daily use, practical, and part of everyday life". The last Semprons were launched in April 2014. The brand was retired with the launch of the AMD A-Series APUs.

History and features

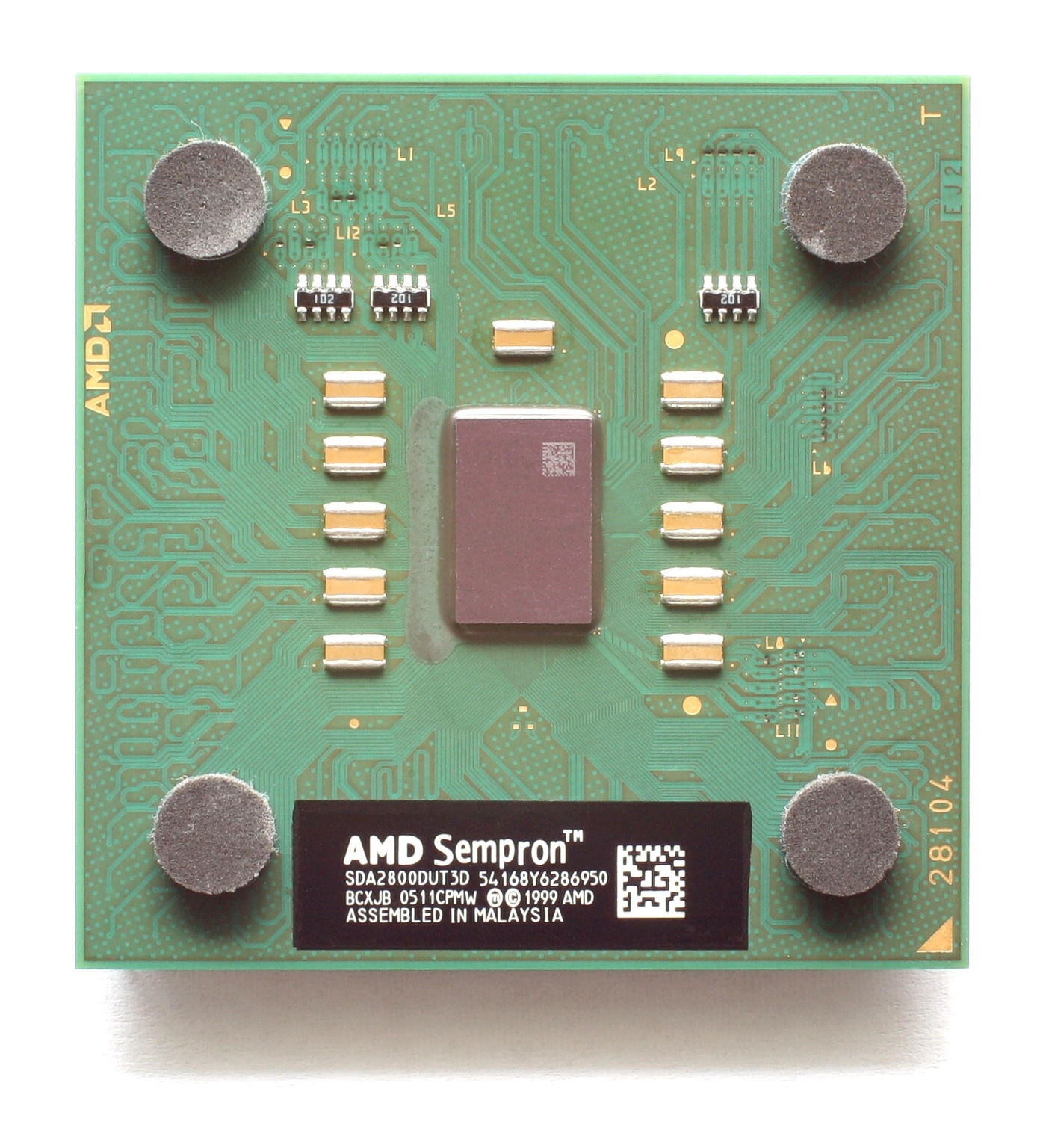

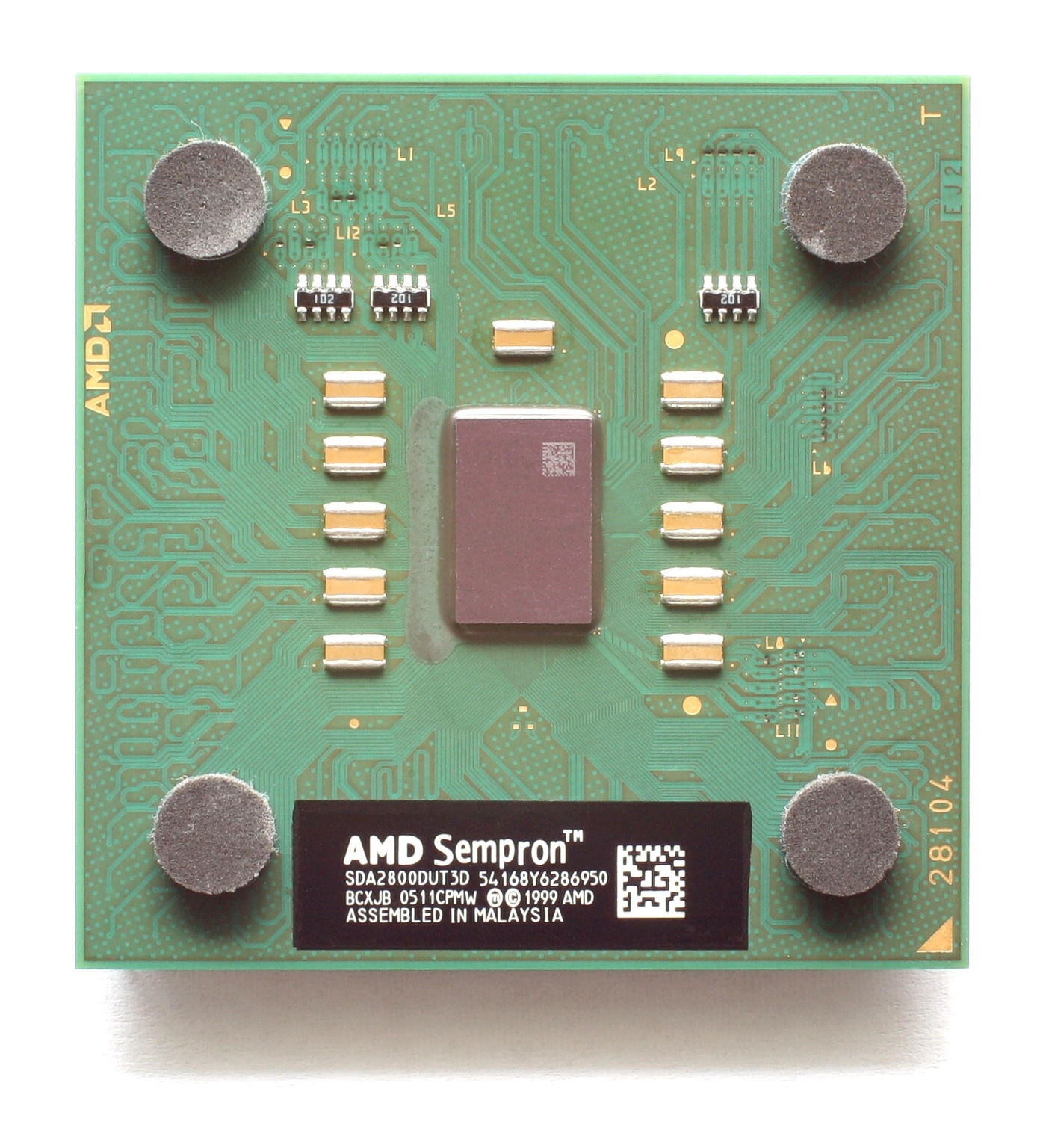

The first Sempron CPUs were based on theAthlon XP

Athlon is the brand name applied to a series of x86-compatible microprocessors designed and manufactured by Advanced Micro Devices (AMD). The original Athlon (now called Athlon Classic) was the first seventh-generation x86 processor and the fi ...

architecture using the ''Thoroughbred'' or ''Thorton'' core. These models were equipped with the Socket A interface, 256 KiB L2 cache and 166 MHz Front side bus (FSB 333). Thoroughbred cores natively had 256 KiB L2 cache, but Thortons had 512 KiB L2 cache, half of which was disabled and could sometimes be reactivated with a slight physical modification to the chip. Later, AMD introduced the Sempron 3000+ CPU, based on the ''Barton'' core with 512 KiB L2 cache. From a hardware and user standpoint, the Socket A Sempron CPUs were essentially identical to Athlon XP desktop CPUs with a new brand name. AMD has ceased production of all Socket A Sempron CPUs.

The second generation (''Paris''/''Palermo'' core) was based on the architecture of the Socket 754 Athlon 64

The Athlon 64 is a ninth-generation, AMD64-architecture microprocessor produced by Advanced Micro Devices (AMD), released on September 23, 2003. It is the third processor to bear the name '' Athlon'', and the immediate successor to the Athlon ...

. Some differences from Athlon 64 processors include a reduced cache size (either 128 or 256 KiB L2), and the absence of AMD64 support in earlier models. Apart from these differences, the Socket 754 Sempron CPUs share most features with the more powerful Athlon 64, including an integrated (on-die) memory controller

The memory controller is a digital circuit that manages the flow of data going to and from the computer's main memory. A memory controller can be a separate chip or integrated into another chip, such as being placed on the same die or as an in ...

, the HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

link, and AMD's "NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

" feature.

In the second half of 2005, AMD added 64-bit support ( AMD64) to the Sempron line. Some journalists (but not AMD) often refer to this revision of chips as "Sempron 64" to distinguish it from the previous revision. AMD's intent in releasing 64-bit entry-level processors was to extend the market for 64-bit processors, which at the time of Sempron 64's first release, was a niche market.

In 2006, AMD announced the Socket AM2 and Socket S1 line of Sempron processors. These are functionally equivalent to the previous generation, except they have a dual-channel DDR2 SDRAM memory controller which replaces the single-channel DDR SDRAM version. The TDP of the standard version remains at 62 W (watts), while the new "Energy Efficient Small Form Factor" version has a reduced 35 W TDP. The Socket AM2 version also does not require a minimum voltage of 1.1 volts to operate, whereas all socket 754 Semprons with Cool'n'Quiet did. In 2006, AMD was selling both Socket 754 and Socket AM2 Sempron CPUs concurrently. In the middle of 2007 AMD appears to have dropped the 754 line and is shipping AM2 and S1 Semprons.

Features table

CPU features tableModels for Socket A (Socket 462)

Thoroughbred B/Thorton (130 nm)

* L1-Cache: 64 + 64 KiB (Data + Instructions) * L2-Cache: 256 KiB, full speed * MMX,3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE

* Socket A (EV6)

* Front side bus: 166 MHz (FSB 333)

* VCore: 1.6 V

* First release: July 28, 2004

* Clockrate: 1500 MHz – 2000 MHz (2200+ to 2800+)

Barton (130 nm)

* L1-Cache: 64 + 64 KiB (Data + Instructions) * L2-Cache: 512 KiB, full speed * MMX,3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE

* Socket A (EV6)

* Front side bus: 166 MHz – 200 MHz (FSB 333 – 400)

* VCore: 1.6 – 1.65 V

* First release: September 17, 2004

* Clockrate: 2000–2200 MHz (Sempron 3000+, Sempron 3300+)

Models for Socket 754

Paris (130 nm SOI)

* L1-Cache: 64 + 64 KiB (Data + Instructions) * L2-Cache: 256 KiB, full speed * MMX,3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE, SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier SSE ins ...

* Enhanced Virus Protection (NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

)

* Integrated 72-bit (Single channel, ECC capable) DDR memory controller

* Socket 754, 800 MHz HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

* VCore: 1.4 V

* First release: July 28, 2004

* Clockrate: 1800 MHz (3100+)

* Stepping: CG (Part No.: *AX)

Palermo (90 nm SOI)

* Early models (stepping D0) are downlabeled "Oakville" mobile Athlon64 * L1-Cache: 64 + 64 KiB (Data + Instructions) * L2-Cache: 128/256 KiB, full speed * MMX,3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE, SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier SSE ins ...

* SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revi ...

support on E3 and E6 steppings

* AMD64 on E6 stepping

* Cool'n'Quiet (Sempron 3000+ and higher)

* Enhanced Virus Protection (NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

)

* Integrated 72-bit (Single channel, ECC capable) DDR memory controller

* Socket 754, 800 MHz HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

* VCore: 1.4 V

* First release: February 2005

* Clockrate: 1400–2000 MHz

**128 KiB L2-Cache (Sempron 2600+, 3000+, 3300+)

**256 KiB L2-Cache (Sempron 2500+, 2800+, 3100+, 3400+)

* Steppings: D0 (Part No.: *BA), E3 (Part No.: *BO), E6 (Part No.: *BX)

Models for Socket 939

Palermo (90 nm SOI)

* L1-Cache: 64 + 64 KiB (Data + Instructions) * L2-Cache: 128/256 KiB, full speed * MMX,3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE, SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier SSE ins ...

, SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revi ...

, AMD64 (E6 Steppings Only), Cool'n'Quiet, NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

* Integrated 144-bit (Dual channel, ECC capable) DDR memory controller

* Socket 939, 800 MHz HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

* VCore: 1.35/1.4 V

* First release: October 2005

* Clockrate: 1800–2000 MHz

**128 KiB L2-Cache (Sempron 3000+, 3400+)

**256 KiB L2-Cache (Sempron 3200+, 3500+)

* Steppings: E3 (Part No.: *BP), E6 (Part No.: *BW)

Models for Socket AM2

Manila (90 nm SOI)

* L1-Cache: 64 + 64 KiB (Data + Instructions)

* L2-Cache: 128/256 KiB, full speed

* MMX, Extended

* L1-Cache: 64 + 64 KiB (Data + Instructions)

* L2-Cache: 128/256 KiB, full speed

* MMX, Extended 3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE, SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier SSE ins ...

, SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revi ...

, AMD64, Cool'n'Quiet, NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

* Integrated 128-bit (Dual channel) DDR2 memory controller

* Socket AM2, 800 MHz HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

* VCore: 1.25/1.35/1.40 V (1.20/1.25 V for Energy Efficient SFF version)

* First release: May 23, 2006

* Clockrate: 1600–2200 MHz

**128 KiB L2-Cache (Sempron 2800+, 3200+, 3500+)

**256 KiB L2-Cache (Sempron 3000+, 3400+, 3600+, 3800+)

* Stepping: F2 (Part No.: *CN, *CW)

Sparta (65 nm SOI)

* L1-Cache: 64 + 64 KiB (Data + Instructions) * L2-Cache: 256/512 KiB, full speed * MMX, Extended3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE, SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier SSE ins ...

, SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revi ...

, AMD64, Cool'n'Quiet, NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

* Integrated 128-bit (Dual channel) DDR2 memory controller

* Socket AM2, 800 MHz HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

* VCore: 1.20/1.40 V

* First release: August 20, 2007

* Clockrate: 1900–2300 MHz

**256 KiB L2-Cache (Sempron LE-1100, LE-1150)

**512 KiB L2-Cache (Sempron LE-1200, LE-1250, LE-1300)

* Stepping: G1 (Part No.: *DE), G2 (Part No.: *DP)

Brisbane (65 nm SOI)

Models for Socket AM3

Sargas (45 nm SOI)

* Chip harvests from Regor with one core disabled * Core Speed (MHz) – 2600–2900 * Max Temps (C): 63 * VCore: 1.35 V * TDP: 45 W * L1 Cache Size (KB) 128 * L2 Cache Size (KB) 1024 * CPU Arch : 1 CPU – 1 Cores – 1 Threads * CPU EXT : MMX(+) 3DNow!(+) SSE SSE2 SSE3 SSE4A x86-64AMD-V

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU.

In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-a ...

, Cool'n'Quiet, NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

* Integrated 128-bit (Dual Channel) DDR2 + DDR3 Memory Controller

* Socket AM3, 2000 MHz HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

* Steppings: C2, C3

Models for Socket S1 (638)

Keene (90 nm SOI)

* L1-Cache: 64 + 64 KiB (Data + Instructions) * L2-Cache: 256 or 512 KiB, full speed * MMX, Extended3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE, SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier SSE ins ...

, SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revi ...

, AMD64, Cool'n'Quiet, NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

* Integrated 128-bit (Dual channel) DDR2 memory controller

* Socket S1, 800 MHz HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

* VCore: 0.950-1.25 V

* First release: May 17, 2006

* Clockrate: 1000–2000 MHz

**256 KiB L2-Cache (Sempron 2100+, 3400+)

**512 KiB L2-Cache (Sempron 3200+, 3500+, 3600+)

* Stepping: F2 (Part No.: *CM)

Sable (65 nm SOI)

* L1-Cache: 64 + 64 KiB (Data + Instructions) * L2-Cache: 512 KiB, full speed * MMX, Extended3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE, SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier SSE ins ...

, SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revi ...

, AMD64, Cool'n'Quiet, NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

* Integrated 128-bit (Dual channel) DDR2 memory controller

* Socket S1, 1600 MHz HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

* VCore: 0.950-1.25 V

* First release: January 8, 2009

* Clockrate: 2000–2100 MHz 25w

**512 KiB L2-Cache

Models for ASB1 package (BGA)

Huron (65 nm SOI)

*L1-Cache: 64 + 64 KiB (Data + Instructions) *L2-Cache: 256 KiB, full speed * MMX, Extended3DNow!

3DNow! is a deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set, enabling it to perform vector processing of flo ...

, SSE, SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets first introduced by Intel with the initial version of the Pentium 4 in 2000. It extends the earlier SSE ins ...

, SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revi ...

, AMD64, Cool'n'Quiet, NX bit

The NX bit (no-execute) is a technology used in CPUs to segregate areas of memory for use by either storage of processor instructions or for storage of data, a feature normally only found in Harvard architecture processors. However, the NX bit is ...

*Integrated 128-bit (Dual channel) DDR2 memory controller

* ASB1 package, 800 MHz HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on Apri ...

*VCore: ?

*First release: January 8, 2009

*Clockrate: 1000–1500 MHz

**256 KiB L2-Cache (Sempron 200U) 1000 MHz TDP 8 W

**256 KiB L2-Cache (Sempron 210U) 1500 MHz TDP 15 W

*Stepping: ? (Part No.: *DV)

Models for Socket 754 32-bit Semprons

Models for Socket S1 (638) 64-bit Semprons

FM2/FM2+ Semprons

*Model 240, 3.3 GHz/2.9 GHz, 1MB cache, 65WAccessed 8 September 2015 *Model 250, 3.6 GHz/3.2 GHz, 1MB cache, 65W, Piledriver microarchitecture, Richland core

Models for Socket AM1

Semprons without Cool'n'Quiet

AMD has released some Sempron processors without Cool'n'Quiet support. The following table describes those processors lacking Cool'n'Quiet.See also

*List of AMD Sempron microprocessors

The Sempron is a name used for AMD's low-end CPUs, replacing the Duron processor. The name was introduced in 2004, and processors with this name continued to be available for the FM2/FM2+ socket in 2015.

Features overview

CPU features table

Desk ...

References

External links

AMD K7 Sempron technical specifications

AMD K8 Sempron technical specifications

AMD's Desktop Sempron product page

{{AMD processors AMD x86 microprocessors