|

DDR3

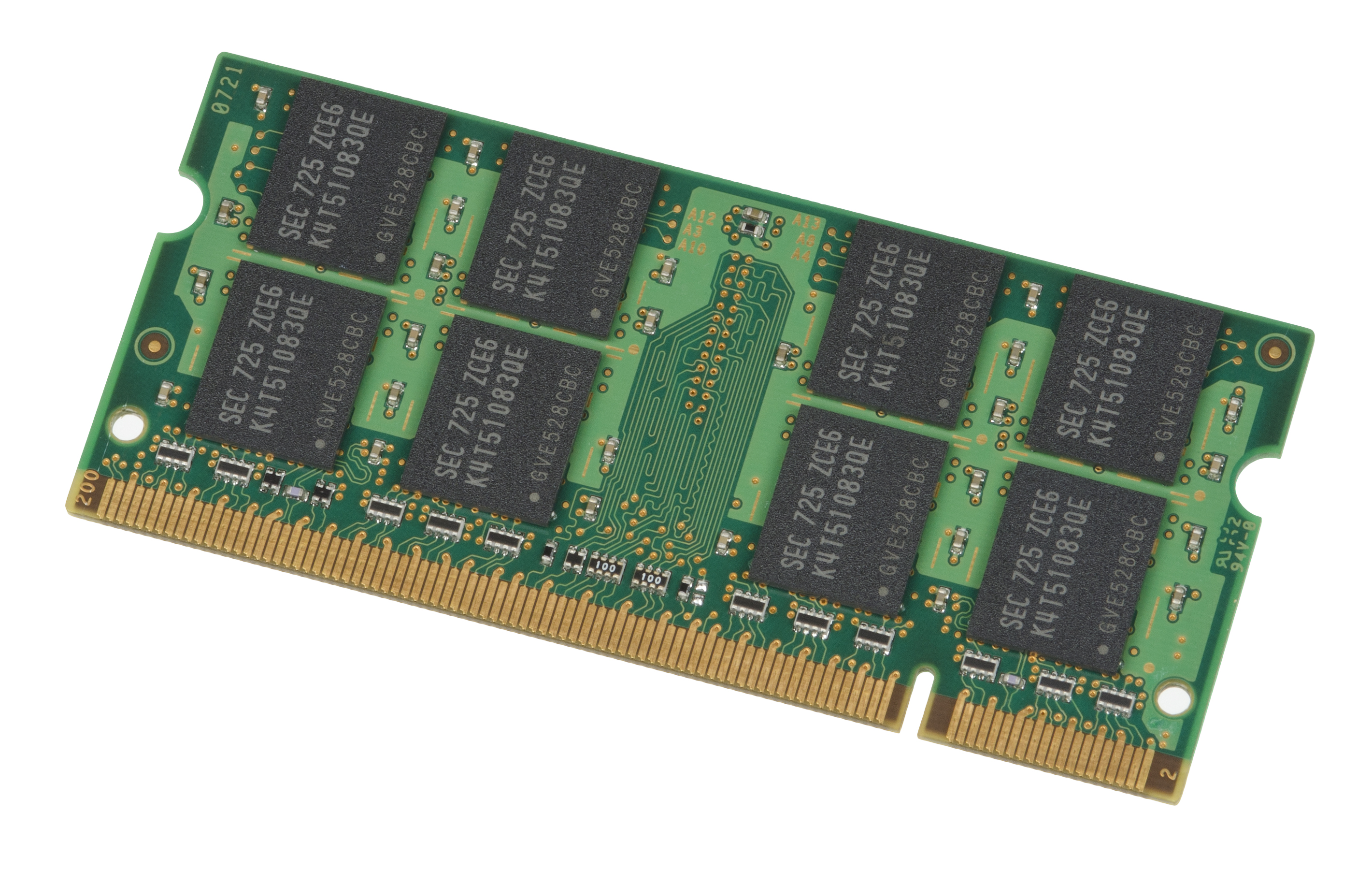

Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth ("double data rate") interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors. DDR3 is a DRAM interface specification. The actual DRAM arrays that store the data are similar to earlier types, with similar performance. The primary benefit of DDR3 SDRAM over its immediate predecessor DDR2 SDRAM, is its ability to transfer data at twice the rate (eight times the speed of its internal memory arrays), enabling higher bandwidth or peak data rates. The DDR3 standard permits DRAM chip capacities of up to 8 gigabits (Gbit), and up to four ran ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR4 SDRAM

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth (" double data rate") interface. Released to the market in 2014, it is a variant of dynamic random-access memory (DRAM), of which some have been in use since the early 1970s, and a higher-speed successor to the DDR2 and DDR3 technologies. DDR4 is not compatible with any earlier type of random-access memory (RAM) due to different signaling voltage and physical interface, besides other factors. DDR4 SDRAM was released to the public market in Q2 2014, focusing on ECC memory, while the non-ECC DDR4 modules became available in Q3 2014, accompanying the launch of Haswell-E processors that require DDR4 memory. Features The primary advantages of DDR4 over its predecessor, DDR3, include higher module density and lower voltage requirements, coupled with higher data rate transfer speeds. The DDR4 standard allows for DIMMs o ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Prefetch Buffer

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions only delayed by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memory acc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Synchronous Dynamic Random-access Memory

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions only delayed by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memory ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR SDRAM

Double Data Rate Synchronous Dynamic Random-Access Memory (DDR SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) class of memory integrated circuits used in computers. DDR SDRAM, also retroactively called DDR1 SDRAM, has been superseded by DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM and DDR5 SDRAM. None of its successors are forward or backward compatible with DDR1 SDRAM, meaning DDR2, DDR3, DDR4 and DDR5 memory modules will not work in DDR1-equipped motherboards, and vice versa. Compared to single data rate ( SDR) SDRAM, the DDR SDRAM interface makes higher transfer rates possible by more strict control of the timing of the electrical data and clock signals. Implementations often have to use schemes such as phase-locked loops and self-calibration to reach the required timing accuracy. The interface uses double pumping (transferring data on both the rising and falling edges of the clock signal) to double data bus bandwidth without a corresp ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Phenom II

Phenom II is a family of AMD's multi-core 45 nm processors using the AMD K10 microarchitecture, succeeding the original Phenom. Advanced Micro Devices released the Socket AM2+ version of Phenom II in December 2008, while Socket AM3 versions with DDR3 support, along with an initial batch of triple- and quad-core processors were released on February 9, 2009. Dual-processor systems require Socket F+ for the Quad FX platform. The next-generation Phenom II X6 was released on April 27, 2010. The Phenom II X4 operates as the processor component of AMD's Dragon Platform, which also includes the 790 series chipset and Radeon HD 4800 series graphics. The Thuban Phenom II X6 is the CPU in the Leo Platform which also includes the AMD 890 chipset and the Radeon HD 5800 series graphics. Features The Phenom II triples the shared L3 cache size from 2MB (in the original Phenom line) to 6MB, leading to benchmark performance gains as high as 30%. In another change from the origin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Core I7

The following is a list of Intel Core i7 brand microprocessors. Introduced in 2008, the Core i7 line of microprocessors are intended to be used by high-end users. Desktop processors Nehalem microarchitecture (1st generation) "Bloomfield" (45 nm) * All models support: MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), Intel VT-x, Hyper-threading, Turbo Boost, Smart Cache. * FSB has been replaced with QPI. * Transistors: 731 million * Die size: 263 mm * Steppings: C0, D0 "Lynnfield" (45 nm) * All models support: MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), TXT, Intel VT-x, Intel VT-d, Hyper-threading, Turbo Boost, Smart Cache. * Core i7-875K features an unlocked multiplier and does not support Intel TXT and Intel VT-d. * FSB has been replaced with DMI. *Moves the QPI link an ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR2 SDRAM

Double Data Rate 2 Synchronous Dynamic Random-Access Memory (DDR2 SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It superseded the original DDR SDRAM specification, and was itself superseded by DDR3 SDRAM (launched in 2007). DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR. In addition to double pumping the data bus as in DDR SDRAM (transferring data on the rising and falling edges of the bus clock signal), DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as DDR results in DDR2 being able to provide the same bandwidth but with better latency. Alternatively, DDR2 memory operating at twice the external d ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Memory Timings

Memory timings or RAM timings describe the timing information of a memory module. Due to the inherent qualities of VLSI and microelectronics, memory chips require time to fully execute commands. Executing commands too quickly will result in data corruption and results in system instability. With appropriate time between commands, memory modules/chips can be given the opportunity to fully switch transistors, charge capacitors and correctly signal back information to the memory controller. Because system performance depends on how fast memory can be used, this timing directly affects the performance of the system. The timing of modern synchronous dynamic random-access memory (SDRAM) is commonly indicated using four parameters: CL, TRCD, TRP, and TRAS in units of clock cycles; they are commonly written as four numbers separated with hyphens, ''e.g.'' 7-8-8-24. The fourth (tRAS) is often omitted, or a fifth, the Command rate, sometimes added (normally 2T or 1T, also written 2N, 1N). Th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Double Data Rate

In computing, a computer bus operating with double data rate (DDR) transfers data on both the rising and falling edges of the clock signal. This is also known as double pumped, dual-pumped, and double transition. The term toggle mode is used in the context of NAND flash memory. Overview The simplest way to design a clocked electronic circuit is to make it perform one transfer per full cycle (rise and fall) of a clock signal. This, however, requires that the clock signal changes twice per transfer, while the data lines change at most once per transfer. When operating at a high bandwidth, signal integrity limitations constrain the clock frequency. By using both edges of the clock, the data signals operate with the same limiting frequency, thereby doubling the data transmission rate. This technique has been used for microprocessor front-side busses, Ultra-3 SCSI, expansion buses (AGP, PCI-X), graphics memory ( GDDR), main memory (both RDRAM and DDR1 through DDR5), and t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Stub Series Terminated Logic

Stub Series Terminated Logic (SSTL) is a group of electrical standards for driving transmission lines commonly used with DRAM based DDR memory IC's and memory modules. SSTL is primarily designed for driving the DDR (double-data-rate) SDRAM modules used in computer memory; however, it is also used in other applications, notably some PCI Express PHYs and other high-speed devices. Four voltage levels for SSTL are defined: *SSTL_3, 3.3 V, defined in EIA/JESD8-8 1996 *SSTL_2, 2.5 V, defined in EIA/JESD8-9B 2002 used in DDR among other things. *SSTL_18, 1.8 V, defined in EIA/JESD8-15A, used in DDR2 among other things. *SSTL_15, 1.5 V, used in DDR3 Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth ("double data rate") interface, and has been in use since 2007. It is the higher-speed ... among other things. SSTL_3 uses a reference of 0.45 * VDDQ (1.5 V). SSTL_2 and SSTL_18 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)