|

CPU Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (M ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Hardware Cache

In computing, a cache ( ) is a hardware or software component that stores data so that future requests for that data can be served faster; the data stored in a cache might be the result of an earlier computation or a copy of data stored elsewhere. A cache hit occurs when the requested data can be found in a cache, while a cache miss occurs when it cannot. Cache hits are served by reading data from the cache, which is faster than recomputing a result or reading from a slower data store; thus, the more requests that can be served from the cache, the faster the system performs. To be cost-effective, caches must be relatively small. Nevertheless, caches are effective in many areas of computing because typical computer applications access data with a high degree of locality of reference. Such access patterns exhibit temporal locality, where data is requested that has been recently requested, and spatial locality, where data is requested that is stored near data that has already be ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Multi-level Caches

Multilevel or multi-level may refer to: * A hierarchy A hierarchy (from Ancient Greek, Greek: , from , 'president of sacred rites') is an arrangement of items (objects, names, values, categories, etc.) that are represented as being "above", "below", or "at the same level as" one another. Hierarchy ..., a system where items are arranged in an "above-below" relation. * A system that is composed of several layers. * Bombardier MultiLevel Coach, a passenger rail car by Bombardier. See also * * {{dab ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

IBM Z13 (microprocessor)

The z13 is a microprocessor made by IBM for their z13 mainframe computers, announced on January 14, 2015. Manufactured at GlobalFoundries' East Fishkill, New York fabrication plant (formerly IBM's own plant). IBM stated that it is the world's fastest microprocessor and is about 10% faster than its predecessor the zEC12 in general single-threaded computing, but significantly more when doing specialized tasks. The IBM z13 is the last z Systems server to support running an operating system in ESA/390 architecture mode. However, all 24-bit and 31-bit problem-state application programs originally written to run on the ESA/390 architecture are unaffected by this change. Description The Processor Unit chip (PU chip) has an area of 678 mm2 and contains 3.99 billion transistors. It is fabricated using IBM's 22 nm CMOS silicon on insulator fabrication process, using 17 metal layers and supporting speeds of 5.0 GHz, which is less than its predecessor, the zEC12. The PU c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

IBM ZEC12 (microprocessor)

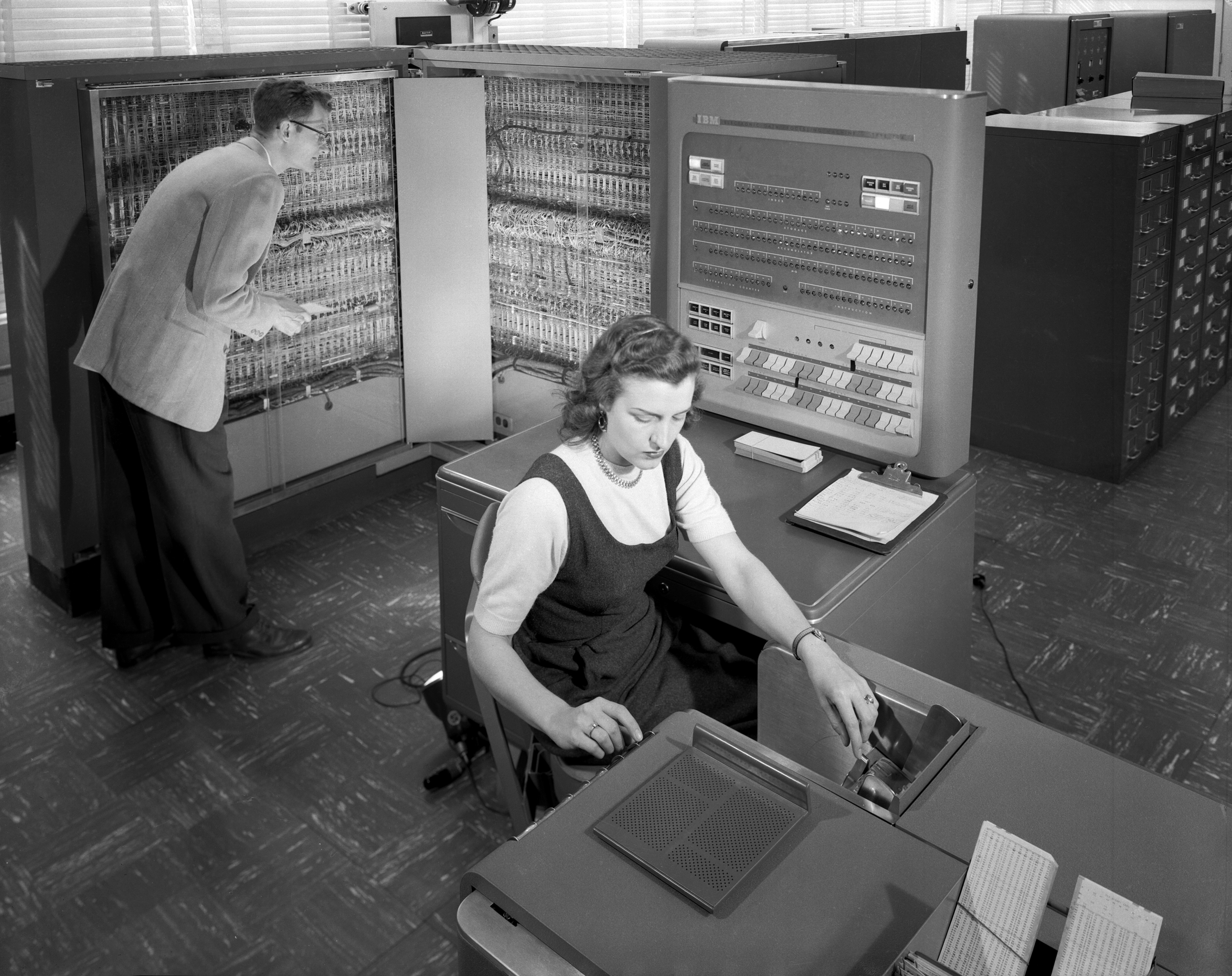

International Business Machines Corporation (using the trademark IBM), nicknamed Big Blue, is an American multinational technology company headquartered in Armonk, New York, and present in over 175 countries. It is a publicly traded company and one of the 30 companies in the Dow Jones Industrial Average. IBM is the largest industrial research organization in the world, with 19 research facilities across a dozen countries; for 29 consecutive years, from 1993 to 2021, it held the record for most annual U.S. patents generated by a business. IBM was founded in 1911 as the Computing-Tabulating-Recording Company (CTR), a holding company of manufacturers of record-keeping and measuring systems. It was renamed "International Business Machines" in 1924 and soon became the leading manufacturer of punch-card tabulating systems. During the 1960s and 1970s, the IBM mainframe, exemplified by the System/360 and its successors, was the world's dominant computing platform, with the com ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Intel Core 2 Duo

Intel Core is a line of multi-core (with the exception of Core Solo and Core 2 Solo) central processing units (CPUs) for midrange, embedded, workstation, high-end and enthusiast computer markets marketed by Intel Corporation. These processors displaced the existing mid- to high-end Pentium processors at the time of their introduction, moving the Pentium to the entry level. Identical or more capable versions of Core processors are also sold as Xeon processors for the server and workstation markets. Core was launched in January 2006 as a mobile-only series, consisting of single- and dual-core models. It was then succeeded later in July by the Core 2 series, which included both desktop and mobile processors with up to four cores, and introduced 64-bit support. Since 2008, Intel began introducing the Core i3, Core i5, Core i7 and Core i9 lineup of processors, succeeding Core 2. A new naming scheme debuted in 2023, consisting of Core 3, Core 5, and Core 7 for mainstream processo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Mebibyte

The byte is a units of information, unit of digital information that most commonly consists of eight bits. Historically, the byte was the number of bits used to encode a single character (computing), character of text in a computer and for this reason it is the smallest address space, addressable unit of Computer memory, memory in many computer architectures. To disambiguate arbitrarily sized bytes from the common 8-bit computing, 8-bit definition, Computer network, network protocol documents such as the Internet Protocol () refer to an 8-bit byte as an Octet (computing), octet. Those bits in an octet are usually counted with numbering from 0 to 7 or 7 to 0 depending on the bit numbering, bit endianness. The size of the byte has historically been Computer hardware, hardware-dependent and no definitive standards existed that mandated the size. Sizes from 1 to 48 bits have been used. The six-bit character code was an often-used implementation in early encoding systems, and compute ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Kibibyte

The byte is a unit of digital information that most commonly consists of eight bits. Historically, the byte was the number of bits used to encode a single character of text in a computer and for this reason it is the smallest addressable unit of memory in many computer architectures. To disambiguate arbitrarily sized bytes from the common 8-bit definition, network protocol documents such as the Internet Protocol () refer to an 8-bit byte as an octet. Those bits in an octet are usually counted with numbering from 0 to 7 or 7 to 0 depending on the bit endianness. The size of the byte has historically been hardware-dependent and no definitive standards existed that mandated the size. Sizes from 1 to 48 bits have been used. The six-bit character code was an often-used implementation in early encoding systems, and computers using six-bit and nine-bit bytes were common in the 1960s. These systems often had memory words of 12, 18, 24, 30, 36, 48, or 60 bits, corresponding to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Dynamic Random-access Memory

Dynamics (from Greek language, Greek δυναμικός ''dynamikos'' "powerful", from δύναμις ''dynamis'' "power (other), power") or dynamic may refer to: Physics and engineering * Dynamics (mechanics), the study of forces and their effect on motion Brands and enterprises * Dynamic (record label), an Italian record label in Genoa Mathematics * Dynamical system, a concept describing a point's time dependency ** Topological dynamics, the study of dynamical systems from the viewpoint of general topology * Symbolic dynamics, a method to model dynamical systems Social science * Group dynamics, the study of social group processes especially * Population dynamics, in life sciences, the changes in the composition of a population * Psychodynamics, the study of psychological forces driving human behavior * Social dynamics, the ability of a society to react to changes * Spiral Dynamics, a social development theory Other uses * Dynamics (music), the softness or loudn ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Multi-core Processor

A multi-core processor (MCP) is a microprocessor on a single integrated circuit (IC) with two or more separate central processing units (CPUs), called ''cores'' to emphasize their multiplicity (for example, ''dual-core'' or ''quad-core''). Each core reads and executes Instruction set, program instructions, specifically ordinary Instruction set, CPU instructions (such as add, move data, and branch). However, the MCP can run instructions on separate cores at the same time, increasing overall speed for programs that support Multithreading (computer architecture), multithreading or other parallel computing techniques. Manufacturers typically integrate the cores onto a single IC Die (integrated circuit), die, known as a ''chip multiprocessor'' (CMP), or onto multiple dies in a single Chip carrier, chip package. As of 2024, the microprocessors used in almost all new personal computers are multi-core. A multi-core processor implements multiprocessing in a single physical package. Des ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

System On A Chip

A system on a chip (SoC) is an integrated circuit that combines most or all key components of a computer or Electronics, electronic system onto a single microchip. Typically, an SoC includes a central processing unit (CPU) with computer memory, memory, input/output, and computer data storage#Secondary storage, data storage control functions, along with optional features like a graphics processing unit (GPU), Wi-Fi connectivity, and radio frequency processing. This high level of integration minimizes the need for separate, discrete components, thereby enhancing Performance per watt, power efficiency and simplifying device design. High-performance SoCs are often paired with dedicated memory, such as LPDDR, and flash storage chips, such as Universal Flash Storage, eUFS or eMMC, which may be stacked directly on top of the SoC in a Package on a package, package-on-package (PoP) configuration or placed nearby on the motherboard. Some SoCs also operate alongside specialized chips, such ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Electronics (magazine)

''Electronics'' is a discontinued American trade journal that covers the radio industry and subsequent industries from 1930 to 1995. Its first issue is dated April 1930. The periodical was published with the title ''Electronics'' until 1984, when it was changed temporarily to ''ElectronicsWeek'', but was then reverted to the original title ''Electronics'' in 1985. The ISSN for the corresponding periods are: for the 1930–1984 issues, for the 1984–1985 issues with title ''ElectronicsWeek'', and for the 1985–1995 issues. It was published by McGraw-Hill until 1988, when it was sold to the Dutch company VNU. VNU sold its American electronics magazines to Penton Publishing the next year. Generally a bimonthly magazine, its frequency and page count varied with the state of the industry, until its end in 1995. More than its principal rival '' Electronic News'', it balanced its appeal to managerial and technical interests (at the time of its 1992 makeover, it described itsel ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

IBM 801

The 801 was an experimental central processing unit (CPU) design developed by IBM during the 1970s. It is considered to be the first modern RISC design, relying on processor registers for all computations and eliminating the many variant addressing modes found in CISC designs. Originally developed as the processor for a telephone switch, it was later used as the basis for a minicomputer and a number of products for their mainframe line. The initial design was a 24-bit processor; that was soon replaced by 32-bit implementations of the same concepts and the original 24-bit 801 was used only into the early 1980s. During the initial design the system was considered as a simple processor with limited functionality that would not compete with IBM's more complex systems like the System/370. But as they explored the concept using huge amounts of performance data collected from their customers, the team was able to demonstrate that the simple design was able to easily outperform even the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |