|

SSSE3

Supplemental Streaming SIMD Extensions 3 (SSSE3 or SSE3S) is a SIMD instruction set created by Intel and is the fourth iteration of the SSE technology. History SSSE3 was first introduced with Intel processors based on the Core microarchitecture on June 26, 2006 with the "Woodcrest" Xeons. SSSE3 has been referred to by the codenames Tejas New Instructions (TNI) or Merom New Instructions (MNI) for the first processor designs intended to support it. Functionality SSSE3 contains 16 new discrete instructions. Each instruction can act on 64-bit MMX or 128-bit XMM registers. Therefore, Intel's materials refer to 32 new instructions. They include: * Twelve instructions that perform horizontal addition or subtraction operations. * Six instructions that evaluate absolute values. * Two instructions that perform multiply-and-add operations and speed up the evaluation of dot products. * Two instructions that accelerate packed integer multiply operations and produce integer values wi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Core I7

The following is a list of Intel Core i7 brand microprocessors. Introduced in 2008, the Core i7 line of microprocessors are intended to be used by high-end users. Desktop processors Nehalem microarchitecture (1st generation) "Bloomfield" (45 nm) * All models support: MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), Intel VT-x, Hyper-threading, Turbo Boost, Smart Cache. * FSB has been replaced with QPI. * Transistors: 731 million * Die size: 263 mm * Steppings: C0, D0 "Lynnfield" (45 nm) * All models support: MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), TXT, Intel VT-x, Intel VT-d, Hyper-threading, Turbo Boost, Smart Cache. * Core i7-875K features an unlocked multiplier and does not support Intel TXT and Intel VT-d. * FSB has been replaced with DMI. *Moves the QPI link an ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Core I5

The following is a list of Intel Core i5 brand microprocessors. Introduced in 2009, the Core i5 line of microprocessors are intended to be used by mainstream users. Desktop processors Nehalem microarchitecture (1st generation) "Lynnfield" (45 nm) * All models support: '' MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), Intel VT-x, Turbo Boost, Smart Cache.'' * FSB has been replaced with DMI. * Transistors: 774 million * Die size: 296 mm² * Stepping: B1 Westmere microarchitecture (1st generation) " Clarkdale" ( MCP, 32 nm dual-core) * All models support: '' MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), TXT, Intel VT-x, Intel VT-d, Hyper-threading, Turbo Boost, AES-NI, Smart Cache.'' * Core i5-655K, Core i5-661 does not support ''Intel TXT and Intel VT-d.'' * Core i5-6 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data (SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in their Pentium III series of Central processing units (CPUs) shortly after the appearance of Advanced Micro Devices (AMD's) 3DNow!. SSE contains 70 new instructions (65 unique mnemonics using 70 encodings), most of which work on single precision floating-point data. SIMD instructions can greatly increase performance when exactly the same operations are to be performed on multiple data objects. Typical applications are digital signal processing and graphics processing. Intel's first IA-32 SIMD effort was the MMX instruction set. MMX had two main problems: it re-used existing x87 floating-point registers making the CPUs unable to work on both floating-point and SIMD data at the same time, and it only worked on integers. SSE floating-point instructions operate on a new independent register set, the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

VIA Nano

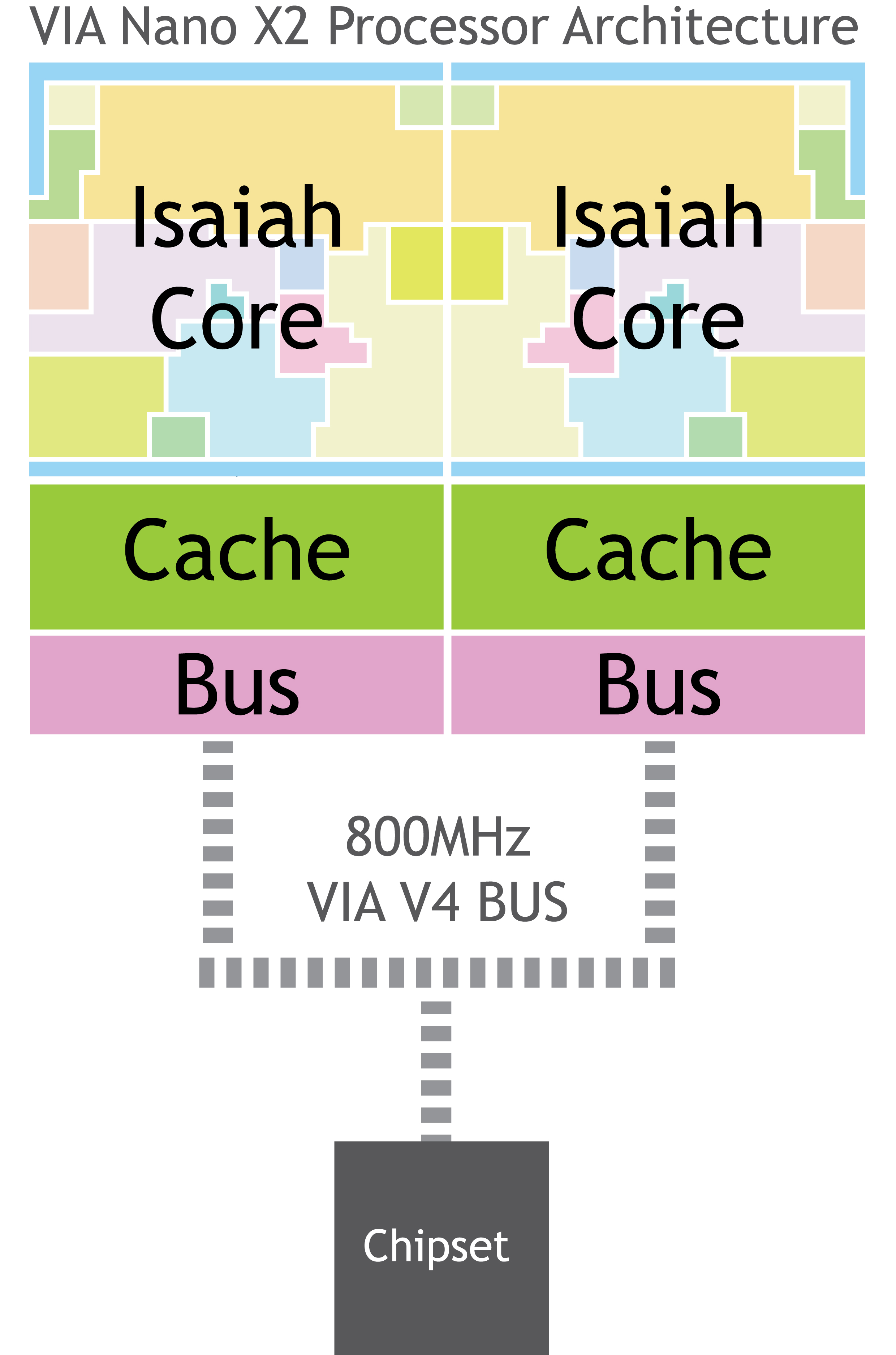

The VIA Nano (formerly code-named VIA Isaiah) is a 64-bit CPU for personal computers. The VIA Nano was released by VIA Technologies in 2008 after five years of development by its CPU division, Centaur Technology. This new Isaiah 64-bit architecture was designed from scratch, unveiled on 24 January 2008, and launched on 29 May, including low-voltage variants and the Nano brand name. The processor supports a number of VIA-specific x86 extensions designed to boost efficiency in low-power appliances. History Unlike Intel and AMD, VIA uses two distinct development code names for each of its CPU cores. In this case, the codename 'CN' was used in the United States by Centaur Technology. Biblical names are used as codes by VIA in Taiwan, and Isaiah was the choice for this particular processor and architecture. It is expected that the VIA Isaiah will be twice as fast in integer performance and four times as fast in floating-point performance as the previous-generation VIA Esther at ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Core (microarchitecture)

The Intel Core microarchitecture (provisionally referred to as Next Generation Micro-architecture, and developed as Merom) is a multi-core processor microarchitecture launched by Intel in mid-2006. It is a major evolution over the Yonah, the previous iteration of the P6 microarchitecture series which started in 1995 with Pentium Pro. It also replaced the NetBurst microarchitecture, which suffered from high power consumption and heat intensity due to an inefficient pipeline designed for high clock rate. In early 2004 the new version of NetBurst (Prescott) needed very high power to reach the clocks it needed for competitive performance, making it unsuitable for the shift to dual/multi-core CPUs. On May 7, 2004 Intel confirmed the cancellation of the next NetBurst. Intel had been developing Merom, the 64-bit evolution of the Pentium M, since 2001, and decided to expand it to all market segments, replacing NetBurst in desktop computers and servers. It inherited from Pentium M t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Xeon

Xeon ( ) is a brand of x86 microprocessors designed, manufactured, and marketed by Intel, targeted at the non-consumer workstation, server, and embedded system markets. It was introduced in June 1998. Xeon processors are based on the same architecture as regular desktop-grade CPUs, but have advanced features such as support for ECC memory, higher core counts, more PCI Express lanes, support for larger amounts of RAM, larger cache memory and extra provision for enterprise-grade reliability, availability and serviceability (RAS) features responsible for handling hardware exceptions through the Machine Check Architecture. They are often capable of safely continuing execution where a normal processor cannot due to these extra RAS features, depending on the type and severity of the machine-check exception (MCE). Some also support multi-socket systems with two, four, or eight sockets through use of the Ultra Path Interconnect (UPI) bus. Overview The ''Xeon'' brand has been ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Atom

Intel Atom is the brand name for a line of IA-32 and x86-64 instruction set ultra-low-voltage processors by Intel Corporation designed to reduce electric consumption and power dissipation in comparison with ordinary processors of the Intel Core series. Atom is mainly used in netbooks, nettops, embedded applications ranging from health care to advanced robotics, mobile Internet devices (MIDs) and phones. The line was originally designed in 45 nm complementary metal–oxide–semiconductor ( CMOS) technology and subsequent models, codenamed ''Cedar'', used a 32 nm process. The first generation of Atom processors are based on the Bonnell microarchitecture. On December 21, 2009, Intel announced the ''Pine Trail'' platform, including new Atom processor code-named ''Pineview'' (Atom N450), with total kit power consumption down 20%. On December 28, 2011, Intel updated the Atom line with the ''Cedar'' processors. In December 2012, Intel launched the 64-bit ''Centerton'' fa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Pentium Dual Core

The Pentium Dual-Core brand was used for mainstream x86-architecture microprocessors from Intel from 2006 to 2009 when it was renamed to Pentium. The processors are based on either the 32-bit '' Yonah'' or (with quite different microarchitectures) 64-bit '' Merom-2M'', '' Allendale'', and '' Wolfdale-3M'' core, targeted at mobile or desktop computers. In terms of features, price, and performance at a given clock frequency, Pentium Dual-Core processors were positioned above Celeron but below Core and Core 2 processors in Intel's product range. The Pentium Dual-Core was also a very popular choice for overclocking, as it can deliver high performance (when overclocked) at a low price. Processor cores In 2006, Intel announced a plan to return the Pentium trademark from retirement to the market, as a moniker of low-cost Core microarchitecture processors based on the single-core Conroe-L but with 1 MB of cache. The identification numbers for those planned Pentiums were similar to th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SIMD

Single instruction, multiple data (SIMD) is a type of parallel processing in Flynn's taxonomy. SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it should not be confused with an ISA. SIMD describes computers with multiple processing elements that perform the same operation on multiple data points simultaneously. Such machines exploit data level parallelism, but not concurrency: there are simultaneous (parallel) computations, but each unit performs the exact same instruction at any given moment (just with different data). SIMD is particularly applicable to common tasks such as adjusting the contrast in a digital image or adjusting the volume of digital audio. Most modern CPU designs include SIMD instructions to improve the performance of multimedia use. SIMD has three different subcategories in Flynn's 1972 Taxonomy, one of which is SIMT. SIMT should not be confused with software thr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Puma (microarchitecture)

The Puma Family 16h is a low-power microarchitecture by AMD for its APUs. It succeeds the Jaguar as a second-generation version, targets the same market, and belongs to the same AMD architecture Family 16h. The ''Beema'' line of processors are aimed at low-power notebooks, and ''Mullins'' are targeting the tablet sector. Design The Puma cores use the same microarchitecture as Jaguar, and inherits the design: * Out-of-order execution and Speculative execution, up to 4 CPU cores * Two-way integer execution * Two-way 128-bit wide floating-point and packed integer execution * Integer hardware divider * Puma does not feature clustered multi-thread (CMT), meaning that there are no "modules" * Puma does not feature Heterogeneous System Architecture or zero-copy * 32 KiB instruction + 32 KiB data L1 cache per core * 1–2 MiB unified L2 cache shared by two or four cores * Integrated single channel memory controller supporting 64bit DDR3L * 3.1 mm2 area per core ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bobcat (processor)

The AMD Bobcat Family 14h is a microarchitecture created by AMD for its AMD APUs, aimed at a low-power/low-cost market. It was revealed during a speech from AMD executive vice-president Henri Richard in Computex 2007 and was put into production Q1 2011. One of the major supporters was executive vice-president Mario A. Rivas who felt it was difficult to compete in the x86 market with a single core optimized for the 10–100 W range and actively promoted the development of the simpler core with a target range of 1–10 W. In addition, it was believed that the core could migrate into the hand-held space if the power consumption can be reduced to less than 1 W. ''Bobcat'' cores are used together with GPU cores in accelerated processing units (APUs) under the "'' Fusion''" brand. A simplified architecture diagram was released at AMD's Analyst Day in November 2009. This is similar in concept with earlier AMD research in 2003,AMD 2003 Microprocessor Forum SlidesSlide 11a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tejas And Jayhawk

Tejas was a code name for Intel's microprocessor, which was to be a successor to the latest Pentium 4 with the Prescott core and was sometimes referred to as Pentium V. Jayhawk was a code name for its Xeon counterpart. The cancellation of the processors in May 2004 underscored Intel's historical transition of its focus on single-core processors to multi-core processors. History In early 2003, Intel showed Tejas and a plan to release it sometime in 2004, but put it off to 2005. Intel, however, canceled development on May 7, 2004. Analysts attribute these delays and cancellation to heat and power consumption problems due to their goal of reaching ever higher clock speeds, even when sacrificing work done per clock (and therefore performance per clock) in the process. This was already the case with Prescott and its mediocre performance increase over Northwood (not to mention heavy competition from Advanced Micro Devices (AMD) with their Athlon 64). Its changes were done to allow Presco ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |