|

AMD Microprocessors

The following is a list of AMD CPU microarchitectures. Nomenclature Historically, AMD's CPU families were given a "K-number" (which originally stood for Kryptonite, an allusion to the Superman comic book character's fatal weakness) starting with their first internal x86 CPU design, the K5, to represent generational changes. AMD has not used K-nomenclature codenames in official AMD documents and press releases since the beginning of 2005, when ''K8'' described the Athlon 64 processor family. AMD now refers to the codename K8 processors as the ''Family 0Fh'' processors. 10h and 0Fh refer to the main result of the CPUID x86 processor instruction. In hexadecimal numbering, 0F(h) (where the ''h'' represents hexadecimal numbering) equals the decimal number 15, and 10(h) equals the decimal number 16. (The "K10h" form that sometimes pops up is an improper hybrid of the "K" code and ''Family XXh'' identifier number.) The Family hexadecimal identifier number can be determined for a par ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Central Processing Unit

A central processing unit (CPU), also called a central processor, main processor, or just processor, is the primary Processor (computing), processor in a given computer. Its electronic circuitry executes Instruction (computing), instructions of a computer program, such as arithmetic, logic, controlling, and input/output (I/O) operations. This role contrasts with that of external components, such as main memory and I/O circuitry, and specialized coprocessors such as graphics processing units (GPUs). The form, CPU design, design, and implementation of CPUs have changed over time, but their fundamental operation remains almost unchanged. Principal components of a CPU include the arithmetic–logic unit (ALU) that performs arithmetic operation, arithmetic and Bitwise operation, logic operations, processor registers that supply operands to the ALU and store the results of ALU operations, and a control unit that orchestrates the #Fetch, fetching (from memory), #Decode, decoding and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

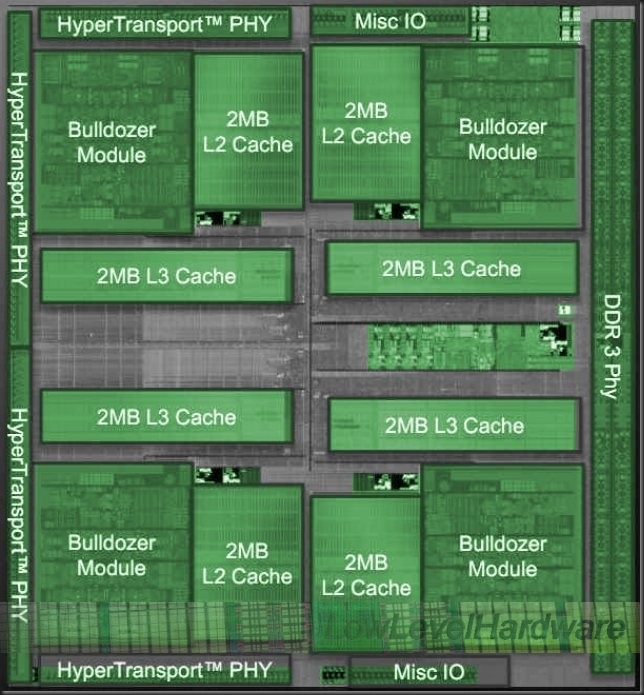

Bulldozer (microarchitecture)

The AMD Bulldozer Family 15h is a microprocessor microarchitecture for the FX and Opteron line of processors, developed by AMD for the desktop and server markets. Bulldozer is the codename for this family of microarchitectures. It was released on October 12, 2011, as the successor to the K10 microarchitecture. Bulldozer is designed from scratch, not a development of earlier processors. The core is specifically aimed at computing products with TDPs of 10 to 125 watts. AMD claims dramatic performance-per-watt efficiency improvements in high-performance computing (HPC) applications with Bulldozer cores. The ''Bulldozer'' cores support most of the instruction sets implemented by Intel processors ( Sandy Bridge) available at its introduction (including SSSE3, SSE4.1, SSE4.2, AES, CLMUL, and AVX) as well as new instruction sets proposed by AMD; ABM, XOP, FMA4 and F16C. Only Bulldozer GEN4 (Excavator) supports AVX2 instruction sets. Overview According to AMD, Bul ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen 5

Zen 5 (''"Nirvana"'') is the name for a CPU microarchitecture by AMD, shown on their roadmap in May 2022, launched for mobile in July 2024 and for desktop in August 2024. It is the successor to Zen 4 and is currently fabricated on TSMC's 5 nm process, N4P process. Zen 5 is also planned to be fabricated on the 3 nm process, N3E process in the future. The Zen 5 microarchitecture powers Ryzen 9000 series desktop processors (codenamed "Granite Ridge"), Epyc 9005 server processors (codenamed "Turin"), and Ryzen AI 300 thin and light mobile processors (codenamed "Strix Point"). Background Zen 5 was first officially mentioned during AMD's ''Ryzen Processors: One Year Later'' presentation on April 9, 2018. A roadmap shown during AMD's Financial Analyst Day on June 9, 2022 confirmed that Zen 5 and Zen 5c would be launching in 3nm and 4nm variants in 2024. The earliest details on the Zen 5 architecture promised a "re-pipelined front end and wide issue" with "integrated AI and Ma ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen 4

Zen 4 is the name for a CPU microarchitecture designed by AMD, released on September 27, 2022. It is the successor to Zen 3 and uses TSMC's N6 process for I/O dies, N5 process for CCDs, and N4 process for APUs. Zen 4 powers Ryzen 7000 performance desktop processors (codenamed "Raphael"), Ryzen 8000G series mainstream desktop APUs (codenamed "Phoenix"), and Ryzen Threadripper 7000 series HEDT and workstation processors (codenamed "Storm Peak"). It is also used in extreme mobile processors (codenamed "Dragon Range"), thin & light mobile processors (codenamed "Phoenix" and "Hawk Point"), as well as EPYC 8004/9004 server processors (codenamed "Siena", "Genoa" and "Bergamo"). Zen 4 is the first microarchitecture whose chips (Ryzen 7000) use the AM5 motherboard socket. Features Like its predecessor, Zen 4 in its Desktop Ryzen variants features one or two Core Complex Dies (CCDs) built on TSMC's 5 nm process and one I/O die built on 6 nm. Previously, the I/O die on Z ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen 3+

Zen 3 is the name for a CPU microarchitecture by AMD, released on November 5, 2020. It is the successor to Zen 2 and uses TSMC's 7 nm process for the chiplets and GlobalFoundries's 14 nm process for the I/O die on the server chips and 12 nm for desktop chips. Zen 3 powers Ryzen 5000 mainstream desktop processors (codenamed "Vermeer") and Epyc server processors (codenamed "Milan"). Zen 3 is supported on motherboards with 500 series chipsets; 400 series boards also saw support on select B450 / X470 motherboards with certain BIOSes. Zen 3 is the last microarchitecture before AMD switched to DDR5 memory and new sockets, which are AM5 for the desktop "Ryzen" chips alongside SP5 and SP6 for the EPYC server platform and sTRX8. According to AMD, Zen 3 has a 19% higher instructions per cycle (IPC) on average than Zen 2. On April 1, 2022, AMD released the new Ryzen 6000 series for laptops/mobile, using an improved Zen 3+ architecture featuring notable architectural improvements to pow ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

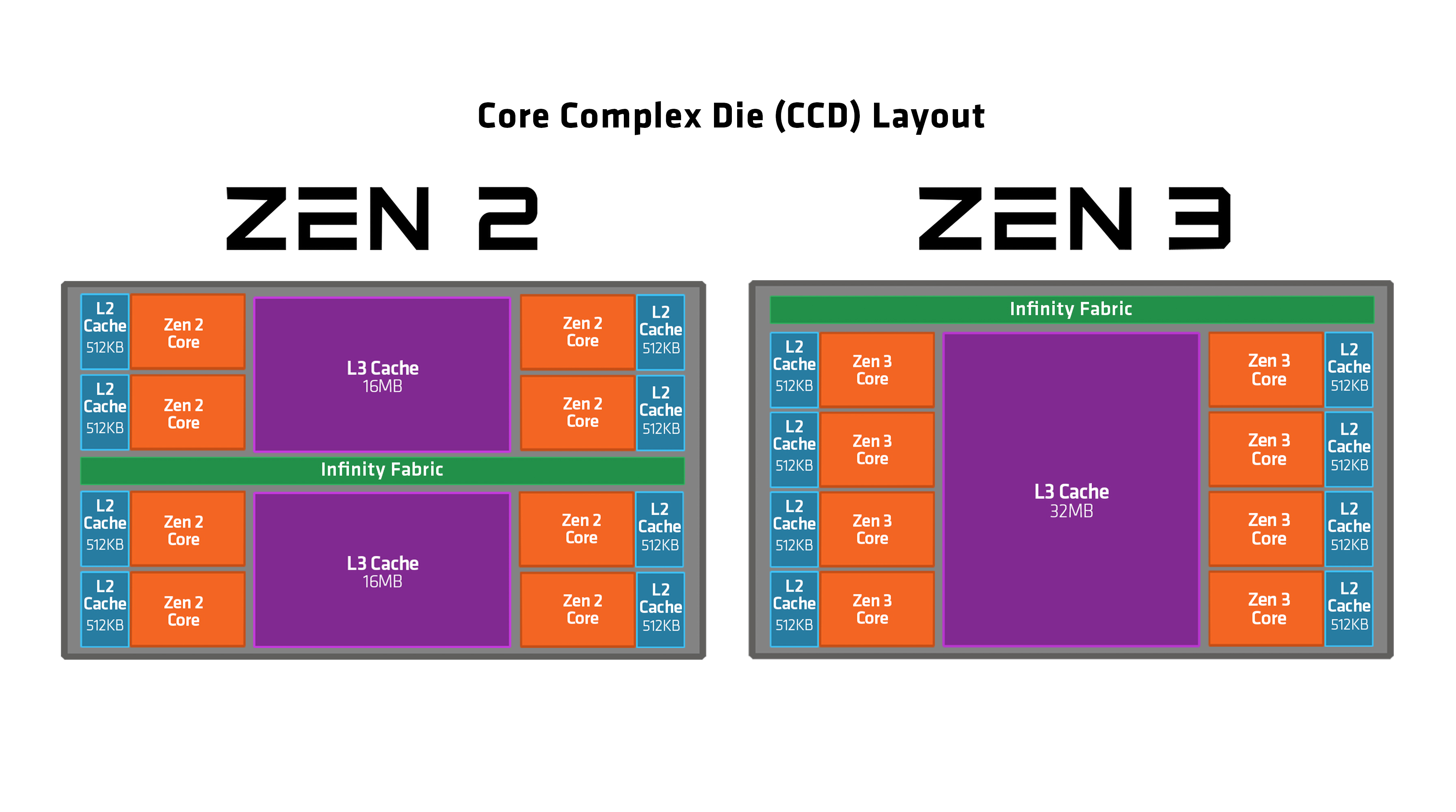

Zen 3

Zen 3 is the name for a CPU microarchitecture by AMD, released on November 5, 2020. It is the successor to Zen 2 and uses TSMC's 7 nm process, 7 nm process for the chiplets and GlobalFoundries's 14 nm process, 14 nm process for the I/O die on the server chips and 12 nm for desktop chips. Zen 3 powers Ryzen 5000 mainstream desktop processors (codenamed "Vermeer") and Epyc server processors (codenamed "Milan"). Zen 3 is supported on motherboards with List of AMD chipsets#AM4 chipsets, 500 series chipsets; 400 series boards also saw support on select B450 / X470 motherboards with certain BIOSes. Zen 3 is the last microarchitecture before AMD switched to DDR5 memory and new sockets, which are AM5 for the desktop "Ryzen" chips alongside SP5 and SP6 for the EPYC server platform and sTRX8. According to AMD, Zen 3 has a 19% higher instructions per cycle (IPC) on average than Zen 2. On April 1, 2022, AMD released the new Ryzen 6000 series for laptops/mobile, using an improved #Zen 3+, Zen ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hygon Dhyana

Epyc (stylized as EPYC) is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets. Epyc processors share the same microarchitecture as their regular desktop-grade counterparts, but have enterprise-grade features such as higher core counts, more PCI Express lanes, support for larger amounts of RAM, and larger cache memory. They also support multi-chip and dual-socket system configurations by using the Infinity Fabric interconnect. History *In March 2017, AMD announced plans to re-enter the server market with a platform based on the Zen microarchitecture, codenamed Naples, and officially revealed it under the brand name Epyc in May. That June AMD officially launched Epyc 7001 series processors, offering up to 32 cores per socket, and enabling performance that allowed Epyc to be competitive with the competing Intel Xe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen 2

Zen 2 is a computer processor microarchitecture by AMD. It is the successor of AMD's Zen and Zen+ microarchitectures, and is fabricated on the 7 nm MOSFET node from TSMC. The microarchitecture powers the third generation of Ryzen processors, known as Ryzen 3000 for the mainstream desktop chips (codename "Matisse"), Ryzen 4000U/H (codename "Renoir") and Ryzen 5000U (codename "Lucienne") for mobile applications, as Threadripper 3000 for high-end desktop systems, and as Ryzen 4000G for accelerated processing units (APUs). The Ryzen 3000 series CPUs were released on 7 July 2019, while the Zen 2-based Epyc server CPUs (codename "Rome") were released on 7 August 2019. An additional chip, the Ryzen 9 3950X, was released in November 2019. At CES 2019, AMD showed a Ryzen third-generation engineering sample that contained one chiplet with eight cores and 16 threads. AMD CEO Lisa Su also said to expect more than eight cores in the final lineup. At Computex 2019, AMD revealed that the Ze ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen+

Zen+ is the name for a computer processor microarchitecture by AMD. It is the successor to the first gen Zen microarchitecture, and was first released in April 2018, powering the second generation of Ryzen processors, known as Ryzen 2000 for mainstream desktop systems, Threadripper 2000 for high-end desktop setups and Ryzen 3000G (instead of 2000G) for accelerated processing units (APUs). Features Zen+ uses GlobalFoundries' 12 nm fabrication process, an optimization of the 14 nm process used for Zen, with only minor design rule changes. This means that the die sizes between Zen and Zen+ are identical as AMD chose to use the new smaller transistors to increase the amount of empty space, or " dark silicon", between the various features on the die. This was done to improve power efficiency & reduce thermal density to allow for higher clock speeds, rather than design an entirely new floorplan for a physically smaller die (which would have been significantly more work an ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen (first Generation)

Zen is the first iteration in the Zen (microarchitecture), Zen family of computer processor microarchitectures from AMD. It was first used with their Ryzen series of CPUs in February 2017. The first Zen-based preview system was demonstrated at Electronic Entertainment Expo 2016, E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017 and Zen-based AMD Accelerated Processing Unit, APUs arrived in November 2017. Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer (microarchitecture), Bulldozer architecture. Zen-based processors use a 14 nanometer, 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. Simultaneous multithreading, SMT has been introduced, allowing each core to run two thr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Puma (microarchitecture)

The Puma Family 16h is a low-power microarchitecture by AMD for its APUs. It succeeds the Jaguar as a second-generation version, targets the same market, and belongs to the same AMD architecture Family 16h. The ''Beema'' line of processors are aimed at low-power notebooks, and ''Mullins'' are targeting the tablet sector. Design The Puma cores use the same microarchitecture as Jaguar, and inherits the design: * Out-of-order execution and Speculative execution, up to 4 CPU cores * Two-way integer execution * Two-way 128-bit wide floating-point and packed integer execution * Integer hardware divider * Puma does not feature clustered multi-thread (CMT), meaning that there are no "modules" * Puma does not feature Heterogeneous System Architecture or zero-copy * 32 KiB instruction + 32 KiB data L1 cache per core * 1–2 MiB unified L2 cache shared by two or four cores * Integrated single channel memory controller supporting 64bit DDR3L * 3.1 mm2 area per core ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Jaguar (microarchitecture)

The AMD Jaguar Family 16h is a low-power microarchitecture designed by AMD. It is used in APUs succeeding the Bobcat Family microarchitecture in 2013 and being succeeded by AMD's Puma architecture in 2014. It is two-way superscalar and capable of out-of-order execution. It is used in AMD's Semi-Custom Business Unit as a design for custom processors and is used by AMD in four product families: ''Kabini'' aimed at notebooks and mini PCs, ''Temash'' aimed at tablets, ''Kyoto'' aimed at micro-servers, and the ''G-Series'' aimed at embedded applications. Both the PlayStation 4 and the Xbox One use SoCs based on the Jaguar microarchitecture, with more powerful GPUs than AMD sells in its own commercially available Jaguar APUs. Design * 32 KiB instruction + 32 KiB data L1 cache per core, L1 cache includes parity error detection * 16-way, 1–2 MiB unified L2 cache shared by two or four cores, L2 cache is protected from errors by the use of error correcting code * Out- ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |