|

Bulldozer (microarchitecture)

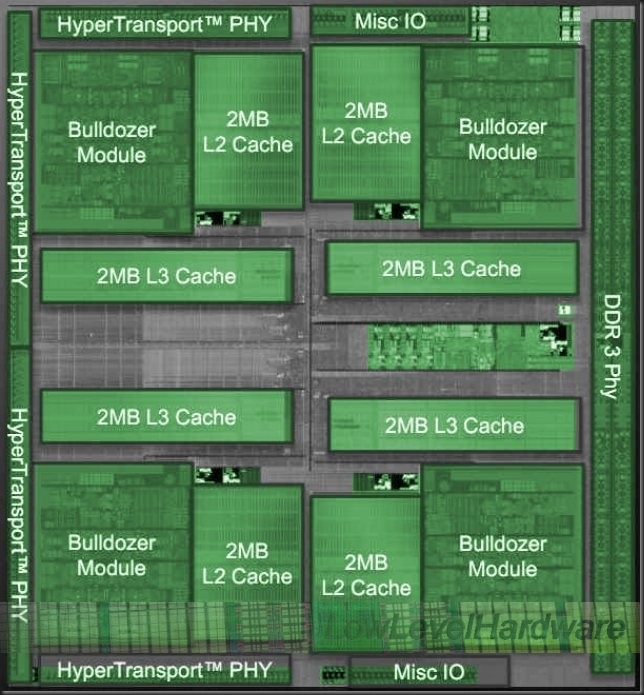

The AMD Bulldozer Family 15h is a microprocessor microarchitecture for the FX and Opteron line of processors, developed by AMD for the desktop and server markets. Bulldozer is the codename for this family of microarchitectures. It was released on October 12, 2011, as the successor to the K10 microarchitecture. Bulldozer is designed from scratch, not a development of earlier processors. The core is specifically aimed at computing products with TDPs of 10 to 125 watts. AMD claims dramatic performance-per-watt efficiency improvements in high-performance computing (HPC) applications with Bulldozer cores. The ''Bulldozer'' cores support most of the instruction sets implemented by Intel processors ( Sandy Bridge) available at its introduction (including SSSE3, SSE4.1, SSE4.2, AES, CLMUL, and AVX) as well as new instruction sets proposed by AMD; ABM, XOP, FMA4 and F16C. Only Bulldozer GEN4 (Excavator) supports AVX2 instruction sets. Overview According to AMD, Bul ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FX-4100

AMD FX is a discontinued series of List of AMD processors, AMD microprocessors for personal computers. The following is a list of AMD FX brand microprocessors. Some AMD Accelerated Processing Unit, APUs also carry an FX model name, but the term "FX" normally only refers to Central_processing_unit, CPUs which are not just APUs with the Graphics_processing_unit#Integrated_graphics, iGPU disabled. Features overview CPUs VS RF Template:AMD APU features, APU features table Desktop CPUs Athlon 64 Family (90–130 nm) These processors were the first AMD CPUs to use the "FX" designation and identified the chip as being higher-performance. The frequency multiplier was unlocked in these chips. SledgeHammer Core (130 nm) * Socket 940 * L1 cache: 64 kb + 64 kb (data + instruction) * L2 cache: 1024 kb (full speed) * Instruction sets: MMX (instruction set), MMX, Streaming SIMD Extensions, SSE, SSE2, 3DNow!, Enhanced 3DNow!, NX bit, x86-64, AMD64 FX-51 (2.2 GHz) and FX-53 (2 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSE4

SSE4 (Streaming SIMD Extensions 4) is a SIMD CPU instruction set used in the Intel Core microarchitecture and AMD K10 (K8L). It was announced on September 27, 2006, at the Fall 2006 Intel Developer Forum, with vague details in a white paper;Intel Streaming SIMD Extensions 4 (SSE4) Instruction Set Innovation , Intel. more precise details of 47 instructions became available at the Spring 2007 Intel Developer Forum in , in the presentation. SSE4 extended the SSE3 instruction set which was released in early 2004. All software using previous Intel SIMD instructio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

32 Nanometer

The "32 nm" node is the step following the "45 nm" process in CMOS (MOSFET) semiconductor device fabrication. "32-nanometre" refers to the average half-pitch (i.e., half the distance between identical features) of a memory cell at this technology level. Toshiba produced commercial 32 GiB NAND flash memory chips with the "32nm" process in 2009. Intel and AMD produced commercial microchips using the "32 nm" process in the early 2010s. IBM and the Common Platform also developed a "32 nm" high-κ metal gate process. Intel began selling its first "32 nm" processors using the Westmere architecture on 7 January 2010. Since at least 1997, "process nodes" have been named purely on a marketing basis, and have no relation to the dimensions on the integrated circuit; neither gate length, nor metal pitch, nor gate pitch on a "32nm" device is thirty-two nanometers. The "28 nm" node is an intermediate half-node die shrink based on the "32 nm" process. The "32 nm" process ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Digital Equipment Corporation

Digital Equipment Corporation (DEC ), using the trademark Digital, was a major American company in the computer industry from the 1960s to the 1990s. The company was co-founded by Ken Olsen and Harlan Anderson in 1957. Olsen was president until he was forced to resign in 1992, after the company had gone into precipitous decline. The company produced many different product lines over its history. It is best known for the work in the minicomputer market starting in the early 1960s. The company produced a series of machines known as the Programmed Data Processor, PDP line, with the PDP-8 and PDP-11 being among the most successful minis in history. Their success was only surpassed by another DEC product, the late-1970s VAX "supermini" systems that were designed to replace the PDP-11. Although a number of competitors had successfully competed with Digital through the 1970s, the VAX cemented the company's place as a leading vendor in the computer space. As microcomputers improved in t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Silicon On Insulator

In semiconductor manufacturing, silicon on insulator (SOI) technology is fabrication of silicon semiconductor devices in a layered silicon–insulator–silicon substrate, to reduce parasitic capacitance within the device, thereby improving performance. SOI-based devices differ from conventional silicon-built devices in that the silicon junction is above an electrical insulator, typically silicon dioxide or sapphire (these types of devices are called silicon on sapphire, or SOS). The choice of insulator depends largely on intended application, with sapphire being used for high-performance radio frequency (RF) and radiation-sensitive applications, and silicon dioxide for diminished short-channel effects in other microelectronics devices. The insulating layer and topmost silicon layer also vary widely with application. Industry need SOI technology is one of several manufacturing strategies to allow the continued miniaturization of microelectronic devices, colloquially referred to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GlobalFoundries

GlobalFoundries Inc. is a multinational semiconductor contract manufacturing and design company located in the Cayman Islands and headquartered in Malta, New York. Created by the divestiture of the manufacturing arm of AMD in March 2009, the company was privately owned by Mubadala Investment Company, a sovereign wealth fund of the United Arab Emirates, until an initial public offering (IPO) in October 2021. Mubadala remains the majority owner of the company with an 82% stake. The company manufactures integrated circuits on wafers designed for markets such as smart mobile devices, automotive, aerospace and defense, consumer internet of things (IoT) and for data centers and communications infrastructure. As of 2023, GlobalFoundries is the third-largest semiconductor foundry by revenue. It is the only one with operations in Singapore, the European Union, and the United States: one 200 mm and one 300 mm wafer fabrication plant in Singapore; one 300 mm plant in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AVX2

Advanced Vector Extensions (AVX, also known as Gesher New Instructions and then Sandy Bridge New Instructions) are SIMD extensions to the x86 instruction set architecture for microprocessors from Intel and Advanced Micro Devices (AMD). They were proposed by Intel in March 2008 and first supported by Intel with the Sandy Bridge microarchitecture shipping in Q1 2011 and later by AMD with the Bulldozer microarchitecture shipping in Q4 2011. AVX provides new features, new instructions, and a new coding scheme. AVX2 (also known as Haswell New Instructions) expands most integer commands to 256 bits and introduces new instructions. They were first supported by Intel with the Haswell microarchitecture, which shipped in 2013. AVX-512 expands AVX to 512-bit support using a new EVEX prefix encoding proposed by Intel in July 2013 and first supported by Intel with the Knights Landing co-processor, which shipped in 2016. In conventional processors, AVX-512 was introduced with Skylak ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Excavator (microarchitecture)

AMD Excavator Family 15h is a microarchitecture developed by AMD to succeed Steamroller Family 15h for use in AMD APU processors and normal CPUs. On October 12, 2011, AMD revealed Excavator to be the code name for the fourth-generation Bulldozer-derived core. The Excavator-based APU for mainstream applications is called ''Carrizo'' and was released in 2015. The ''Carrizo'' APU is designed to be HSA 1.0 compliant. An Excavator-based APU and CPU variant named ''Toronto'' for server and enterprise markets was also produced. Excavator was the final revision of the "Bulldozer" family, with two new microarchitectures replacing Excavator a year later. Excavator was succeeded by the x86-64 Zen architecture in early 2017. Architecture Excavator added hardware support for new instructions such as AVX2, BMI2 and RDRAND. Excavator is designed using High Density (aka "Thin") Libraries normally used for GPUs to reduce electric energy consumption and die size, delivering a 30 percent inc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

F16C

The F16C (previously/informally known as CVT16) instruction set is an x86 instruction set architecture extension which provides support for converting between half-precision and standard IEEE single-precision floating-point formats. History The CVT16 instruction set, announced by AMD on May 1, 2009, is an extension to the 128-bit SSE core instructions in the x86 and AMD64 instruction sets. CVT16 is a revision of part of the SSE5 instruction set proposal announced on August 30, 2007, which is supplemented by the XOP and FMA4 instruction sets. This revision makes the binary coding of the proposed new instructions more compatible with Intel's AVX instruction extensions, while the functionality of the instructions is unchanged. In recent documents, the name F16C is formally used in both Intel and AMD x86-64 architecture specifications. Technical information There are variants that convert four floating-point values in an XMM register or 8 floating-point values in a YMM re ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FMA4 Instruction Set

The FMA instruction set is an extension to the 128- and 256-bit Streaming SIMD Extensions instructions in the x86 microprocessor instruction set to perform fused multiply–add (FMA) operations. There are two variants: * FMA4 is supported in AMD processors starting with the Bulldozer architecture. FMA4 was performed in hardware before FMA3 was. Support for FMA4 has been removed since Zen 1. * FMA3 is supported in AMD processors starting with the Piledriver architecture and Intel starting with Haswell processors and Broadwell processors since 2014. Instructions FMA3 and FMA4 instructions have almost identical functionality, but are not compatible. Both contain fused multiply–add (FMA) instructions for floating-point scalar and SIMD operations, but FMA3 instructions have three operands, while FMA4 ones have four. The FMA operation has the form ''d'' = round(''a'' · ''b'' + ''c''), where the round function performs a rounding to allow the result to fit within the destination r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

XOP Instruction Set

The XOP (''eXtended Operations'') instruction set, announced by AMD on May 1, 2009, is an extension to the 128-bit SSE core instructions in the x86 and AMD64 instruction set for the Bulldozer processor core, which was released on October 12, 2011. However AMD removed support for XOP from Zen (microarchitecture) onward. The XOP instruction set contains several different types of vector instructions since it was originally intended as a major upgrade to SSE. Most of the instructions are integer instructions, but it also contains floating point permutation and floating point fraction extraction instructions. See the index for a list of instruction types. History XOP is a revised subset of what was originally intended as SSE5. It was changed to be similar but not overlapping with AVX, parts that overlapped with AVX were removed or moved to separate standards such as FMA4 (floating-point vector multiply–accumulate) and CVT16 ( Half-precision floating-point conversion imp ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bit Manipulation Instruction Sets

Bit manipulation instructions sets (BMI sets) are extensions to the x86 instruction set architecture for microprocessors from Intel and AMD. The purpose of these instruction sets is to improve the speed of bit manipulation. All the instructions in these sets are non-SIMD and operate only on general-purpose registers. There are two sets published by Intel: BMI (now referred to as BMI1) and BMI2; they were both introduced with the Haswell microarchitecture with BMI1 matching features offered by AMD's ABM instruction set and BMI2 extending them. Another two sets were published by AMD: ABM (''Advanced Bit Manipulation'', which is also a subset of SSE4a implemented by Intel as part of SSE4.2 and BMI1), and TBM (''Trailing Bit Manipulation'', an extension introduced with Piledriver-based processors as an extension to BMI1, but dropped again in Zen-based processors). ABM (Advanced Bit Manipulation) AMD was the first to introduce the instructions that now form Intel's BMI1 as part ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |