Zen 3 on:

[Wikipedia]

[Google]

[Amazon]

Zen 3 is the

File:AMD@7nm(12nmIOD)@Zen3@Vermeer@Ryzen 5 5600X@100-000000064 BG 2042SUS 9JF6228V00014 DSCx2.jpg, A de-lidded Ryzen 5 5600X. Only one CCD is present. The contacts for a second CCD are visible.

File:AMD@7nm(12nmIOD)@Zen3@Vermeer@Ryzen 5 5600X@100-000000064 BG 2042SUS 9JF6228V00014 DSCx4@IR.jpg, Close-up of the CCD, taken under infrared lighting. This die was damaged by the de-lidding process.

File:AMD@7nm(12nmIOD)@Zen3@Vermeer@Ryzen 5 5600X@100-000000064 BG 2042SUS 9JF6228V00014 DSCx3@IR.jpg, Close-up of the I/O die

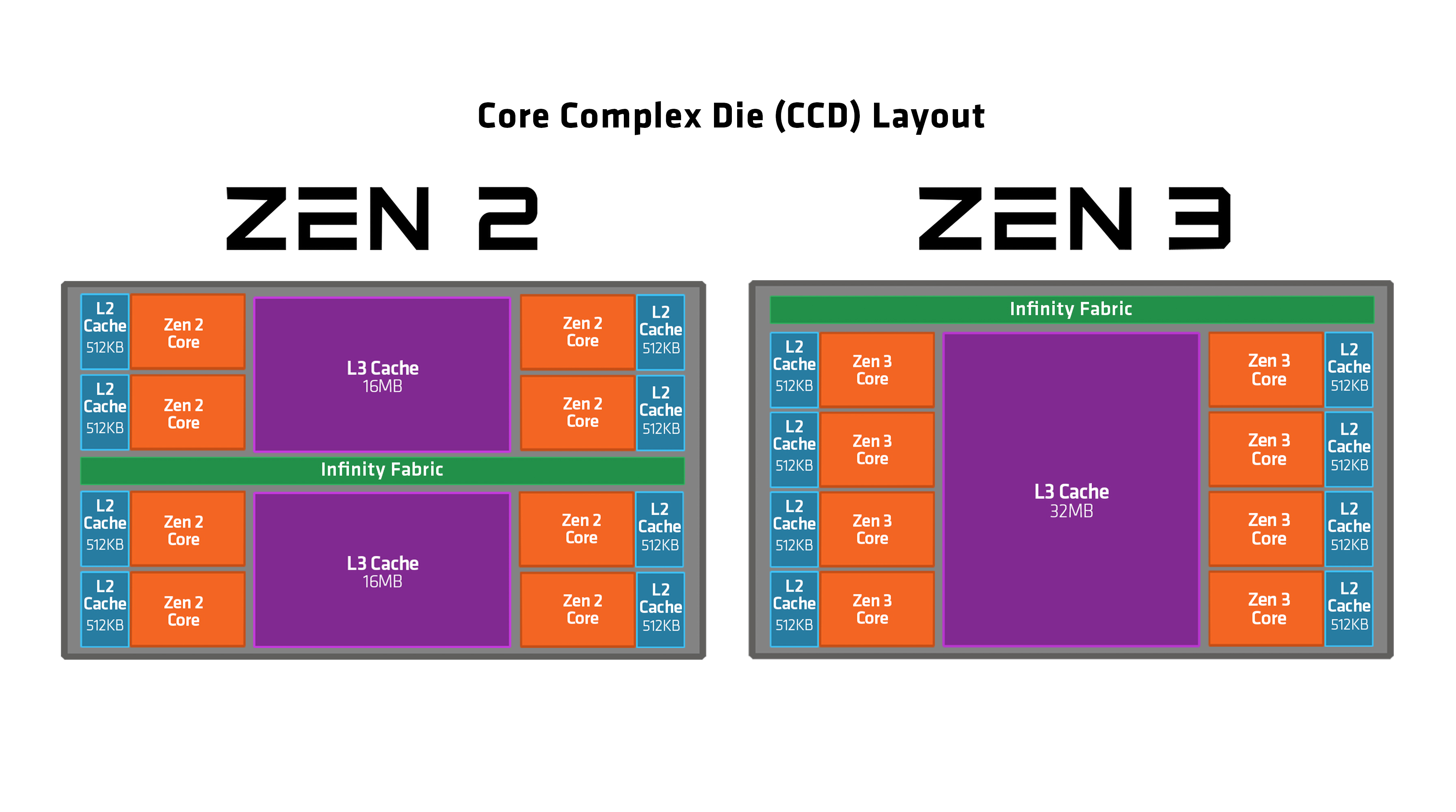

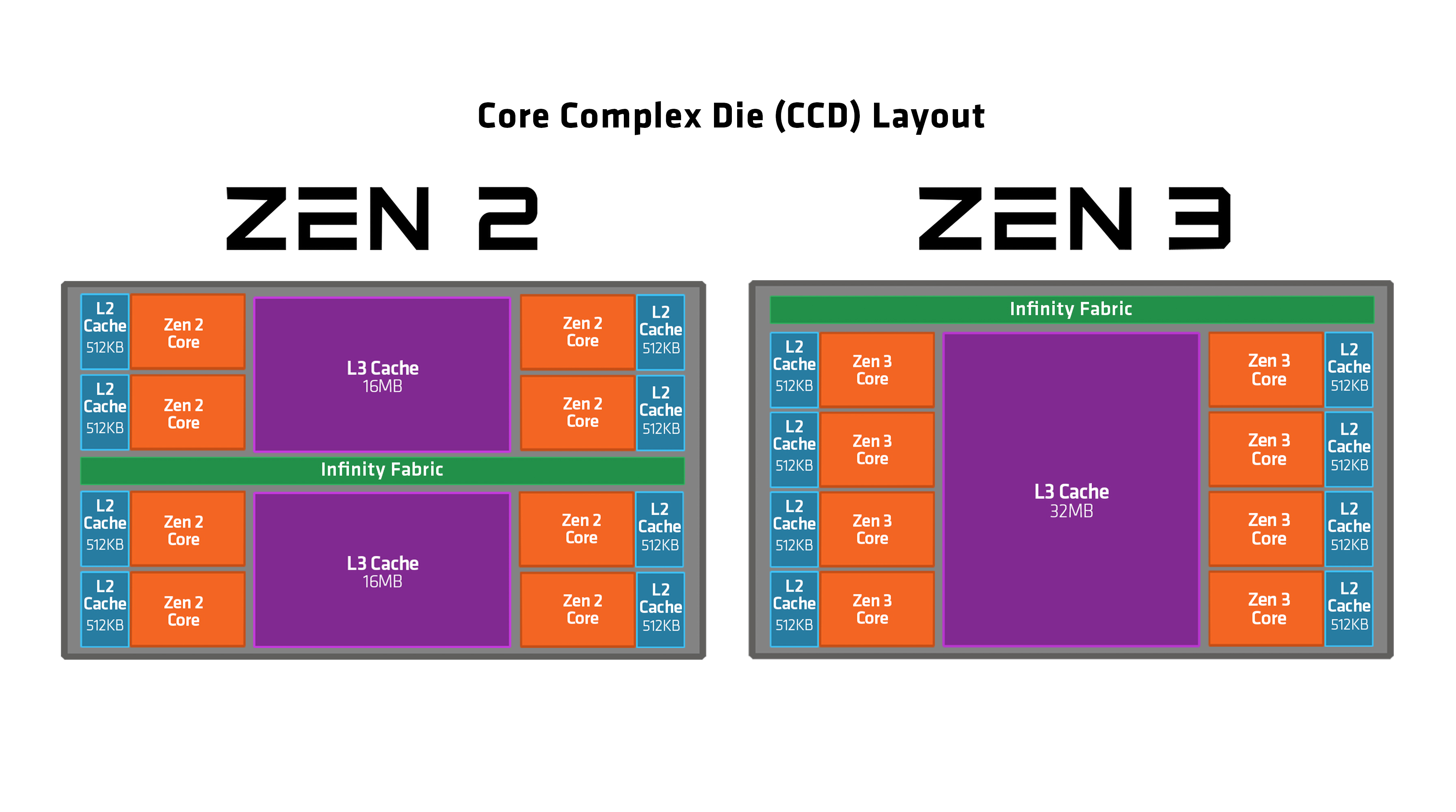

In Zen 3, a single 32MB L3 cache pool is shared among all 8 cores in a chiplet, vs. Zen 2's two 16MB pools each shared among 4 cores in a core complex, of which there were two per chiplet. This new arrangement improves the cache hit rate as well as performance in situations that require cache data to be exchanged among cores, but increases cache latency from 39 cycles in Zen 2 to 46 clock cycles and halves per-core cache bandwidth, although both problems are partially mitigated by higher clock speeds. Total cache bandwidth on all 8 cores combined remains the same due to power consumption concerns. L2 cache capacity and latency remain the same at 512KB and 12 cycles. All cache read and write operations are done at 32 bytes per cycle.

Ryzen 6000 series, which was later released on April 1, 2022, introduced PCIe 4.0 and

Zen 3 has made the following improvements over Zen 2:

* An increase of 19% in

Zen 3 has made the following improvements over Zen 2:

* An increase of 19% in

codename

A code name, call sign or cryptonym is a Code word (figure of speech), code word or name used, sometimes clandestinely, to refer to another name, word, project, or person. Code names are often used for military purposes, or in espionage. They may ...

for a CPU

A central processing unit (CPU), also called a central processor, main processor or just processor, is the electronic circuitry that executes instructions comprising a computer program. The CPU performs basic arithmetic, logic, controlling, and ...

microarchitecture

In computer engineering, microarchitecture, also called computer organization and sometimes abbreviated as µarch or uarch, is the way a given instruction set architecture (ISA) is implemented in a particular processor. A given ISA may be impl ...

by AMD

Advanced Micro Devices, Inc. (AMD) is an American multinational semiconductor company based in Santa Clara, California, that develops computer processors and related technologies for business and consumer markets. While it initially manufactur ...

, released on November 5, 2020. It is the successor to Zen 2

Zen 2 is a computer processor microarchitecture by AMD. It is the successor of AMD's Zen and Zen+ microarchitectures, and is fabricated on the 7 nanometer MOSFET node from TSMC. The microarchitecture powers the third generation of Ryzen proces ...

and uses TSMC

Taiwan Semiconductor Manufacturing Company Limited (TSMC; also called Taiwan Semiconductor) is a Taiwanese multinational corporation, multinational semiconductor contract manufacturing and design company. It is the world's most valuable semicon ...

's 7 nm

In semiconductor manufacturing, the International Technology Roadmap for Semiconductors defines the 7 nm process as the MOSFET technology node following the 10 nm node. It is based on FinFET (fin field-effect transistor) technology, ...

process for the chiplets and GlobalFoundries

GlobalFoundries Inc. (GF or GloFo) is a multinational semiconductor contract manufacturing and design company incorporated in the Cayman Islands and headquartered in Malta, New York. Created by the divestiture of the manufacturing arm of AMD, th ...

's 14 nm

The 14 nm process refers to the MOSFET technology node that is the successor to the 22nm (or 20nm) node. The 14nm was so named by the International Technology Roadmap for Semiconductors (ITRS). Until about 2011, the node following 22nm was expe ...

process for the I/O die on the server chips and 12 nm for desktop chips. Zen 3 powers Ryzen 5000

Ryzen ( ) is a brand of multi-core processor, multi-core x86-64 microprocessors designed and marketed by AMD for desktop, mobile, server, and embedded platforms based on the Zen (microarchitecture), Zen microarchitecture. It consists of centr ...

mainstream desktop processors (codenamed "Vermeer") and Epyc

Epyc is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets. Epyc processors share t ...

server processors (codenamed "Milan"). Zen 3 is supported on motherboards with 500 series chipsets; 400 series boards also saw support on select B450 / X470 motherboards with certain BIOSes. Zen 3 is expected to be the last microarchitecture before AMD switches to DDR5

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) ...

memory and new sockets. According to AMD, Zen 3 has a 19% higher instructions per cycle

In computer architecture, instructions per cycle (IPC), commonly called instructions per clock is one aspect of a processor's performance: the average number of instructions executed for each clock cycle. It is the multiplicative inverse of cycl ...

(IPC) on average than Zen 2

Zen 2 is a computer processor microarchitecture by AMD. It is the successor of AMD's Zen and Zen+ microarchitectures, and is fabricated on the 7 nanometer MOSFET node from TSMC. The microarchitecture powers the third generation of Ryzen proces ...

. On April 1, 2022, AMD released the new Ryzen 6000 series for the laptop, using an improved "Zen 3+" architecture, bringing RDNA 2 graphics integrated in a APU to the PC for the first time. On April 20, 2022, AMD also released the Ryzen 7 5800X3D, which increases the single threading performance by another 15% in gaming by using, for the first time in a PC product, 3D vertically stacked L3 cache.

Features

Zen 3 is a significant incremental improvement over its predecessors, with an IPC increase of 19%, and being capable of reaching higher clock speeds. Like Zen 2, Zen 3 is composed of up to 2 core complex dies (CCD) along with a separate IO die containing the I/O components. A Zen 3 CCD is composed of a single core complex (CCX) containing 8 CPU cores and 32MB of sharedL3 cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which ...

, this is in contrast to Zen 2 where each CCD is composed of 2 CCX, each containing 4 cores each as well as 16MB of L3 cache. The new configuration allows all 8 cores of the CCX to directly communicate with each other and the L3 Cache instead of having to use the IO die through the Infinity Fabric

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/parallel high-bandwidth, low- latency point-to-point link that was introduced on April 2 ...

.

Zen 3 (along with AMD's RDNA2 GPUs) were also the first implementation of Resizable BAR

Bar or BAR may refer to:

Food and drink

* Bar (establishment), selling alcoholic beverages

* Candy bar

* Chocolate bar

Science and technology

* Bar (river morphology), a deposit of sediment

* Bar (tropical cyclone), a layer of cloud

* Bar (u ...

, an optional feature introduced in PCIe2.0, that was branded as ''Smart Access Memory'' (SAM). This technology allows CPU to directly access all of compatible video card's VRAM

Video random access memory (VRAM) is dedicated computer memory used to store the pixels and other graphics data as a framebuffer to be rendered on a computer monitor. This is often different technology than other computer memory, to facilitate b ...

. Intel and Nvidia have since implemented this feature as well.

DDR5

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) ...

/LPDDR5

Low-Power Double Data Rate (LPDDR), also known as LPDDR SDRAM, is a type of synchronous dynamic random-access memory that consumes less power and is targeted for mobile computers and devices such as mobile phones. Older variants are also known a ...

for the first time in an APU for the laptop and also introduced RDNA2 APU graphics to the PC.

On April 20, 2022, AMD released the last member of the AM4 family, the 5800X3D. It features, for the first time in a desktop PC product, 3D-stacked vertical L3 cache, which in the size of an extra 64 MB on top of the usual 32 MB increases the total amount to 96 MB and brings tremendous performance improvements for gaming, rivalling the newest processors of the competition while being much more power efficient.

Improvements

Zen 3 has made the following improvements over Zen 2:

* An increase of 19% in

Zen 3 has made the following improvements over Zen 2:

* An increase of 19% in instructions per clock

In computer architecture, instructions per cycle (IPC), commonly called instructions per clock is one aspect of a processor's performance: the average number of instructions executed for each clock cycle. It is the multiplicative inverse of cycl ...

* The base core chiplet

A chiplet is a tiny integrated circuit (IC) that contains a well-defined subset of functionality. It is designed to be combined with other chiplets on an interposer in a single package. A set of chiplets can be implemented in a mix-and-match "LEGO ...

has a single eight-core complex (versus two four-core complexes in Zen 2)

* A unified 32MB L3 cache pool equally available to all 8 cores in a chiplet, vs Zen 2's two 16MB pools each shared among 4 cores in a core complex.

**On mobile: A unified 16MB L3

*A unified 8-core CCX (from 2x 4-Core CCX per CCD)

* Increased branch prediction

In computer architecture, a branch predictor is a digital circuit that tries to guess which way a branch (e.g., an if–then–else structure) will go before this is known definitively. The purpose of the branch predictor is to improve the flow ...

bandwidth. L1 branch target buffer size increased to 1024 entries (vs 512 in Zen 2)

*New Instructions

** VAES - 256-bit Vector AES instructions

** INVLPGB - Broadcast TLB flushing

** CET_SS - Control-flow Enforcement Technology

Control-flow integrity (CFI) is a general term for computer security techniques that prevent a wide variety of malware attacks from redirecting the flow of execution (the control flow) of a program.

Techniques

Associated techniques include code-p ...

/ Shadow Stack

A shadow is a dark area where light from a light source is blocked by an opaque object. It occupies all of the three-dimensional volume behind an object with light in front of it. The cross section of a shadow is a two-dimensional silhouette, o ...

* Improved integer units

** 96 entry integer scheduler (up from 92)

** 192 entry physical register file (up from 180)

** 10 issue per cycle (up from 7)

** 256 entry reorder-buffer (up from 224)

** fewer cycles for DIV/IDIV ops (10...20 from 16...46)

* Improved floating point units

** 6 µOP dispatch width (up from 4)

** FMA latency reduced by 1 cycle (down from 5 to 4)

* RDNA 2 graphics with up to 12 Compute Units (up from 8) in Ryzen 6000 series

* DDR5/LPDDR5 support (Ryzen 6000)

* Additional 64MB 3D vertically stacked dense library L3 cache (5800X3D)

Feature tables

CPUs

CPU features tableAPUs

APU features tableProducts

200px, AMD Ryzen 7 5800X On October 8, 2020, AMD announced four Zen 3-based desktop Ryzen processors, consisting of one Ryzen 5, one Ryzen 7, and two Ryzen 9 CPUs and featuring between 6 and 16 cores.Desktop CPUs

The Ryzen 5000 series desktop CPUs are codenamed ''Vermeer'', except for the Ryzen 5 5500, which is a ''Cezanne''APU

APU or Apu may refer to:

Film and television

* ''The Apu Trilogy'', a series of three Bengali films, directed by Satyajit Ray, with the fictional character Apu Roy, comprising:

** ''Pather Panchali'' (''Song of the Little Road'') (1955), the first ...

with its integrated GPU

A graphics processing unit (GPU) is a specialized electronic circuit designed to manipulate and alter memory to accelerate the creation of images in a frame buffer intended for output to a display device. GPUs are used in embedded systems, mobil ...

disabled. Meanwhile the Ryzen Threadripper Pro 5000 series were codenamed ''Chagall''.

Desktop APUs

Cezanne

Mobile APUs

Cezanne

Barceló

Rembrandt

Embedded CPUs

Server CPUs

TheEpyc

Epyc is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets. Epyc processors share t ...

server line of chips based on Zen 3 is named Milan and is the final generation of chips using the SP3 socket. Epyc Milan was released on March 15, 2021.

References

{{AMD processor roadmap AMD microarchitectures AMD x86 microprocessors Computer-related introductions in 2020 X86 microarchitectures