|

DDR5

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth (" double data rate") interface. Released to the market in 2014, it is a variant of dynamic r ..., DDR5 was planned to reduce power consumption, while doubling Bandwidth (computing), bandwidth. The standard, originally targeted for 2018, was released on July 14, 2020. A new feature called Decision Feedback Equalization (DFE) enables I/O speed scalability for higher bandwidth and performance improvement. DDR5 supports more Bandwidth (computing), bandwidth than its predecessor, DDR4 SDRAM, DDR4, with 4.8 gigabits per second possible, but not shipping at launch. DDR5 has about the same memory timings, latency as DDR4 and DDR3. DDR5 octuples the maximum DIMM capac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LPDDR

Low-Power Double Data Rate (LPDDR), also known as LPDDR SDRAM, is a type of synchronous dynamic random-access memory that consumes less power and is targeted for mobile computers and devices such as mobile phones. Older variants are also known as Mobile DDR, and abbreviated as mDDR. Modern LPDDR SDRAM is distinct from DDR SDRAM, with various differences that make the technology more appropriate for the mobile application. LPDDR technology standards are developed independently of DDR standards, with LPDDR4X and even LPDDR5 for example being implemented prior to DDR5 SDRAM and offering far higher data rates than DDR4 SDRAM. Bus width In contrast with standard SDRAM, used in stationary devices and laptops and usually connected over a 64-bit wide memory bus, LPDDR also permits 16- or 32-bit wide channels. The "E" versions mark enhanced versions of the specifications. They formalize overclocking the memory array up to 266 MHz for a 33% performance boost. Memory modules impleme ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LPDDR5

Low-Power Double Data Rate (LPDDR), also known as LPDDR SDRAM, is a type of synchronous dynamic random-access memory that consumes less power and is targeted for mobile computers and devices such as mobile phones. Older variants are also known as Mobile DDR, and abbreviated as mDDR. Modern LPDDR SDRAM is distinct from DDR SDRAM, with various differences that make the technology more appropriate for the mobile application. LPDDR technology standards are developed independently of DDR standards, with LPDDR4X and even LPDDR5 for example being implemented prior to DDR5 SDRAM and offering far higher data rates than DDR4 SDRAM. Bus width In contrast with standard SDRAM, used in stationary devices and laptops and usually connected over a 64-bit wide memory bus, LPDDR also permits 16- or 32-bit wide channels. The "E" versions mark enhanced versions of the specifications. They formalize overclocking the memory array up to 266 MHz for a 33% performance boost. Memory modules imple ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SDRAM

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions only delayed by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memory a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Synchronous Dynamic Random-access Memory

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions only delayed by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memory a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Synchronous Dynamic Random-access Memory

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions only delayed by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memory a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DIMM

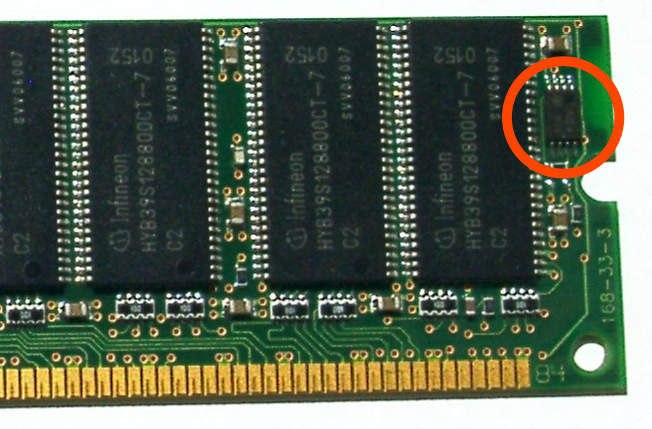

A DIMM () (Dual In-line Memory Module), commonly called a RAM stick, comprises a series of dynamic random-access memory integrated circuits. These memory modules are mounted on a printed circuit board and designed for use in personal computers, workstations, printers, and servers. They are the predominant method for adding memory into a computer system. The vast majority of DIMMs are standardized through JEDEC standards, although there are proprietary DIMMs. DIMMs come in a variety of speeds and sizes, but generally are one of two lengths - PC which are and laptop (SO-DIMM) which are about half the size at . History DIMMs (Dual In-line Memory Module) were a 1990s upgrade for SIMMs (Single In-line Memory Modules) as Intel P5-based Pentium processors began to gain market share. The Pentium had a 64-bit bus width, which would require SIMMs installed in matched pairs in order to populate the data bus. The processor would then access the two SIMMs in parallel. DIMMs were i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Serial Presence Detect

In computing, serial presence detect (SPD) is a standardized way to automatically access information about a memory module. Earlier 72-pin SIMMs included five pins that provided five bits of ''parallel presence detect'' (PPD) data, but the 168-pin DIMM standard changed to a serial presence detect to encode much more information. When an ordinary modern computer is turned on, it starts by doing a power-on self-test (POST). Since about the mid-1990s, this process includes automatically configuring the hardware currently present. SPD is a memory hardware feature that makes it possible for the computer to know what memory is present, and what memory timings to use to access the memory. Some computers adapt to hardware changes completely automatically. In most cases, there is a special optional procedure for accessing BIOS parameters, to view and potentially make changes in settings. It may be possible to control how the computer uses the memory SPD data—to choose settings, sel ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ryzen

Ryzen ( ) is a brand of multi-core x86-64 microprocessors designed and marketed by AMD for desktop, mobile, server, and embedded platforms based on the Zen microarchitecture. It consists of central processing units (CPUs) marketed for mainstream, enthusiast, server, and workstation segments and accelerated processing units (APUs) marketed for mainstream and entry-level segments and embedded systems applications. AMD announced a new series of processors on December 13, 2016, named "Ryzen", and delivered them in Q1 2017, the first of several generations. The 1000 series featured up to eight cores and 16 threads, with a 52% instructions per cycle (IPC) increase over their prior CPU products. The second generation of Ryzen processors, the Ryzen 2000 series, released in April 2018, featured the Zen+ microarchitecture, a 12 nm process (GlobalFoundries); the aggregate performance increased 10% (of which approximately 3% was IPC, 6% was frequency); most importantly, Zen+ fixed ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR4 SDRAM

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth (" double data rate") interface. Released to the market in 2014, it is a variant of dynamic random-access memory (DRAM), of which some have been in use since the early 1970s, and a higher-speed successor to the DDR2 and DDR3 technologies. DDR4 is not compatible with any earlier type of random-access memory (RAM) due to different signaling voltage and physical interface, besides other factors. DDR4 SDRAM was released to the public market in Q2 2014, focusing on ECC memory, while the non-ECC DDR4 modules became available in Q3 2014, accompanying the launch of Haswell-E processors that require DDR4 memory. Features The primary advantages of DDR4 over its predecessor, DDR3, include higher module density and lower voltage requirements, coupled with higher data rate transfer speeds. The DDR4 standard allows for DIMMs of up ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sapphire Rapids

Sapphire Rapids is a List of Intel codenames, codename for Intel's server (fourth generation Xeon Scalable) and workstation processors based on 7 nm process, Intel 7. Sapphire Rapids was intended as part of the Eagle Stream server platform. In addition, it will be powering Aurora (supercomputer), Aurora, an exascale computing, exascale supercomputer in the United States, at Argonne National Laboratory. History Sapphire Rapids has been a long-standing Intel project in development for over five years and has been subjected to many delays. Sapphire Rapids was first announced by Intel at their Investor Meeting in May 2019 with the intention of Sapphire Rapids succeeding Ice Lake (microprocessor), Ice Lake in 2021. Intel again announced details on Sapphire Rapids in their August 2021 Architecture Day presentation with no mention of a launch date. Intel CEO Pat Gelsinger tacitly blamed the previous Intel leadership as a reason for Sapphire Rapid's many delays. One industry analyst fi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Alder Lake

Alder Lake is Intel's codename for the 12th generation of Intel Core processors based on a hybrid architecture utilizing Golden Cove performance cores and Gracemont efficient cores. It is fabricated using Intel's Intel 7 process, previously referred to as Intel 10 nm Enhanced SuperFin (10ESF). The 10ESF has a 10%-15% boost in performance over the 10SF used in the mobile Tiger Lake processors. Intel officially announced 12th Gen Intel Core CPUs on October 27, 2021. Intel officially announced 12th Gen Intel Core mobile CPUs and non-K series desktop CPUs on January 4, 2022. Intel officially announced the launch of Alder Lake-P and -U series on February 23, 2022, and Alder Lake-HX series on May 10, 2022. History Fabricated using Intel's Intel 7 process, which was previously referred to as Intel 10 nm Enhanced SuperFin (10ESF), Intel officially announced 12th Gen Intel Core CPUs on October 27, 2021. Intel then officially announced 12th Gen Intel Core mobile CPUs and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Raptor Lake

Raptor Lake is Intel's codename for the 13th-generation of Intel Core processors based on a hybrid architecture, utilizing Raptor Cove performance cores and Gracemont efficient cores. Raptor Lake launched on October 20, 2022. Mobile versions are expected to be released by the end of the year. Like Alder Lake, Raptor Lake is fabricated using Intel's Intel 7 process. At Intel's Investor Meeting 2022, it was confirmed that Raptor Lake would feature up to 24 cores (8 performance cores plus 16 efficient cores) and 32 threads and is socket compatible with Alder Lake systems (LGA 1700). The company spokesman revealed that Raptor Lake was conjured in the last-minute, to benefit from all the process improvements before Meteor Lake arrives since the next microarchitecture was not ready on time. Raptor Lake competes with the AMD Ryzen 7000 series that was launched about one month earlier on September 27, 2022. Features CPU * Cores ** Raptor Cove performance cores (P-core) ** ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |