|

Zen 3

Zen 3 is the name for a CPU microarchitecture by AMD, released on November 5, 2020. It is the successor to Zen 2 and uses TSMC's 7 nm process, 7 nm process for the chiplets and GlobalFoundries's 14 nm process, 14 nm process for the I/O die on the server chips and 12 nm for desktop chips. Zen 3 powers Ryzen 5000 mainstream desktop processors (codenamed "Vermeer") and Epyc server processors (codenamed "Milan"). Zen 3 is supported on motherboards with List of AMD chipsets#AM4 chipsets, 500 series chipsets; 400 series boards also saw support on select B450 / X470 motherboards with certain BIOSes. Zen 3 is the last microarchitecture before AMD switched to DDR5 memory and new sockets, which are AM5 for the desktop "Ryzen" chips alongside SP5 and SP6 for the EPYC server platform and sTRX8. According to AMD, Zen 3 has a 19% higher instructions per cycle (IPC) on average than Zen 2. On April 1, 2022, AMD released the new Ryzen 6000 series for laptops/mobile, using an improved #Zen 3+, Zen ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR5

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM, DDR5 was planned to reduce power consumption, while doubling bandwidth. The standard, originally targeted for 2018, was released on July 14, 2020. A new feature called Decision Feedback Equalization (DFE) enables input/output (I/O) speed scalability for higher bandwidth and performance improvement. DDR5 has about the same latency as DDR4 and DDR3. DDR5 octuples the maximum DIMM capacity from 64 GB to 512 GB. DDR5 also has higher frequencies than DDR4, up to 9600 MT/s is currently possible, 8200 MT/s translates into around 66 GB/s of bandwidth. Using liquid nitrogen 13000 MT/s speeds were achieved. Rambus announced a working DDR5 dual in-line memory module (DIMM) in September 2017. On November 15, 2018, SK Hynix announced completion of its first DDR5 RAM chip; running at 5.2 GT/s at 1.1 V. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Branch Prediction

In computer architecture, a branch predictor is a digital circuit that tries to guess which way a branch (e.g., an if–then–else structure) will go before this is known definitively. The purpose of the branch predictor is to improve the flow in the instruction pipeline. Branch predictors play a critical role in achieving high performance in many modern pipelined microprocessor architectures. Two-way branching is usually implemented with a conditional jump instruction. A conditional jump can either be "taken" and jump to a different place in program memory, or it can be "not taken" and continue execution immediately after the conditional jump. It is not known for certain whether a conditional jump will be taken or not taken until the condition has been calculated and the conditional jump has passed the execution stage in the instruction pipeline (see fig. 1). Without branch prediction, the processor would have to wait until the conditional jump instruction has passed the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Chiplet

A chiplet is a tiny integrated circuit (IC) that contains a well-defined subset of functionality. It is designed to be combined with other chiplets on an interposer in a single package to create a complex component such as a computer processor. Each chiplet in a computer processor provides only a portion of the processor's total functionality. A set of chiplets can be implemented in a mix-and-match "Lego-like" assembly. This provides several advantages over a traditional system on chip (SoC) which is monolithic as it comprises a single silicon die: * Reusable IP (intellectual property): the same chiplet can be used in many different devices * Heterogeneous integration: chiplets can be fabricated with different processes, materials, and nodes, each optimized for its particular function * Known good die: chiplets can be tested before assembly, improving the yield of the final device. Multiple chiplets working together in a single integrated circuit may be called a multi-chip modul ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instructions Per Cycle

In computer architecture, instructions per cycle (IPC), commonly called instructions per clock, is one aspect of a processor's performance: the average number of instructions executed for each clock cycle. It is the multiplicative inverse of cycles per instruction. Explanation While early generations of CPUs carried out all the steps to execute an instruction sequentially, modern CPUs can do many things in parallel. As it is impossible to just keep doubling the speed of the clock, instruction pipelining and superscalar processor design have evolved so CPUs can use a variety of execution units in parallel - looking ahead through the incoming instructions in order to optimise them. This leads to the ''instructions per cycle completed'' being much higher than 1 and is responsible for much of the speed improvements in subsequent CPU generations. Calculation of IPC The calculation of IPC is done through running a set piece of code, calculating the number of machine-level inst ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

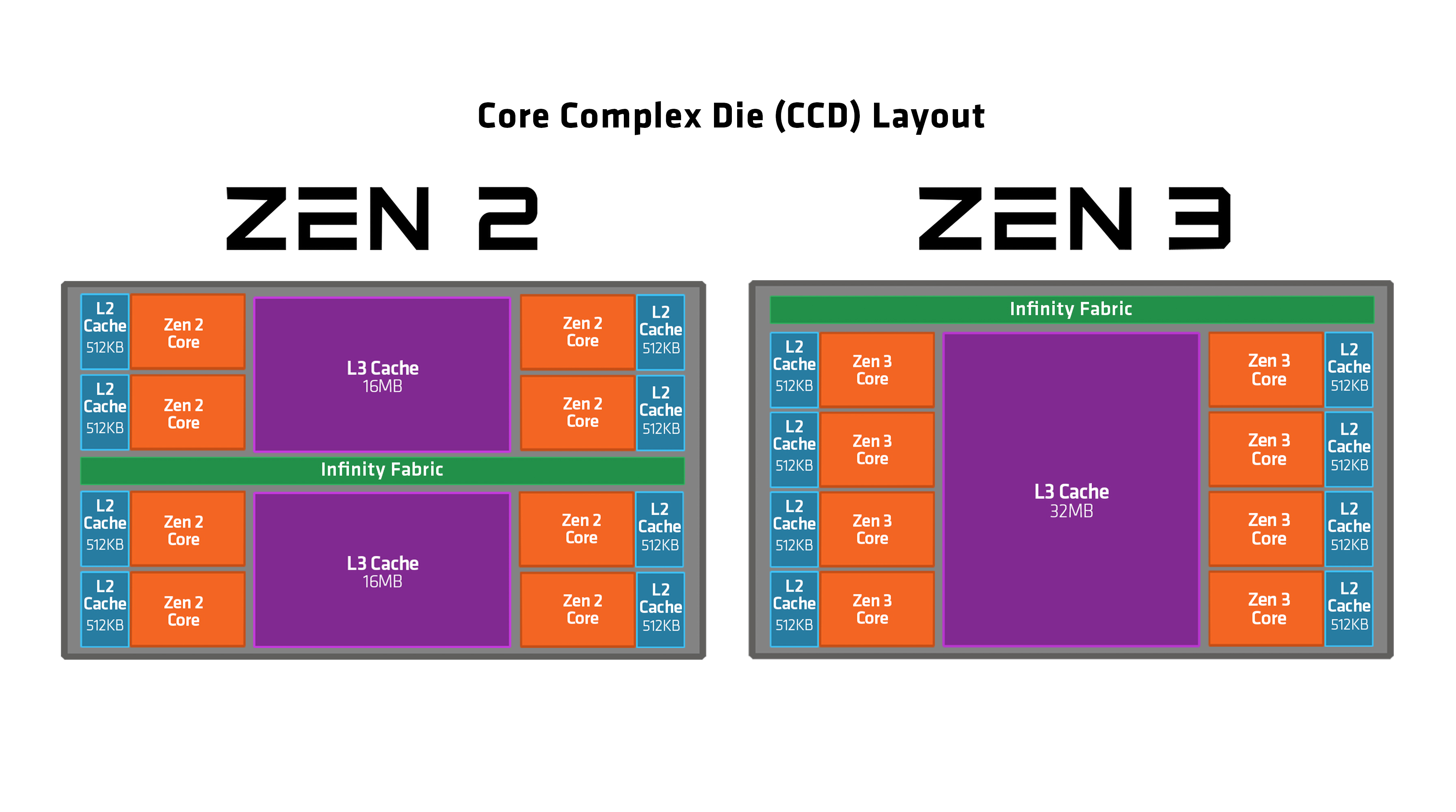

Zen 2 Vs Zen 3 CCD Layout

Zen (; from Chinese: ''Chán''; in Korean: ''Sŏn'', and Vietnamese: ''Thiền'') is a Mahayana Buddhist tradition that developed in China during the Tang dynasty by blending Indian Mahayana Buddhism, particularly Yogacara and Madhyamaka philosophies, with Chinese Taoist thought, especially Xuanxue, Neo-Daoist. Zen originated as the Chan Buddhism, Chan School (禪宗, ''chánzōng'', 'meditation school') or the Buddha-nature, Buddha-mind school (佛心宗'', fóxīnzōng''), and later developed into various sub-schools and branches. Chan is traditionally believed to have been brought to China by the semi-legendary figure Bodhidharma, an Indian (or Central Asian) monk who is said to have introduced dhyana teachings to China. From China, Chán spread south to Vietnam and became Thiền, Vietnamese Thiền, northeast to Korea to become Korean Seon, Seon Buddhism, and east to Japan, becoming Japanese Zen. Zen emphasizes Buddhist meditation, meditation practice, direct insight int ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

VRAM

Video random-access memory (VRAM) is dedicated computer memory used to store the pixels and other graphics data as a framebuffer to be rendered on a computer monitor. It often uses a different technology than other computer memory, in order to be read quickly for display on a screen. Relation to GPUs Many modern GPUs rely on VRAM. In contrast, a GPU that does ''not'' use VRAM, and relies instead on system RAM, is said to have a unified memory architecture, or shared graphics memory. System RAM and VRAM have been segregated due to the bandwidth requirements of GPUs, and to achieve lower latency, since VRAM is physically closer to the GPU die. Modern VRAM is typically found in a BGA package soldered onto a graphics card. The VRAM is cooled along with the GPU by the GPU heatsink. Technologies * Dual-ported video RAM, used in the 1990s and at the time often called "VRAM" * SGRAM * GDDR SDRAM * High Bandwidth Memory (HBM) See also * Graphics processing unit A graph ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Base Address Register

PCI configuration space is the underlying way that the Conventional PCI, PCI-X and PCI Express perform auto configuration of the cards inserted into their bus. Overview PCI devices have a set of registers referred to as ''configuration space'' and PCI Express introduces ''extended configuration space'' for devices. Configuration space registers are mapped to memory locations. Device drivers and diagnostic software must have access to the configuration space, and operating systems typically use APIs to allow access to device configuration space. When the operating system does not have access methods defined or APIs for memory mapped configuration space requests, the driver or diagnostic software has the burden to access the configuration space in a manner that is compatible with the operating system's underlying access rules. In all systems, device drivers are encouraged to use APIs provided by the operating system to access the configuration space of the device. Technical i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

RDNA2

RDNA 2 is a GPU microarchitecture designed by AMD, released with the Radeon RX 6000 series on November 18, 2020. Alongside powering the RX 6000 series, RDNA 2 is also featured in the SoCs designed by AMD for the PlayStation 5, Xbox Series X/S, and Steam Deck consoles. Background On July 7, 2019, AMD released the first iteration of the RDNA microarchitecture, a new graphics architecture designed specifically for gaming that replaced the aging Graphics Core Next (GCN) microarchitecture. With RDNA, AMD sought to reduce latency and improve power efficiency over their previous Vega series based on GCN 5th gen and Nvidia's competing Turing microarchitecture. RDNA 2 was first publicly announced in January 2020 with AMD initially calling RDNA 2 a "refresh" of the original RDNA architecture from the previous year. At AMD's Financial Analysts Day held on March 5, 2020, AMD showed a client GPU roadmap that gave details on RDNA's successor, RDNA 2, that it would again be built using TS ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Infinity Fabric

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high-bandwidth, low- latency point-to-point link that was introduced on April 2, 2001. The HyperTransport Consortium is in charge of promoting and developing HyperTransport technology. HyperTransport is best known as the system bus architecture of AMD central processing units (CPUs) from Athlon 64 through AMD FX and the associated motherboard chipsets. HyperTransport has also been used by IBM and Apple for the Power Mac G5 machines, as well as a number of modern MIPS systems. The current specification HTX 3.1 remained competitive for 2014 high-speed (2666 and 3200 MT/s or about 10.4 GB/s and 12.8 GB/s) DDR4 RAM and slower (around 1 GB/similar to high end Solid-state drive#Standard card form factors, PCIe SSDs ULLtraDIMM flash RAM) technology—a wider range of RAM speeds on a common CPU ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cache (computing)

In computing, a cache ( ) is a hardware or software component that stores data so that future requests for that data can be served faster; the data stored in a cache might be the result of an earlier computation or a copy of data stored elsewhere. A cache hit occurs when the requested data can be found in a cache, while a cache miss occurs when it cannot. Cache hits are served by reading data from the cache, which is faster than recomputing a result or reading from a slower data store; thus, the more requests that can be served from the cache, the faster the system performs. To be cost-effective, caches must be relatively small. Nevertheless, caches are effective in many areas of computing because typical Application software, computer applications access data with a high degree of locality of reference. Such access patterns exhibit temporal locality, where data is requested that has been recently requested, and spatial locality, where data is requested that is stored near dat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-core Processor

A multi-core processor (MCP) is a microprocessor on a single integrated circuit (IC) with two or more separate central processing units (CPUs), called ''cores'' to emphasize their multiplicity (for example, ''dual-core'' or ''quad-core''). Each core reads and executes Instruction set, program instructions, specifically ordinary Instruction set, CPU instructions (such as add, move data, and branch). However, the MCP can run instructions on separate cores at the same time, increasing overall speed for programs that support Multithreading (computer architecture), multithreading or other parallel computing techniques. Manufacturers typically integrate the cores onto a single IC Die (integrated circuit), die, known as a ''chip multiprocessor'' (CMP), or onto multiple dies in a single Chip carrier, chip package. As of 2024, the microprocessors used in almost all new personal computers are multi-core. A multi-core processor implements multiprocessing in a single physical package. Des ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |