|

Sierra Forest

Sierra Forest is a codename for Intel's first generation E-core based Xeon server processors. It is fabricated using Intel's Intel 3 process. Sierra Forest will be used as part of the Birch Stream server platform in 2024. Architecture Sierra Forest will use only E-cores to achieve higher core counts in order to compete with AMD's Epyc server processors codenamed Bergamo which features up to 128 smaller Zen 4c cores. See also * Process–architecture–optimization model, by Intel * Tick–tock model, by Intel * List of Intel CPU microarchitectures The following is a ''partial'' list of Intel CPU microarchitectures. The list is ''incomplete''. Additional details can be found in Intel's Tick–tock model and Process–architecture–optimization model. x86 microarchitectures 16-bit ; ... References Intel products Intel microprocessors {{Compu-hardware-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

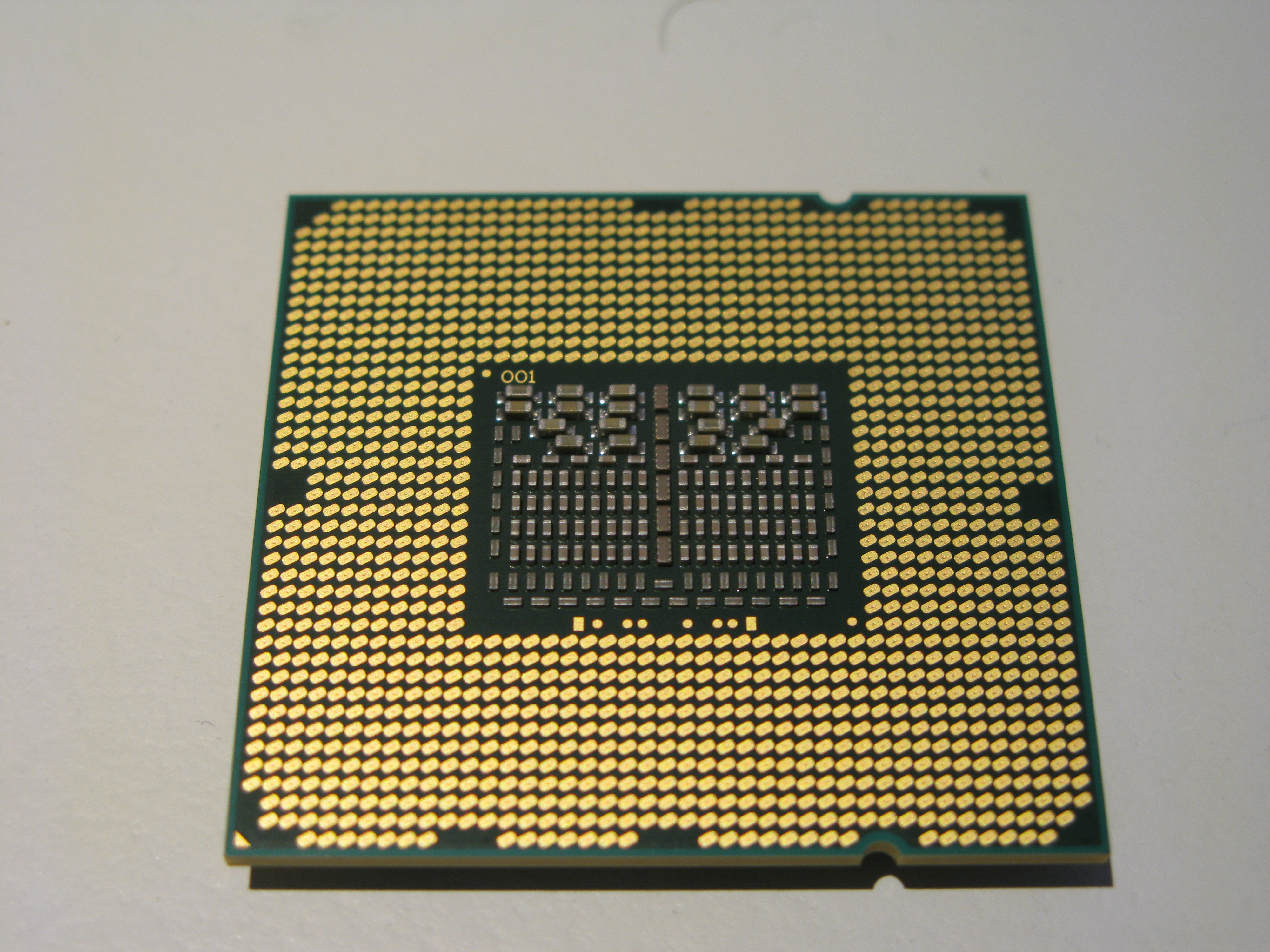

Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 series of instruction sets, the instruction sets found in most personal computers (PCs). Incorporated in Delaware, Intel ranked No. 45 in the 2020 ''Fortune'' 500 list of the largest United States corporations by total revenue for nearly a decade, from 2007 to 2016 fiscal years. Intel supplies microprocessors for computer system manufacturers such as Acer, Lenovo, HP, and Dell. Intel also manufactures motherboard chipsets, network interface controllers and integrated circuits, flash memory, graphics chips, embedded processors and other devices related to communications and computing. Intel (''int''egrated and ''el''ectronics) was founded on July 18, 1968, by semiconductor pioneers Gordon Moore (of Moore's law) and Robert Noyce ( ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Advanced Vector Extensions

Advanced Vector Extensions (AVX) are extensions to the x86 instruction set architecture for microprocessors from Intel and Advanced Micro Devices (AMD). They were proposed by Intel in March 2008 and first supported by Intel with the Sandy Bridge processor shipping in Q1 2011 and later by AMD with the Bulldozer processor shipping in Q3 2011. AVX provides new features, new instructions and a new coding scheme. AVX2 (also known as Haswell New Instructions) expands most integer commands to 256 bits and introduces new instructions. They were first supported by Intel with the Haswell processor, which shipped in 2013. AVX-512 expands AVX to 512-bit support using a new EVEX prefix encoding proposed by Intel in July 2013 and first supported by Intel with the Knights Landing co-processor, which shipped in 2016. In conventional processors, AVX-512 was introduced with Skylake server and HEDT processors in 2017. Advanced Vector Extensions AVX uses sixteen YMM registers to perform a sin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Intel CPU Microarchitectures

The following is a ''partial'' list of Intel CPU microarchitectures. The list is ''incomplete''. Additional details can be found in Intel's Tick–tock model and Process–architecture–optimization model. x86 microarchitectures 16-bit ; 8086: first x86 processor; initially a temporary substitute for the iAPX 432 to compete with Motorola, Zilog, and National Semiconductor and to top the successful Z80. 8088 version, with an 8-bit bus, used in the original IBM Personal Computer. ; 186: included a DMA controller, interrupt controller, timers, and chip select logic. A small number of additional instructions. The 80188 was a version with an 8-bit bus. ; 286: first x86 processor with protected mode including segmentation based virtual memory management. Performance improved by a factor of 3 to 4 over 8086. Included instructions relating to protected mode. 32-bit (IA-32) ; i386: first 32-bit x86 processor. Introduced paging on top of segmentation which is the most commonly ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tick–tock Model

Tick–tock was a production model adopted in 2007 by chip manufacturer Intel. Under this model, every microarchitecture change (tock) was followed by a die shrink of the process technology (tick). It was replaced by the process–architecture–optimization model, which was announced in 2016 and is like a tick–tock cycle followed by an optimization phase. As a general engineering model, tick–tock is a model that refreshes one side of a binary system each release cycle. History Every "tick" represented a shrinking of the process technology of the previous microarchitecture (sometimes introducing new instructions, as with Broadwell, released in late 2014) and every "tock" designated a new microarchitecture. These occurred roughly every year to 18 months. In 2014, Intel created a " tock refresh" of a tock in the form of a smaller update to the microarchitecture not considered a new generation in and of itself. In March 2016, Intel announced in a Form 10-K report that it deprec ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Process–architecture–optimization Model

Process–architecture–optimization is a development model for central processing units (CPUs) that Intel adopted in 2016. Under this three-phase (three-year) model, every microprocessor die shrink is followed by a microarchitecture change and then by one or more optimizations. It replaced the two-phase (two-year) tick–tock model that Intel adopted in 2006. The tick–tock model was no longer economically sustainable, according to Intel, because production of ever smaller dies becomes ever more costly.Tick Tock On The Rocks: Intel Delays 10nm, Adds 3rd Gen 14nm Core Product "Kaby Lake" AnandTech. 16 July 2015. Roadmap See also * |

Zen 4

Zen 4 is the codename for a CPU microarchitecture by AMD, released on September 27, 2022. It is the successor to Zen 3 and uses TSMC's N5 process for CCDs. Zen 4 powers Ryzen 7000 mainstream desktop processors (codenamed "Raphael") and will be used in high-end mobile processors (codenamed "Dragon Range"), thin & light mobile processors (codenamed "Phoenix"), as well as Epyc 9004 server processors (codenamed "Genoa" and "Bergamo"). Features Like its predecessor, Zen 4 in its Desktop Ryzen variants features one or two Core Complex Dies (CCDs) built on TSMC's 5 nm process and one I/O die built on 6 nm. Previously, the I/O die on Zen 3 was built on GlobalFoundries' 14 nm process. Zen 4's I/O die includes integrated RDNA 2 graphics for the first time on any Zen architecture. Zen 4 marks the first utilization of the 5 nm process for x86-based desktop processors. On desktop and server platforms, Zen 4 has moved from DDR4 to DDR5 memory; DDR4 is not supported. Addit ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Epyc

Epyc is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets. Epyc processors share the same microarchitecture as their regular desktop-grade counterparts, but have enterprise-grade features such as higher core counts, more PCI Express lanes, support for larger amounts of RAM, and larger cache memory. They also support multi-chip and dual-socket system configurations by using the Infinity Fabric interconnect. History In March 2017, AMD announced plans to re-enter the server market with a platform based on the Zen microarchitecture, codenamed Naples, and officially revealed it under the brand name Epyc in May. That June, AMD officially launched Epyc 7001 series processors, offering up to 32 cores per socket, and enabling performance that allowed Epyc to be competitive with the competing Intel Xeon product line. Two years ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Advanced Micro Devices

Advanced Micro Devices, Inc. (AMD) is an American multinational semiconductor company based in Santa Clara, California, that develops computer processors and related technologies for business and consumer markets. While it initially manufactured its own processors, the company later outsourced its manufacturing, a practice known as going fabless, after GlobalFoundries was spun off in 2009. AMD's main products include microprocessors, motherboard chipsets, embedded processors, graphics processors, and FPGAs for servers, workstations, personal computers, and embedded system applications. History First twelve years Advanced Micro Devices was formally incorporated by Jerry Sanders, along with seven of his colleagues from Fairchild Semiconductor, on May 1, 1969. Sanders, an electrical engineer who was the director of marketing at Fairchild, had, like many Fairchild executives, grown frustrated with the increasing lack of support, opportunity, and flexibility within th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Intel Codenames

Intel has historically named integrated circuit (IC) development projects after geographical names of towns, rivers or mountains near the location of the Intel facility responsible for the IC. Many of these are in the American West, particularly in Oregon (where most of Intel's CPU projects are designed; see Project code name#Famous code names, famous codenames). As Intel's development activities have expanded, this nomenclature has expanded to Israel and India, and some older codenames refer to celestial bodies. The following table lists known Intel codenames along with a brief explanation of their meaning and their likely namesake, and the year of their earliest known public appearance. Most processors after a certain date were named after cities that could be found on a map of the United States. This was done for trademark considerations. Banias was the last of the non-US city names. Gesher was renamed to Sandy Bridge to comply with the new rule. Dothan is a city both in Israel ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Emerald Rapids

Emerald Rapids is a codename for Intel's fifth generation Xeon server processors based on the Intel 7 node. Emerald Rapids CPUs are designed for data centers; the roughly contemporary Raptor Lake is intended for the wider public. Nevine Nassif is a chief engineer for this generation. Features CPU * Up to 64 Raptor Cove CPU cores per package Trust Domain Extensions (TDX) a collection of technologies to help deploy hardware-isolated virtual machines (VMs) called trust domains (TDs) I/O * DDR5 memory support up to DDR5-5600 * Up to 80 PCI Express 5.0 lanes See also * Intel's process–architecture–optimization model * Intel's tick–tock model * List of Intel CPU microarchitectures The following is a ''partial'' list of Intel CPU microarchitectures. The list is ''incomplete''. Additional details can be found in Intel's Tick–tock model and Process–architecture–optimization model. x86 microarchitectures 16-bit ; ... References {{Intel processor r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

VT-d

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel (VT-x) and AMD (AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited acce ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

VT-x

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel (VT-x) and AMD (AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited acce ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |