|

X86 Bit Manipulation Instruction Set

Bit manipulation instructions sets (BMI sets) are extensions to the x86 instruction set architecture for microprocessors from Intel and AMD. The purpose of these instruction sets is to improve the speed of bit manipulation. All the instructions in these sets are non- SIMD and operate only on general-purpose registers. There are two sets published by Intel: BMI (now referred to as BMI1) and BMI2; they were both introduced with the Haswell microarchitecture with BMI1 matching features offered by AMD's ABM instruction set and BMI2 extending them. Another two sets were published by AMD: ABM (''Advanced Bit Manipulation'', which is also a subset of SSE4a implemented by Intel as part of SSE4.2 and BMI1), and TBM (''Trailing Bit Manipulation'', an extension introduced with Piledriver-based processors as an extension to BMI1, but dropped again in Zen-based processors). ABM (Advanced Bit Manipulation) AMD was the first to introduce the instructions that now form Intel's BMI1 as p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instruction Set Architecture

In computer science, an instruction set architecture (ISA) is an abstract model that generally defines how software controls the CPU in a computer or a family of computers. A device or program that executes instructions described by that ISA, such as a central processing unit (CPU), is called an ''implementation'' of that ISA. In general, an ISA defines the supported instructions, data types, registers, the hardware support for managing main memory, fundamental features (such as the memory consistency, addressing modes, virtual memory), and the input/output model of implementations of the ISA. An ISA specifies the behavior of machine code running on implementations of that ISA in a fashion that does not depend on the characteristics of that implementation, providing binary compatibility between implementations. This enables multiple implementations of an ISA that differ in characteristics such as performance, physical size, and monetary cost (among other things), but t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GitHub

GitHub () is a Proprietary software, proprietary developer platform that allows developers to create, store, manage, and share their code. It uses Git to provide distributed version control and GitHub itself provides access control, bug tracking system, bug tracking, software feature requests, task management, continuous integration, and wikis for every project. Headquartered in California, GitHub, Inc. has been a subsidiary of Microsoft since 2018. It is commonly used to host open source software development projects. GitHub reported having over 100 million developers and more than 420 million Repository (version control), repositories, including at least 28 million public repositories. It is the world's largest source code host Over five billion developer contributions were made to more than 500 million open source projects in 2024. About Founding The development of the GitHub platform began on October 19, 2005. The site was launched in April 2008 by Tom ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

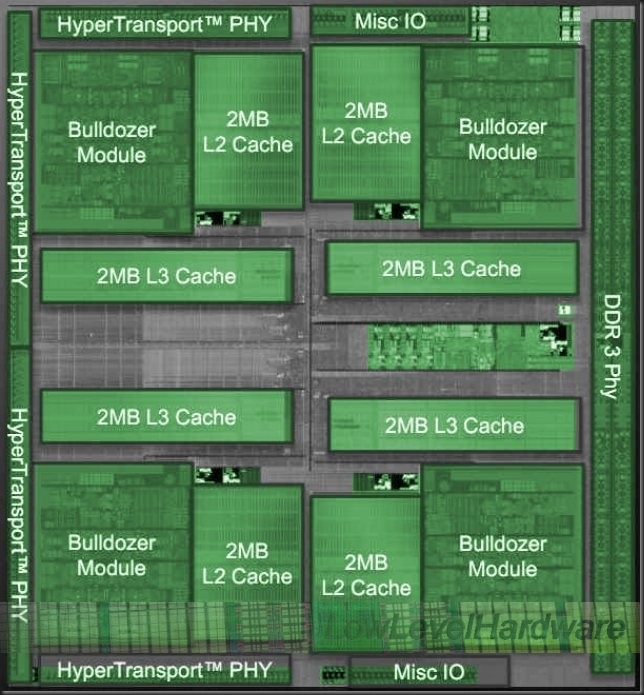

Bulldozer (microarchitecture)

The AMD Bulldozer Family 15h is a microprocessor microarchitecture for the FX and Opteron line of processors, developed by AMD for the desktop and server markets. Bulldozer is the codename for this family of microarchitectures. It was released on October 12, 2011, as the successor to the K10 microarchitecture. Bulldozer is designed from scratch, not a development of earlier processors. The core is specifically aimed at computing products with TDPs of 10 to 125 watts. AMD claims dramatic performance-per-watt efficiency improvements in high-performance computing (HPC) applications with Bulldozer cores. The ''Bulldozer'' cores support most of the instruction sets implemented by Intel processors ( Sandy Bridge) available at its introduction (including SSSE3, SSE4.1, SSE4.2, AES, CLMUL, and AVX) as well as new instruction sets proposed by AMD; ABM, XOP, FMA4 and F16C. Only Bulldozer GEN4 (Excavator) supports AVX2 instruction sets. Overview According to AMD, Bul ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Puma (microarchitecture)

The Puma Family 16h is a low-power microarchitecture by AMD for its APUs. It succeeds the Jaguar as a second-generation version, targets the same market, and belongs to the same AMD architecture Family 16h. The ''Beema'' line of processors are aimed at low-power notebooks, and ''Mullins'' are targeting the tablet sector. Design The Puma cores use the same microarchitecture as Jaguar, and inherits the design: * Out-of-order execution and Speculative execution, up to 4 CPU cores * Two-way integer execution * Two-way 128-bit wide floating-point and packed integer execution * Integer hardware divider * Puma does not feature clustered multi-thread (CMT), meaning that there are no "modules" * Puma does not feature Heterogeneous System Architecture or zero-copy * 32 KiB instruction + 32 KiB data L1 cache per core * 1–2 MiB unified L2 cache shared by two or four cores * Integrated single channel memory controller supporting 64bit DDR3L * 3.1 mm2 area per core ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bobcat (processor)

The AMD Bobcat Family 14h is a microarchitecture created by AMD for its AMD APUs, aimed at a low-power/low-cost market. It was revealed during a speech from AMD executive vice-president Henri Richard in Computex 2007 and was put into production Q1 2011. One of the major supporters was executive vice-president Mario A. Rivas who felt it was difficult to compete in the x86 market with a single core optimized for the 10–100 W range and actively promoted the development of the simpler core with a target range of 1–10 W. In addition, it was believed that the core could migrate into the hand-held space if the power consumption can be reduced to less than 1 W. Bobcat cores are used together with GPU cores in accelerated processing units (APUs) under the "Fusion" brand. A simplified architecture diagram was released at AMD's Analyst Day in November 2009. This is similar in concept with earlier AMD research in 2003,AMD 2003 Microprocessor Forum SlidesSlide 11anSlide 22 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD 10h

The AMD Family 10h, or K10, is a microprocessor microarchitecture by AMD based on the K8 microarchitecture. The first third-generation Opteron products for servers were launched on September 10, 2007, with the Phenom processors for desktops following and launching on November 11, 2007, as the immediate successors to the K8 series of processors (Athlon 64, Opteron, 64-bit Sempron). Nomenclature It appears that AMD has not used K-nomenclature (which originally stood for "Kryptonite" in the K5 processor) from the time after the use of the codename ''K8'' for the AMD K8 or Athlon 64 processor family, since no K-nomenclature naming convention beyond K8 has appeared in official AMD documents and press releases after the beginning of 2005. The name "''K8L''" was first coined by Charlie Demerjian in 2005, at the time a writer at ''The Inquirer'', and was used by the wider IT community as a convenient shorthand while according to AMD official documents, the processor family was terme ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Broadwell (microarchitecture)

Broadwell (previously Rockwell) is the fifth generation of the Intel Core processor. It is Intel's codename for the 14 nanometer die shrink of its Haswell microarchitecture. It is a "tick" in Intel's tick–tock principle as the next step in semiconductor fabrication. Like some of the previous tick-tock iterations, Broadwell did not completely replace the full range of CPUs from the previous microarchitecture ( Haswell), as there were no low-end desktop CPUs based on Broadwell. Some of the processors based on the Broadwell microarchitecture are marketed as "5th-generation Core" i3, i5 and i7 processors. This moniker is however not used for marketing of the Broadwell-based Celeron, Pentium or Xeon chips. This microarchitecture also introduced the Core M processor branding. Broadwell's H and C variants are used in conjunction with Intel 9 Series chipsets ( Z97, H97 and HM97), in addition to retaining backward compatibility with some of the Intel 8 Series chipse ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Skylake (microarchitecture)

Skylake is Intel's codename for its sixth generation Core microprocessor family that was launched on August 5, 2015, succeeding the Broadwell microarchitecture. Skylake is a microarchitecture redesign using the same 14 nm manufacturing process technology as its predecessor, serving as a tock in Intel's tick–tock manufacturing and design model. According to Intel, the redesign brings greater CPU and GPU performance and reduced power consumption. Skylake CPUs share their microarchitecture with Kaby Lake, Coffee Lake, Whiskey Lake, and Comet Lake CPUs. Skylake is the last Intel platform on which Windows earlier than Windows 10 are officially supported by Microsoft, although enthusiast-created modifications are available that disabled the Windows Update check and allowed Windows 8.1 and earlier to continue to receive Windows Updates on this and later platforms. Some of the processors based on the Skylake microarchitecture are marketed as sixth-generation Core. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Silvermont

Silvermont is a microarchitecture for low-power Atom, Celeron and Pentium branded processors used in systems on a chip (SoCs) made by Intel. Silvermont forms the basis for a total of four SoC families: * ''Merrifield'' and ''Moorefield'' consumer SoCs intended for smartphones * ''Bay Trail'' consumer SoCs aimed at tablets, hybrid devices, netbooks, nettops, and embedded/automotive systems * ''Avoton'' SoCs for micro-servers and storage devices * ''Rangeley'' SoCs targeting network and communication infrastructure. Silvermont is the successor of the Bonnell, using a newer 22 nm process (previously introduced with Ivy Bridge) and a new microarchitecture, replacing Hyper Threading with out-of-order execution. Silvermont was announced to news media on May 6, 2013, at Intel's headquarters at Santa Clara, California. Intel had repeatedly said the first Bay Trail devices would be available during the Holiday 2013 timeframe, while leaked slides showed that the release window f ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ivy Bridge (microarchitecture)

Ivy Bridge is the codename for Intel's 22 nm microarchitecture used in the third generation of the Intel Core processors ( Core i7, i5, i3). Ivy Bridge is a die shrink to 22 nm process based on FinFET ("3D") Tri-Gate transistors, from the former generation's 32 nm Sandy Bridge microarchitecture—also known as tick–tock model. The name is also applied more broadly to the Xeon and Core i7 Extreme Ivy Bridge-E series of processors released in 2013. Ivy Bridge processors are backward compatible with the Sandy Bridge platform, but such systems might require a firmware update (vendor specific). In 2011, Intel released the 7-series Panther Point chipsets with integrated USB 3.0 and SATA 3.0 to complement Ivy Bridge. Volume production of Ivy Bridge chips began in the third quarter of 2011. Quad-core and dual-core-mobile models launched on April 29, 2012 and May 31, 2012 respectively. Core i3 desktop processors, as well as the first 22 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sandy Bridge

Sandy Bridge is the List of Intel codenames, codename for Intel's 32 nm process, 32 nm microarchitecture used in the second generation of the Intel Core, Intel Core processors (Intel Core i7, Core i7, Intel Core i5, i5, Intel Core i3, i3). The Sandy Bridge microarchitecture is the successor to Nehalem (microarchitecture), Nehalem and Westmere (microarchitecture), Westmere microarchitecture. Intel demonstrated an A1 stepping Sandy Bridge processor in 2009 during Intel Developer Forum (IDF), and released first products based on the architecture in January 2011 under the Intel Core#Sandy Bridge microarchitecture based, Core brand. Sandy Bridge is manufactured in the 32 nanometer, 32 nm process and has a soldered contact with the die and IHS (Integrated Heat Spreader), while Intel's subsequent generation Ivy Bridge (microarchitecture), Ivy Bridge uses a 22 nanometer, 22 nm die shrink and a TIM (Thermal Interface Material) between the die and the IHS. Technology Intel demonstrated a S ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nehalem (microarchitecture)

Nehalem is the codename for Intel's 45 nm microarchitecture released in November 2008. It was used in the first generation of the Intel Core i5 and i7 processors, and succeeds the older Core microarchitecture used on Core 2 processors. The term "Nehalem" comes from the Nehalem River. Nehalem is built on the 45 nm process, is able to run at higher clock speeds without sacrificing efficiency, and is more energy-efficient than Penryn microprocessors. Hyper-threading is reintroduced, along with a reduction in L2 cache size, as well as an enlarged L3 cache that is shared among all cores. Nehalem is an architecture that differs radically from NetBurst, while retaining some of the latter's minor features. Nehalem later received a die-shrink to 32 nm with Westmere, and was fully succeeded by "second-generation" Sandy Bridge in January 2011. Technology * Cache line block on L2/L3 cache was reduced from 128 bytes in NetBurst & Merom/Penryn to 64 bytes per line in this gene ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |