Emotion Engine on:

[Wikipedia]

[Google]

[Amazon]

The Emotion Engine is a

The Emotion Engine consists of eight separate "units", each performing a specific task, integrated onto the same die. These units are: a CPU core, two Vector Processing Units (VPU), a 10-channel DMA unit, a

The Emotion Engine consists of eight separate "units", each performing a specific task, integrated onto the same die. These units are: a CPU core, two Vector Processing Units (VPU), a 10-channel DMA unit, a

central processing unit

A central processing unit (CPU), also called a central processor, main processor, or just processor, is the primary Processor (computing), processor in a given computer. Its electronic circuitry executes Instruction (computing), instructions ...

developed and manufactured by Sony Computer Entertainment

Sony Interactive Entertainment LLC (SIE) is an American video game and digital entertainment company that is a major subsidiary of Japanese conglomerate Sony, Sony Group Corporation. It primarily operates the PlayStation brand of video game co ...

and Toshiba

is a Japanese multinational electronics company headquartered in Minato, Tokyo. Its diversified products and services include power, industrial and social infrastructure systems, elevators and escalators, electronic components, semiconductors ...

for use in the PlayStation 2

The PlayStation 2 (PS2) is a home video game console developed and marketed by Sony Interactive Entertainment, Sony Computer Entertainment. It was first released in Japan on 4 March 2000, in North America on 26 October, in Europe on 24 Novembe ...

video game console

A video game console is an electronic device that Input/output, outputs a video signal or image to display a video game that can typically be played with a game controller. These may be home video game console, home consoles, which are generally ...

. It was also used in early PlayStation 3

The PlayStation 3 (PS3) is a home video game console developed and marketed by Sony Computer Entertainment (SCE). It is the successor to the PlayStation 2, and both are part of the PlayStation brand of consoles. The PS3 was first released on ...

models sold in Japan and North America (Model Numbers CECHAxx & CECHBxx) to provide PlayStation 2 game support. Mass production of the Emotion Engine began in 1999 and ended in late 2012 with the discontinuation of the PlayStation 2.

Description

The Emotion Engine consists of eight separate "units", each performing a specific task, integrated onto the same die. These units are: a CPU core, two Vector Processing Units (VPU), a 10-channel DMA unit, a

The Emotion Engine consists of eight separate "units", each performing a specific task, integrated onto the same die. These units are: a CPU core, two Vector Processing Units (VPU), a 10-channel DMA unit, a memory controller

A memory controller, also known as memory chip controller (MCC) or a memory controller unit (MCU), is a digital circuit that manages the flow of data going to and from a computer's main memory. When a memory controller is integrated into anothe ...

, and an Image Processing Unit (IPU). There are three interfaces: an input output interface to the I/O processor, a graphics interface (GIF) to the graphics synthesizer, and a memory interface to the system memory.

The CPU core is tightly coupled to the first VPU, VPU0. Together, they are responsible for executing game code and high-level modeling computations. The second VPU, VPU1, is dedicated to geometry-transformations and lighting and operates independently, parallel to the CPU core, controlled by microcode

In processor design, microcode serves as an intermediary layer situated between the central processing unit (CPU) hardware and the programmer-visible instruction set architecture of a computer. It consists of a set of hardware-level instructions ...

. VPU0, when not utilized, can also be used for geometry-transformations. Display list

A display list, also called a command list in Direct3D 12 and a command buffer in Vulkan, is a series of graphics commands or instructions that are run when the list is executed. Systems that make use of display list functionality are called ...

s generated by CPU/VPU0 and VPU1 are sent to the GIF, which prioritizes them before dispatching them to the Graphics Synthesizer for rendering.

CPU core

The CPU core is a two-waysuperscalar

A superscalar processor (or multiple-issue processor) is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single in ...

in-order RISC

In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a comp ...

processor. Based on the MIPS R5900, it implements the MIPS-III instruction set architecture

In computer science, an instruction set architecture (ISA) is an abstract model that generally defines how software controls the CPU in a computer or a family of computers. A device or program that executes instructions described by that ISA, ...

(ISA) and much of MIPS-IV, in addition to a custom instruction set developed by Sony which operated on 128-bit wide groups of either 32-bit, 16-bit, or 8-bit integers in single instruction, multiple data

Single instruction, multiple data (SIMD) is a type of parallel computer, parallel processing in Flynn's taxonomy. SIMD describes computers with multiple processing elements that perform the same operation on multiple data points simultaneousl ...

(SIMD) fashion (e.g. four 32-bit integers could be added to four others using a single instruction). Instructions defined include: add, subtract, multiply, divide, min/max, shift, logical, leading-zero count, 128-bit load/store and 256-bit to 128-bit funnel shift in addition to some not described by Sony for competitive reasons. Contrary to some misconceptions, these SIMD capabilities did not amount to the processor being "128-bit", as neither the memory addresses nor the integers themselves were 128-bit, only the shared SIMD/integer registers. For comparison, 128-bit wide registers and SIMD instructions had been present in the 32-bit x86

x86 (also known as 80x86 or the 8086 family) is a family of complex instruction set computer (CISC) instruction set architectures initially developed by Intel, based on the 8086 microprocessor and its 8-bit-external-bus variant, the 8088. Th ...

architecture since 1999, with the introduction of SSE. However the internal data paths were 128-bit wide, and its processors were capable of operating on 4x32bit quantities in parallel in single registers.

It has a 6-stage integer pipeline

A pipeline is a system of Pipe (fluid conveyance), pipes for long-distance transportation of a liquid or gas, typically to a market area for consumption. The latest data from 2014 gives a total of slightly less than of pipeline in 120 countries ...

and a 15-stage floating-point

In computing, floating-point arithmetic (FP) is arithmetic on subsets of real numbers formed by a ''significand'' (a Sign (mathematics), signed sequence of a fixed number of digits in some Radix, base) multiplied by an integer power of that ba ...

(FP) pipeline. Its assortment of registers consists of 32 128-bit VLIW SIMD registers (naming/renaming), one 64-bit accumulator and two 64-bit general data registers, 8 16-bit fix function registers, 16 8-bit controller registers. The processor also has two 64-bit integer arithmetic logic unit

In computing, an arithmetic logic unit (ALU) is a Combinational logic, combinational digital circuit that performs arithmetic and bitwise operations on integer binary numbers. This is in contrast to a floating-point unit (FPU), which operates on ...

s (ALUs), a 128-bit load–store unit (LSU), a Branch Execution Unit (BXU), and a 32-bit VU1 floating-point unit

A floating-point unit (FPU), numeric processing unit (NPU), colloquially math coprocessor, is a part of a computer system specially designed to carry out operations on floating-point numbers. Typical operations are addition, subtraction, multip ...

(FPU) coprocessor (which acted as a sync controller for the VPU0/VPU1) containing a MIPS base processor core with 32 64-bit FP registers and 15 32-bit integer registers. The ALUs are 64-bit, with a 32-bit FPU that isn't IEEE 754 compliant. The custom instruction set 107 MMI (Multimedia Extensions) was implemented by grouping the two 64-bit integer ALUs. Both the integer and floating-point pipelines are six stages long.

To feed the execution units with instructions and data, there is a 16 KB two-way set associative

In mathematics, the associative property is a property of some binary operations that rearranging the parentheses in an expression will not change the result. In propositional logic, associativity is a valid rule of replacement for express ...

instruction cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which ...

, an 8 KB two-way set associative non blocking data cache and a 16 KB scratchpad RAM. Both the instruction and data caches are virtually indexed and physically tagged while the scratchpad RAM exists in a separate memory space. A combined 48 double entry instruction and data translation lookaside buffer

A translation lookaside buffer (TLB) is a memory CPU cache, cache that stores the recent translations of virtual memory address to a physical memory Memory_address, location. It is used to reduce the time taken to access a user memory location. It ...

is provided for translating virtual addresses. Branch prediction

In computer architecture, a branch predictor is a digital circuit that tries to guess which way a branch (e.g., an if–then–else structure) will go before this is known definitively. The purpose of the branch predictor is to improve the flow ...

is achieved by a 64-entry branch target address cache and a branch history table that is integrated into the instruction cache. The branch misprediction penalty is three cycles due to the short six stage pipeline.

Vector processing units

The majority of the Emotion Engine'sfloating point

In computing, floating-point arithmetic (FP) is arithmetic on subsets of real numbers formed by a ''significand'' (a signed sequence of a fixed number of digits in some base) multiplied by an integer power of that base.

Numbers of this form ...

performance is provided by two vector processing

In computing, a vector processor or array processor is a central processing unit (CPU) that implements an instruction set where its Instruction (computer science), instructions are designed to operate efficiently and effectively on large Array d ...

units (VPU), designated VPU0 and VPU1. These were essentially DSPs tailored for 3D math, and the forerunner to hardware vertex shader pipelines. Each VPU features 32 128-bit

General home computing and gaming utility emerged at 8-bit word sizes, as 28=256 Word (computer architecture), words, a natural unit of data, became possible. Early 8-bit CPUs (such as the Zilog Z80 and MOS Technology 6502, used in the 1977 Co ...

vector SIMD registers (holding 4D vector data), 16 16-bit fixed-point registers, four floating point multiply-accumulate

Floating may refer to:

* a type of dental work performed on horse teeth

* use of an isolation tank

* the guitar-playing technique where chords are sustained rather than scratched

* Floating (play), ''Floating'' (play), by Hugh Hughes

* Floating (p ...

(FMAC) units, a floating point divide (FDIV) unit and a local data memory. The data memory for VPU0 is 4 KB in size, while VPU1 features a 16 KB data memory.

To achieve high bandwidth, the VPU's data memory is connected directly to the GIF, and both of the data memories can be read directly by the DMA unit. A single vector instruction consists of four 32-bit single-precision floating-point values which are distributed to the four single-precision (32-bit) FMAC units for processing. This scheme is similar to the SSEx extensions by Intel.

The FMAC units take four cycles to execute one instruction, but as the units have a six-stage pipeline

A pipeline is a system of Pipe (fluid conveyance), pipes for long-distance transportation of a liquid or gas, typically to a market area for consumption. The latest data from 2014 gives a total of slightly less than of pipeline in 120 countries ...

, they have a throughput of one instruction per cycle. The FDIV unit has a nine-stage pipeline and can execute one instruction every seven cycles.

Image Processing Unit (IPU)

The IPU allowedMPEG-2

MPEG-2 (a.k.a. H.222/H.262 as was defined by the ITU) is a standard for "the generic coding of moving pictures and associated audio information". It describes a combination of lossy video compression and lossy audio data compression methods ...

compressed image decoding, allowing playback of DVDs and game FMV. It also allowed vector quantization for 2D graphics data.

DMA, DRAM and Memory Management Unit (MMU)

The memory management unit,RDRAM

Rambus DRAM (RDRAM), and its successors Concurrent Rambus DRAM (CRDRAM) and Direct Rambus DRAM (DRDRAM), are types of synchronous dynamic random-access memory (SDRAM) developed by Rambus from the 1990s through to the early 2000s. The third-generati ...

controller and DMA controller handle memory access within the system.

Internal data bus

Communications between the MIPS core, the two VPUs, GIF, memory controller and other units is handled by a 128-bit wide internal data bus running at half the clock frequency of the Emotion Engine but, to offer greater bandwidth, there is also a 128-bit dedicated path between the CPU and VPU0 and a 128-bit dedicated path between VPU1 and GIF. At 150 MHz, the internal data bus provides a maximum theoretical bandwidth of 2.4 GB/s.External interface

Communication between the Emotion Engine and RAM occurs through two channels of DRDRAM (Direct Rambus Dynamic Random Access Memory) and thememory controller

A memory controller, also known as memory chip controller (MCC) or a memory controller unit (MCU), is a digital circuit that manages the flow of data going to and from a computer's main memory. When a memory controller is integrated into anothe ...

, which interfaces to the internal data bus. Each channel is 16 bits wide and operates at 400 MHz DDR (Double Data Rate). Combined, the two channels of DRDRAM have a maximum theoretical bandwidth of 25.6 Gbit/s (3.2 GB/s), about 33% more bandwidth than the internal data bus. Because of this, the memory controller buffers data sent from the DRDRAM channels so the extra bandwidth can be utilised by the CPU.

The Emotion Engine interfaces directly to the Graphics Synthesizer via the GIF with a dedicated 64-bit, 150 MHz bus that has a maximum theoretical bandwidth of 1.2 GB/s.

To provide communications between the Emotion Engine and the Input Output Processor (IOP), the input output interface interfaces a 32-bit wide, 37.5 MHz input output bus with a maximum theoretical bandwidth of 150 MB/s to the internal data bus. The interface provides enough bandwidth for the PCMCIA extension connector which was used for the network adapter with built-in P-ATA interface for faster data access and online functionality. An advantage of the high bandwidth was that it could be easily used to introduce hardware extensions like the Network Adapter with built-in IDE HDD support or other extensions to extend functionality and product lifecycle which can be seen as a competitive advantage. In newer variants (like the slim edition), the interface would however, offer vastly more bandwidth than what is required by the PlayStation's input output devices as the HDD support was removed and the PCMCIA connector design was abandoned in favor of a slimmer design.

Fabrication

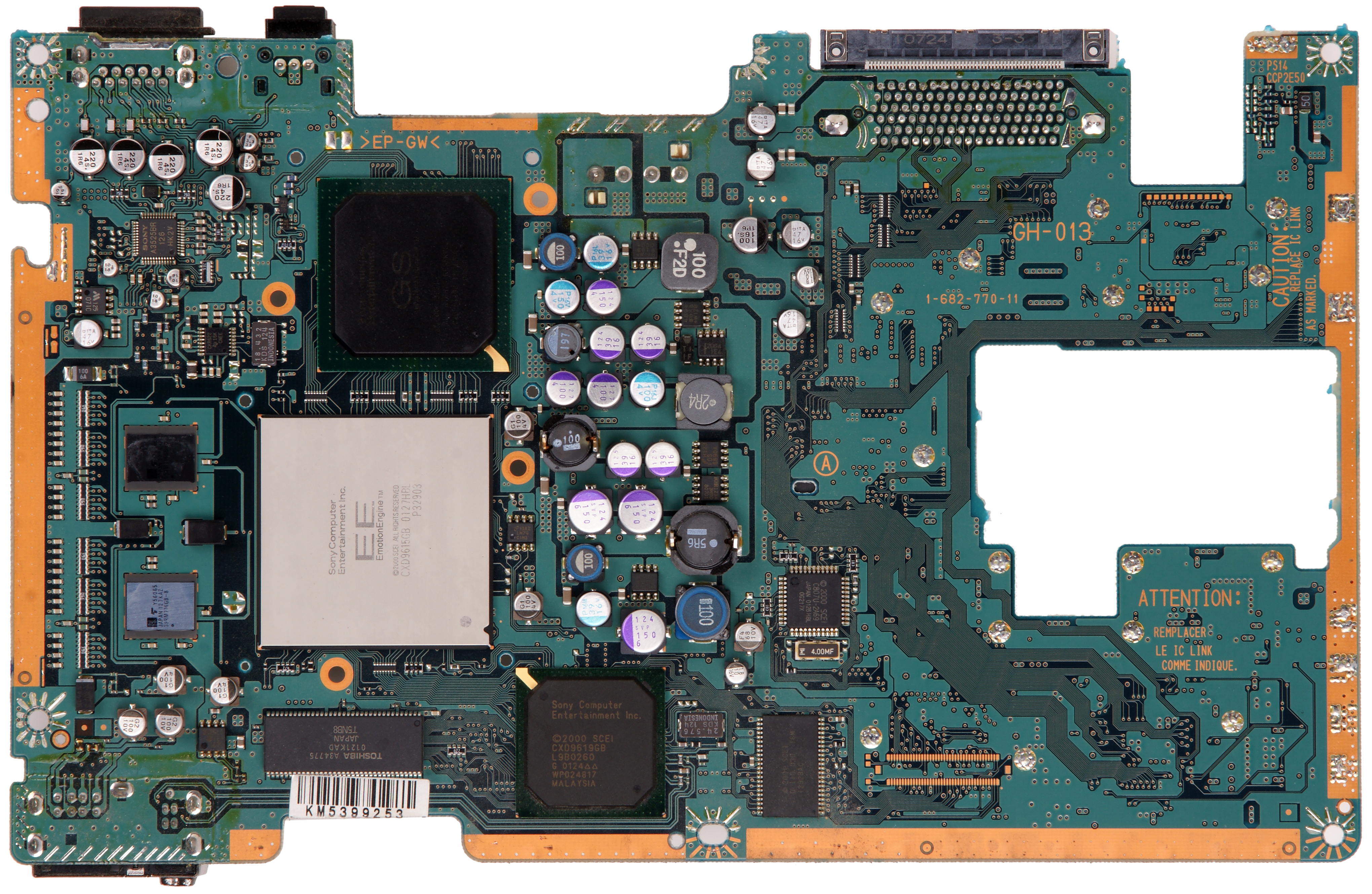

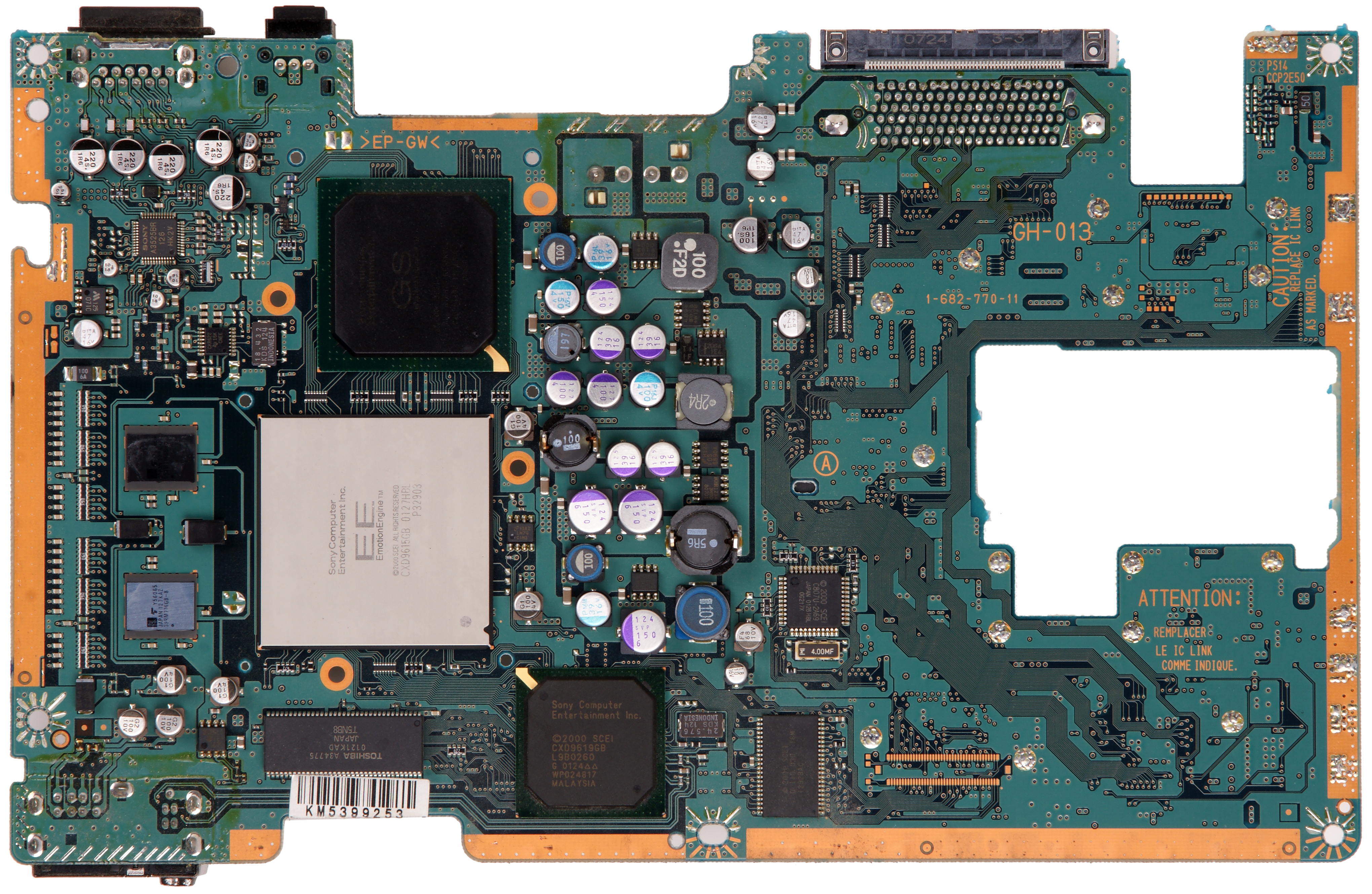

The Emotion Engine contained 13.5 millionmetal–oxide–semiconductor

upright=1.3, Two power MOSFETs in amperes">A in the ''on'' state, dissipating up to about 100 watt">W and controlling a load of over 2000 W. A matchstick is pictured for scale.

In electronics, the metal–oxide–semiconductor field- ...

(MOS) transistors, on an integrated circuit

An integrated circuit (IC), also known as a microchip or simply chip, is a set of electronic circuits, consisting of various electronic components (such as transistors, resistors, and capacitors) and their interconnections. These components a ...

(IC) die measuring 240 mm2. It was fabricated by Sony and Toshiba in a 0.25 μm ( 0.18 μm effective LG) complementary metal–oxide–semiconductor

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss

", , ) is a type of MOSFET, metal–oxide–semiconductor field-effect transistor (MOSFET) semiconductor device fabrication, fabrication process that uses complementary an ...

(CMOS) process with four levels of interconnect.

Packaging

The Emotion Engine was packaged in a 540-contact plasticball grid array

A ball grid array (BGA) is a type of surface-mount packaging (a chip carrier) used for integrated circuits. BGA packages are used to permanently mount devices such as microprocessors. A BGA can provide more interconnection pins than can be pu ...

(PBGA).

Uses

The primary use of the Emotion Engine was to serve as thePlayStation 2

The PlayStation 2 (PS2) is a home video game console developed and marketed by Sony Interactive Entertainment, Sony Computer Entertainment. It was first released in Japan on 4 March 2000, in North America on 26 October, in Europe on 24 Novembe ...

's CPU.

The first PlayStation 3

The PlayStation 3 (PS3) is a home video game console developed and marketed by Sony Computer Entertainment (SCE). It is the successor to the PlayStation 2, and both are part of the PlayStation brand of consoles. The PS3 was first released on ...

revisions produced also featured an Emotion Engine on the motherboard to achieve backwards compatibility with PlayStation 2 games. However, the second revisions of the PlayStation 3

The PlayStation 3 (PS3) is a home video game console developed and marketed by Sony Computer Entertainment (SCE). It is the successor to the PlayStation 2, and both are part of the PlayStation brand of consoles. The PS3 was first released on ...

lacked a physical Emotion Engine in order to lower costs, performing all of its functions using software emulation performed by the Cell Broadband Processor, coupled with a hardware Graphics Synthesizer still present to achieve PlayStation 2 backwards compatibility. In all subsequent revisions, the Graphics Synthesizer was removed; however, a PlayStation 2 software emulator is available in later system software revisions for use with Sony's PS2 Classics titles available for purchase on the Sony Entertainment Network.

The Emotion Engine was also used in the PSX (digital video recorder) as well as the HDTV television models Sony WEGA HVX (Model Numbers KDE-xxxHVX/KDL-xxxHVX) and Sony BRAVIA KDL22PX300, all of which used PlayStation 2 hardware.

Technical specifications

* Clock frequency: 294.912MHz

The hertz (symbol: Hz) is the unit of frequency in the International System of Units (SI), often described as being equivalent to one event (or cycle) per second. The hertz is an SI derived unit whose formal expression in terms of SI base u ...

, 299 MHz (later versions)

* Instruction set

In computer science, an instruction set architecture (ISA) is an abstract model that generally defines how software controls the CPU in a computer or a family of computers. A device or program that executes instructions described by that ISA, s ...

: MIPS III, MIPS IV subset, 107 vector instructions

* 2-issue, 2 64-bit fixed point units, 1 floating point unit, 6 stage pipeline

* Instruction cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which ...

: 16 KB, 2-way set associative

* Data cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which ...

: 8 KB, 2-way set associative

* Scratchpad RAM: 16 KB

* Translation look aside buffer: 48-entry combined instruction/data

* Vector processing unit: 4 FMAC units, 1 FDIV unit

* Vector processing unit registers: 128-bit wide, 32 entries

* Image processing unit: MPEG2

MPEG-2 (a.k.a. H.222/H.262 as was defined by the ITU) is a standard for "the generic coding of moving pictures and associated audio information". It describes a combination of lossy video compression and lossy audio data compression methods ...

macroblock

The macroblock is a processing unit in image and video compression formats based on linear block transforms, typically the discrete cosine transform (DCT). A macroblock typically consists of 16×16 samples, and is further subdivided into transform ...

layer decoder

* Direct memory access

Direct memory access (DMA) is a feature of computer systems that allows certain hardware subsystems to access main system computer memory, memory independently of the central processing unit (CPU).

Without DMA, when the CPU is using programmed i ...

: 10 channels

* VDD Voltage

Voltage, also known as (electrical) potential difference, electric pressure, or electric tension, is the difference in electric potential between two points. In a Electrostatics, static electric field, it corresponds to the Work (electrical), ...

: 1.8 V

* Power consumption

Electric energy consumption is energy consumption in the form of electrical energy. About a fifth of global energy is consumed as electricity: for residential, industrial, commercial, transportation and other purposes.

The global electricity con ...

: 15 W at 1.8 V

* Embedded memory: 1KB RAM

Ram, ram, or RAM most commonly refers to:

* A male sheep

* Random-access memory, computer memory

* Ram Trucks, US, since 2009

** List of vehicles named Dodge Ram, trucks and vans

** Ram Pickup, produced by Ram Trucks

Ram, ram, or RAM may also ref ...

, 4KB FeRAM, 16KB ROM

Rom, or ROM may refer to:

Biomechanics and medicine

* Risk of mortality, a medical classification to estimate the likelihood of death for a patient

* Rupture of membranes, a term used during pregnancy to describe a rupture of the amniotic sac

* ...

Theoretical performance

*Floating-point

In computing, floating-point arithmetic (FP) is arithmetic on subsets of real numbers formed by a ''significand'' (a Sign (mathematics), signed sequence of a fixed number of digits in some Radix, base) multiplied by an integer power of that ba ...

: 6.2 billion single-precision (32-bit) floating-point operations per second

Floating point operations per second (FLOPS, flops or flop/s) is a measure of computer performance in computing, useful in fields of scientific computations that require floating-point calculations.

For such cases, it is a more accurate measur ...

* Perspective transformation: 66 million polygons per second

* With lighting

Lighting or illumination is the deliberate use of light to achieve practical or aesthetic effects. Lighting includes the use of both artificial light sources like lamps and light fixtures, as well as natural illumination by capturing daylight. ...

and fog: 36 million polygons per second

* Bézier surface patches: 16 million polygons per second

* Image decompression: 150 million pixel

In digital imaging, a pixel (abbreviated px), pel, or picture element is the smallest addressable element in a Raster graphics, raster image, or the smallest addressable element in a dot matrix display device. In most digital display devices, p ...

s per second

See also

*Graphics card

A graphics card (also called a video card, display card, graphics accelerator, graphics adapter, VGA card/VGA, video adapter, display adapter, or colloquially GPU) is a computer expansion card that generates a feed of graphics output to a displa ...

* Graphics processing unit

A graphics processing unit (GPU) is a specialized electronic circuit designed for digital image processing and to accelerate computer graphics, being present either as a discrete video card or embedded on motherboards, mobile phones, personal ...

* Computer graphics

Computer graphics deals with generating images and art with the aid of computers. Computer graphics is a core technology in digital photography, film, video games, digital art, cell phone and computer displays, and many specialized applications. ...

* List of computer graphics and descriptive geometry topics

* Cell microprocessor

The Cell Broadband Engine (Cell/B.E.) is a 64-bit multi-core processor and microarchitecture developed by Sony, Toshiba, and IBM—an alliance known as "STI". It combines a general-purpose PowerPC core, called the Power Processing Element (PPE), ...

, a design inspired by the Emotion Engine's CPU+VU0/VU1 arrangement, used in the PlayStation 3

The PlayStation 3 (PS3) is a home video game console developed and marketed by Sony Computer Entertainment (SCE). It is the successor to the PlayStation 2, and both are part of the PlayStation brand of consoles. The PS3 was first released on ...

References

References

* * {{MIPS microprocessors MIPS implementations PlayStation 2 Sony semiconductors