|

Translation Lookaside Buffer

A translation lookaside buffer (TLB) is a memory CPU cache, cache that stores the recent translations of virtual memory address to a physical memory Memory_address, location. It is used to reduce the time taken to access a user memory location. It can be called an address-translation cache. It is a part of the chip's Memory management unit, memory-management unit (MMU). A TLB may reside between the Central processing unit, CPU and the CPU cache, between CPU cache and the main memory or between the different levels of the multi-level cache. The majority of desktop, laptop, and server processors include one or more TLBs in the memory-management hardware, and it is nearly always present in any processor that uses Memory paging, paged or Memory segmentation, segmented virtual memory. The TLB is sometimes implemented as content-addressable memory (CAM). The CAM search key is the virtual address, and the search result is a physical address. If the requested address is present in the TLB ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CPU Cache

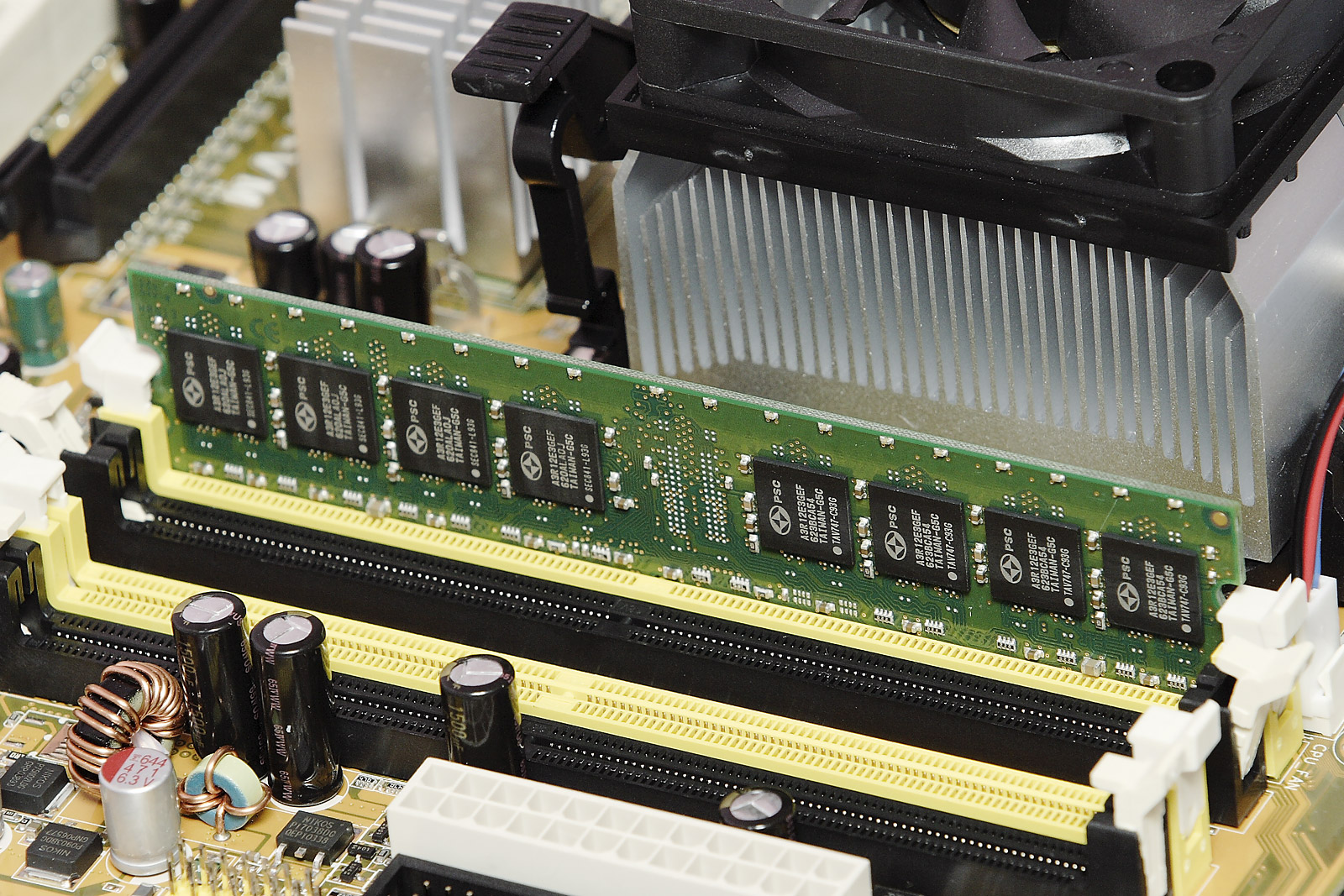

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (M ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Primary Storage

Computer data storage or digital data storage is a technology consisting of computer components and recording media that are used to retain digital data. It is a core function and fundamental component of computers. The central processing unit (CPU) of a computer is what manipulates data by performing computations. In practice, almost all computers use a storage hierarchy, which puts fast but expensive and small storage options close to the CPU and slower but less expensive and larger options further away. Generally, the fast technologies are referred to as "memory", while slower persistent technologies are referred to as "storage". Even the first computer designs, Charles Babbage's Analytical Engine and Percy Ludgate's Analytical Machine, clearly distinguished between processing and memory (Babbage stored numbers as rotations of gears, while Ludgate stored numbers as displacements of rods in shuttles). This distinction was extended in the Von Neumann architecture, whe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Skylake (microarchitecture)

Skylake is Intel's codename for its sixth generation Core microprocessor family that was launched on August 5, 2015, succeeding the Broadwell microarchitecture. Skylake is a microarchitecture redesign using the same 14 nm manufacturing process technology as its predecessor, serving as a tock in Intel's tick–tock manufacturing and design model. According to Intel, the redesign brings greater CPU and GPU performance and reduced power consumption. Skylake CPUs share their microarchitecture with Kaby Lake, Coffee Lake, Whiskey Lake, and Comet Lake CPUs. Skylake is the last Intel platform on which Windows earlier than Windows 10 are officially supported by Microsoft, although enthusiast-created modifications are available that disabled the Windows Update check and allowed Windows 8.1 and earlier to continue to receive Windows Updates on this and later platforms. Some of the processors based on the Skylake microarchitecture are marketed as sixth-generation Core. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tom's Hardware

''Tom's Hardware'' is an online publication owned by Future plc and focused on technology. It was founded in 1996 by Thomas Pabst. It provides articles, news, price comparisons, videos and reviews on computer hardware and high technology. The site features coverage on CPUs, motherboards, RAM, PC cases, graphic cards, display technology, power supplies and displays, storage, smartphones, tablets, gaming, consoles, and computer peripherals. ''Tom's Hardware'' has a forum and featured blogs. History ''Tom's Hardware'' was founded in 1996 as ''Tom's Hardware Guide'' in Canada by Thomas Pabst. It started using the domain tomshardware.com in September 1997 and was followed by several foreign language versions, including Italian, French, Finnish and Russian based on franchise agreements. While the initial testing labs were in Germany and California, much of ''Tom's Hardware'''s testing now occurs in New York and a facility in Ogden, Utah owned by its parent company. In April 20 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nehalem (microarchitecture)

Nehalem is the codename for Intel's 45 nm microarchitecture released in November 2008. It was used in the first generation of the Intel Core i5 and i7 processors, and succeeds the older Core microarchitecture used on Core 2 processors. The term "Nehalem" comes from the Nehalem River. Nehalem is built on the 45 nm process, is able to run at higher clock speeds without sacrificing efficiency, and is more energy-efficient than Penryn microprocessors. Hyper-threading is reintroduced, along with a reduction in L2 cache size, as well as an enlarged L3 cache that is shared among all cores. Nehalem is an architecture that differs radically from NetBurst, while retaining some of the latter's minor features. Nehalem later received a die-shrink to 32 nm with Westmere, and was fully succeeded by "second-generation" Sandy Bridge in January 2011. Technology * Cache line block on L2/L3 cache was reduced from 128 bytes in NetBurst & Merom/Penryn to 64 bytes per line in this gene ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California, and Delaware General Corporation Law, incorporated in Delaware. Intel designs, manufactures, and sells computer components such as central processing units (CPUs) and related products for business and consumer markets. It is one of the world's List of largest semiconductor chip manufacturers, largest semiconductor chip manufacturers by revenue, and ranked in the Fortune 500, ''Fortune'' 500 list of the List of largest companies in the United States by revenue, largest United States corporations by revenue for nearly a decade, from 2007 to 2016 Fiscal year, fiscal years, until it was removed from the ranking in 2018. In 2020, it was reinstated and ranked 45th, being the List of Fortune 500 computer software and information companies, 7th-largest technology company in the ranking. It was one of the first companies listed on Nasdaq. Intel supplies List of I ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cache Line

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) wh ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Thrashing (computer Science)

In computer science, thrashing occurs in a system with virtual memory when a computer's real storage resources are ''overcommitted'', leading to a constant state of paging and page faults, slowing most application-level processing. This causes the performance of the computer to degrade or even collapse. The situation can continue indefinitely until the user closes some running applications or the active processes free up additional virtual memory resources. After initialization, most programs operate on a small number of code and data pages compared to the total memory the program requires. The pages most frequently accessed at any point are called the working set, which may change over time. When the working set is not significantly greater than the system's total number of real storage ''page frames'', virtual memory systems work most efficiently, and an insignificant amount of computing is spent resolving page faults. As the total of the working sets grows, resolving page fa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Working Set

Working set is a concept in computer science which defines the amount of memory that a process (computing), process requires in a given time interval. Definition Peter_J._Denning, Peter Denning (1968) defines "the working set of information W(t, \tau) of a process (computing), process at time t to be the collection of information referenced by the process during the process time interval (t - \tau, t)". Typically the units of information in question are considered to be page (computer memory), memory pages. This is suggested to be an approximation of the set of pages that the process will access in the future (say during the next \tau time units), and more specifically is suggested to be an indication of what pages ought to be kept in main memory to allow most progress to be made in the execution of that process. Rationale The effect of the choice of what pages to be kept in main memory (as distinct from being ''paged out'' to auxiliary storage) is important: if too many pages o ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Page Fault

In computing, a page fault is an exception that the memory management unit (MMU) raises when a process accesses a memory page without proper preparations. Accessing the page requires a mapping to be added to the process's virtual address space. Furthermore, the actual page contents may need to be loaded from a back-up, e.g. a disk. The MMU detects the page fault, but the operating system's kernel handles the exception by making the required page accessible in the physical memory or denying an illegal memory access. Valid page faults are common and necessary to increase the amount of memory available to programs in any operating system that uses virtual memory, such as Windows, macOS, and the Linux kernel. Types Minor page fault If the page is loaded in memory at the time the fault is generated, but is not marked in the memory management unit as being loaded in memory, then it is called a ''minor'' or ''soft'' page fault. The page fault handler in the operating system m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Steps In A Translation Lookaside Buffer

Step(s) or STEP may refer to: Common meanings * Steps, making a staircase * Walking * Dance move * Military step, or march ** Marching Arts Films and television * ''Steps'' (TV series), Hong Kong * ''Step'' (film), US, 2017 Literature * ''Steps'' (novel), by Jerzy Kosinski * Systematic Training for Effective Parenting, a book series Music * Step (music), pitch change * Steps (pop group), UK * ''Step'' (Kara album), 2011, South Korea ** "Step" (Kara song) * ''Step'' (Meg album), 2007, Japan * "Step" (Vampire Weekend song) * "Step" (ClariS song) Organizations * STEP (company), Belgium * Society of Trust and Estate Practitioners, international professional body for advisers who specialise in inheritance and succession planning * Board on Science, Technology, and Economic Policy of the U.S. National Academies * Solving the E-waste Problem, a UN organization Science, technology, and mathematics * Step (software), a physics simulator in KDE * Step function, in mathema ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |