|

Xtrace

strace is a diagnostic, debugging and instructional userspace utility for Linux. It is used to monitor and tamper with interactions between processes and the Linux kernel, which include system calls, signal deliveries, and changes of process state. The operation of strace is made possible by the kernel feature known as ptrace. Some Unix-like systems provide other diagnostic tools similar to strace, such as truss. History Strace was originally written for SunOS by Paul Kranenburg in 1991, according to its copyright notice, and published early in 1992, in volume three of comp.sources.sun. The initial README file contained the following: is a system call tracer for Sun(tm) systems much like the Sun supplied program . is a useful utility to sort of debug programs for which no source is available which unfortunately includes almost all of the Sun supplied system software. Later, Branko Lankester ported this version to Linux, releasing his version in November 1992 with th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

C (programming Language)

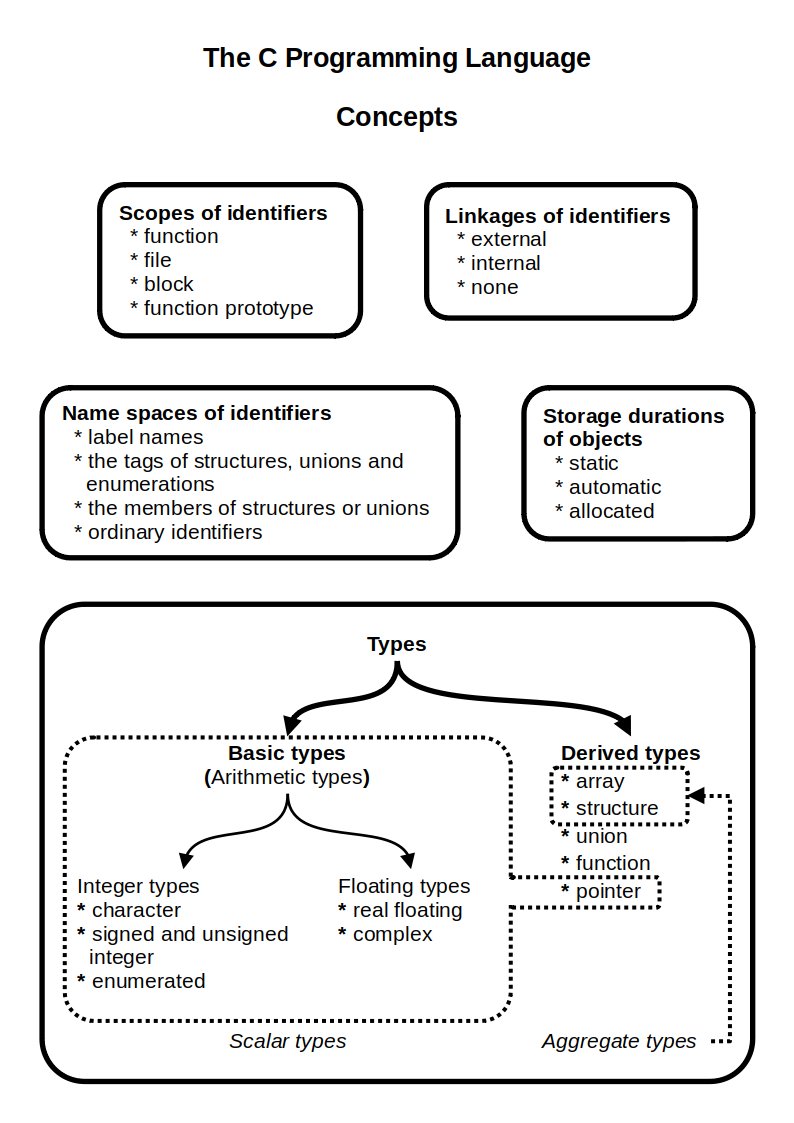

C (''pronounced'' '' – like the letter c'') is a general-purpose programming language. It was created in the 1970s by Dennis Ritchie and remains very widely used and influential. By design, C's features cleanly reflect the capabilities of the targeted Central processing unit, CPUs. It has found lasting use in operating systems code (especially in Kernel (operating system), kernels), device drivers, and protocol stacks, but its use in application software has been decreasing. C is commonly used on computer architectures that range from the largest supercomputers to the smallest microcontrollers and embedded systems. A successor to the programming language B (programming language), B, C was originally developed at Bell Labs by Ritchie between 1972 and 1973 to construct utilities running on Unix. It was applied to re-implementing the kernel of the Unix operating system. During the 1980s, C gradually gained popularity. It has become one of the most widely used programming langu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

OpenRISC

OpenRISC is a project to develop a series of open-source hardware based central processing units (CPUs) on established reduced instruction set computer (RISC) principles. It includes an instruction set architecture (ISA) using an open-source license. It is the original flagship project of the OpenCores community. The first (and only) architectural description is for the OpenRISC 1000 ("OR1k"), describing a family of 32-bit and 64-bit processors with optional floating-point arithmetic and vector processing support. The OpenRISC 1200 implementation of this specification was designed by Damjan Lampret in 2000, written in the Verilog hardware description language (HDL). The later mor1kx implementation, which has some advantages compared to the OR 1200, was designed by Julius Baxter and is also written in Verilog. Software simulators also exist which implement the OR1k specification. The hardware design was released under the GNU Lesser General Public License (LGPL), while the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

English Language

English is a West Germanic language that developed in early medieval England and has since become a English as a lingua franca, global lingua franca. The namesake of the language is the Angles (tribe), Angles, one of the Germanic peoples that Anglo-Saxon settlement of Britain, migrated to Britain after its End of Roman rule in Britain, Roman occupiers left. English is the list of languages by total number of speakers, most spoken language in the world, primarily due to the global influences of the former British Empire (succeeded by the Commonwealth of Nations) and the United States. English is the list of languages by number of native speakers, third-most spoken native language, after Mandarin Chinese and Spanish language, Spanish; it is also the most widely learned second language in the world, with more second-language speakers than native speakers. English is either the official language or one of the official languages in list of countries and territories where English ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Xtensa

Tensilica Inc. was a company based in Silicon Valley that developed semiconductor intellectual property (SIP) cores. Tensilica was founded in 1997 by Chris Rowen. In April 2013, the company was acquired by Cadence Design Systems for approximately $326 million. Products Cadence Tensilica develops SIP blocks to be included in chip (IC) designs of products of their licensees, such as system on a chip architectures for embedded systems. Tensilica processors are delivered as synthesizable RTL to aid integration with other designs. Xtensa configurable cores Xtensa processors range from small, low-power cache-less microcontroller to more performance-oriented SIMD processors, multiple-issue VLIW DSP cores, and neural network processors. Cadence standard DSPs are based on the Xtensa architecture. The architecture offers a user-customizable instruction set through automated customization tools that can extend the base instruction set, including and not limited to, addition of ne ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

X32 ABI

The x32 ABI is an application binary interface (ABI) and one of the interfaces of the Linux kernel. The x32 ABI provides 32-bit integers, long and pointers ( ILP32) on Intel and AMD 64-bit hardware. The ABI allows programs to take advantage of the benefits of x86-64 instruction set (larger number of CPU registers, better floating-point performance, faster position-independent code, shared libraries, function parameters passed via registers, faster syscall instruction) while using 32-bit pointers and thus avoiding the overhead of 64-bit pointers. Details Though the x32 ABI limits the program to a virtual address space of 4 GiB, it also decreases the memory footprint of the program by making pointers smaller. This can allow it to run faster by fitting more code ''and'' more data into cache. The best results during testing were with the 181.mcf SPEC CPU 2000 benchmark, in which the x32 ABI version was 40% faster than the x86-64 version. On average, x32 is 5–8% faster on the SPEC C ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

X86-64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit extension of the x86 instruction set architecture, instruction set. It was announced in 1999 and first available in the AMD Opteron family in 2003. It introduces two new operating modes: 64-bit mode and compatibility mode, along with a new four-level paging mechanism. In 64-bit mode, x86-64 supports significantly larger amounts of virtual memory and physical memory compared to its 32-bit computing, 32-bit predecessors, allowing programs to utilize more memory for data storage. The architecture expands the number of general-purpose registers from 8 to 16, all fully general-purpose, and extends their width to 64 bits. Floating-point arithmetic is supported through mandatory SSE2 instructions in 64-bit mode. While the older x87 FPU and MMX registers are still available, they are generally superseded by a set of sixteen 128-bit Processor register, vector registers (XMM registers). Each of these vector registers ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

TILE-Gx

TILE-Gx was a VLIW ISA multicore processor family designed by Tilera. It consisted of a mesh network that was expected to scale up to 100 cores, but only 72-core variants actually shipped. After a few acquisitions, Tilera's designs ended up in the hands of Nvidia, which ended production of TILE-Gx processors in 2022. In June 2018, the Linux kernel dropped support for this architecture. Tile-Gx processors were used in MikroTik's CCR1000 series routers, and MikroTik continues to support this architecture out-of-tree in its RouterOS Linux distribution. Product lineup Common features of TILE-Gx processors: * 64-bit VLIW RISC core (3-issue) * 4 MAC/cycle with SIMD extensions * L1 cache: 64 KB (32 KB data + 32 KB instruction) per core. * L2 cache: 256 KB per core. * L3 cache: Other core's L2 cache connected via mesh network. * 1, 2, or 4 ECC 72-bit DDR3 controllers. * Up to 24 PCIe 2.0 lanes. * Optional built-in crypto accelerator with 40 Gbit/s encry ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

TILEPro64

TILE''Pro''64 is a VLIW ISA multicore processor ( Tile processor) manufactured by Tilera. It consists of a cache-coherent mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor. The short-pipeline, in-order, three-issue cores implement a VLIW instruction set. Each core has a register file and three functional units: two integer arithmetic logic units and a load–store unit. Each of the cores ("tile") has its own L1 and L2 caches plus an overall virtual L3 cache which is an aggregate of all the L2 caches. A core is able to run a full operating system on its own or multiple cores can be used to run a symmetrical multi-processing operating system. TILE''Pro''64 has four DDR2 controllers at up to 800MT/s, two 10-gigabit Ethernet XAUI interfaces, two four-lane PCIe interfaces, and a "flexible" input/output interface, which can be software-configure ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

TILE64

TILE64 is a VLIW ISA multicore processor manufactured by Tilera. It consists of a mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor. The short-pipeline, in-order, three-issue cores implement a MIPS-inspired VLIW instruction set. Each core has a register file and three functional units: two integer arithmetic logic units and a load–store unit. Each of the cores ("tile") has its own L1 and L2 caches plus an overall virtual L3 cache which is an aggregate of all the L2 caches. A core is able to run a full operating system on its own or multiple cores can be used to run a symmetrical multi-processing operating system. TILE64 has four DDR2 controllers, two 10-gigabit Ethernet interfaces, two four-lane PCIe interfaces, and a "flexible" input/output interface, which can be software-configured to handle a number of protocols. The proce ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SuperH

SuperH (or SH) is a 32-bit reduced instruction set computing (RISC) instruction set architecture (ISA) developed by Hitachi and currently produced by Renesas. It is implemented by microcontrollers and microprocessors for embedded systems. At the time of introduction, SuperH was notable for having fixed-length 16-bit instructions in spite of its 32-bit architecture. Using smaller instructions had consequences: the processor register, register file was smaller and instructions were generally two-operand format. However for the market the SuperH was aimed at, this was a small price to pay for the improved memory and processor cache efficiency. Later versions of the design, starting with SH-5, included both 16- and 32-bit instructions, with the 16-bit versions mapping onto the 32-bit version inside the CPU. This allowed the machine code to continue using the shorter instructions to save memory, while not demanding the amount of instruction decoding logic needed if they were completely ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Z/Architecture

z/Architecture, initially and briefly called ESA Modal Extensions (ESAME), is IBM's 64-bit complex instruction set computer (CISC) instruction set architecture, implemented by its mainframe computers. IBM introduced its first z/Architecture-based system, the z900, in late 2000. Subsequent z/Architecture systems include the IBM z800, z990, z890, System z9, System z10, zEnterprise 196, zEnterprise 114, zEC12, zBC12, z13, z14, z15, z16, and z17. z/Architecture retains backward compatibility with previous 32-bit-data/31-bit-addressing architecture ESA/390 and its predecessors back to the 32-bit-data/24-bit-addressing System/360. The IBM z13 is the last z Systems server to support running an operating system in ESA/390 architecture mode. However, all 24-bit and 31-bit problem-state application programs originally written to run on the ESA/390 architecture will be unaffected by this change. Features z/Architecture includes almost all of the features of ESA/390, and a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |