|

X79

The Intel X79 ( codenamed ''Patsburg'') is a Platform Controller Hub (PCH) designed and manufactured by Intel for their LGA 2011 (Socket R) and LGA 2011-1 (Socket R2). Socket and chipset support CPUs targeted at the high-end desktop (HEDT) and enthusiast segments of the Intel product lineup: Core i7-branded and Xeon-branded processors from the Sandy Bridge and Ivy Bridge CPU architectures. The supported CPUs feature quad channel memory controllers, and a certain number of PCIe lanes, the chipset features additional PCIe lanes; it is designed to connect an Intel processor through a DMI 2.0 interface to peripheral devices. Features The first product was announced on November 14, 2011, for "Extreme" CPUs using the LGA 2011 socket. Features include: * 2× Serial ATA (SATA) 3.0 (6Gbit/s) ports & 4x SATA 2 (3Gbit/s) ports. * 8× PCI Express 2.0 lanes * 14 Universal Serial Bus (USB) 2.0 ports * Integrated Gigabit Ethernet MAC (Lewisville PHY) * Optional Intel Rapid Storage Tech ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LGA 2011

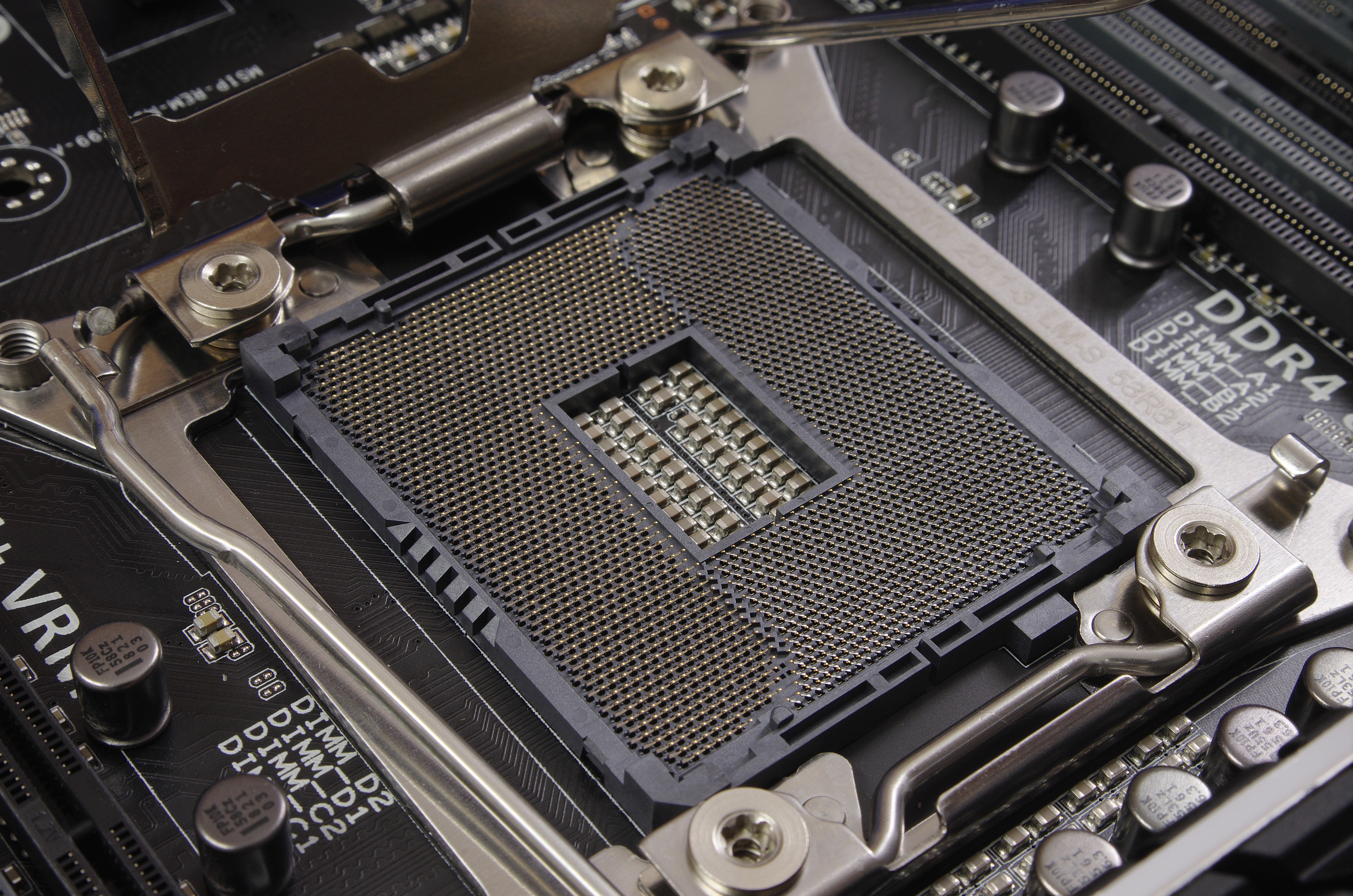

LGA 2011, also called ''Socket R'', is a CPU socket by Intel released on November 14, 2011. It launched along with LGA 1356 to replace its predecessor, LGA 1366 (Socket B) and LGA 1567. While LGA 1356 was designed for dual-processor or low-end servers, LGA 2011 was designed for high-end desktops and high-performance servers. The socket has 2011 protruding pins that touch contact points on the underside of the processor. The LGA 2011 socket uses QPI to connect the CPU to additional CPUs. DMI 2.0 is used to connect the processor to the PCH. The memory controller and 40 PCI Express (PCIe) lanes are integrated on the CPU. On a secondary processor an extra ×4 PCIe interface replaces the DMI interface. As with its predecessor LGA 1366, there is no provisioning for integrated graphics. This socket supports four DDR3 or DDR4 SDRAM memory channels with up to three unbuffered or registered DIMMs per channel, as well as up to 40 PCI Express 2.0 or 3.0 lanes. LGA ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LGA 2011-1

LGA 2011, also called ''Socket R'', is a CPU socket by Intel released on November 14, 2011. It launched along with LGA 1356 to replace its predecessor, LGA 1366 (Socket B) and LGA 1567. While LGA 1356 was designed for dual-processor or low-end servers, LGA 2011 was designed for high-end desktops and high-performance servers. The socket has 2011 protruding pins that touch contact points on the underside of the processor. The LGA 2011 socket uses QPI to connect the CPU to additional CPUs. DMI 2.0 is used to connect the processor to the PCH. The memory controller and 40 PCI Express (PCIe) lanes are integrated on the CPU. On a secondary processor an extra ×4 PCIe interface replaces the DMI interface. As with its predecessor LGA 1366, there is no provisioning for integrated graphics. This socket supports four DDR3 or DDR4 SDRAM memory channels with up to three unbuffered or registered DIMMs per channel, as well as up to 40 PCI Express 2.0 or 3.0 lanes. LGA&nb ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Intel Codenames

Intel has historically named integrated circuit (IC) development projects after geographical names of towns, rivers or mountains near the location of the Intel facility responsible for the IC. Many of these are in the American West, particularly in Oregon (where most of Intel's CPU projects are designed; see Project code name#Famous code names, famous codenames). As Intel's development activities have expanded, this nomenclature has expanded to Israel and India, and some older codenames refer to celestial bodies. The following table lists known Intel codenames along with a brief explanation of their meaning and their likely namesake, and the year of their earliest known public appearance. Most processors after a certain date were named after cities that could be found on a map of the United States. This was done for trademark considerations. Banias was the last of the non-US city names. Gesher was renamed to Sandy Bridge to comply with the new rule. Dothan is a city both in Israel ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Rapid Storage Technology

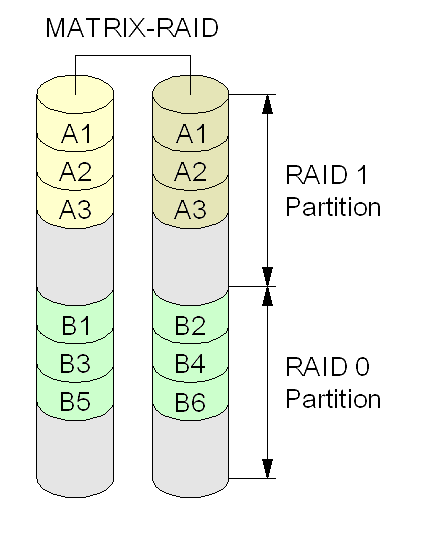

Intel Rapid Storage Technology (RST) is a driver SATA AHCI and a firmware-based RAID solution built into a wide range of Intel chipsets. Currently also is installed as a driver for Intel Optane temporary storage units. It contains two operation modes that do not follow the SATA standard, it follows two Intel specific modes. The name modes and the application that contains them have been renamed since the first version. Until 2010 it contains AHCI and Matrix RAID modes. The first mode is the Intel driver SATA normal and the latter mode is a fake RAID. Up to version 4 it is included on Intel Application Accelerator RAID Edition, between versions 5 and 8.9 it is included on Intel Matrix Storage Manager (IMSM), since version 9 it is included on Intel Rapid Storage Technology (IRST) preferring the driver modes to be named RST AHCI and RST AHCI RAID instead of Matrix RAID. The latter is also known as RST RAID mode, since it is the mode that Intel recommends to use, even if you are n ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Chipsets

This article provides a list of motherboard chipsets made by Intel, divided into three main categories: those that use the PCI bus for interconnection (the 4xx series), those that connect using specialized "hub links" (the 8xx series), and those that connect using PCI Express (the 9xx series). The chipsets are listed in chronological order. Pre-chipset situation An earlier chipset support for Intel 8085 microprocessor can be found at MCS-85 family section. Early IBM XT-compatible mainboards did not have a chipset yet, but relied instead on a collection of discrete TTL chips by Intel: * the 8284 clock generator * the 8288 bus controller * the 8254 Programmable Interval Timer * the 8255 parallel I/O interface * the 8259 Programmable Interrupt Controller * the 8237 DMA controller Early chipsets To integrate the functions needed on a mainboard into a smaller amount of ICs, Intel licensed the ZyMOS POACH chipset for its Intel 80286 and Intel 80386SX processors (the 8223 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Intel Chipsets

This article provides a list of motherboard chipsets made by Intel, divided into three main categories: those that use the PCI bus for interconnection (the 4xx series), those that connect using specialized "hub links" (the 8xx series), and those that connect using PCI Express (the 9xx series). The chipsets are listed in chronological order. Pre-chipset situation An earlier chipset support for Intel 8085 microprocessor can be found at MCS-85 family section. Early IBM XT-compatible mainboards did not have a chipset yet, but relied instead on a collection of discrete TTL chips by Intel: * the 8284 clock generator * the 8288 bus controller * the 8254 Programmable Interval Timer * the 8255 parallel I/O interface * the 8259 Programmable Interrupt Controller * the 8237 DMA controller Early chipsets To integrate the functions needed on a mainboard into a smaller amount of ICs, Intel licensed the ZyMOS POACH chipset for its Intel 80286 and Intel 80386SX processors (the 822 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Platform Controller Hub

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chips - a Northbridge (computing), northbridge and Southbridge (computing), southbridge, and first appeared in the Intel 5 Series. The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is used only when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCI Express, PCIe lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge. AMD has its equivalent for the PCH, known simply as a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel X99

Intel X99, List of Intel codenames, codenamed "Wellsburg", is a Platform Controller Hub (PCH) designed and manufactured by Intel, targeted at the Desktop computer, high-end desktop (HEDT) and enthusiast segments of the Intel product lineup. The X99 chipset supports both Intel Core i7 Extreme and Intel Xeon E5-16xx v3 and E5-26xx v3 Central processing unit, processors, which belong to the Haswell-E and Haswell-EP variants of the Haswell (microarchitecture), Haswell microarchitecture, respectively. All supported processors use the LGA 2011-v3 CPU socket, socket. The X99 chipset was released in late August 2014, while the supported processors were released in late August 2014 (Haswell-E) and early September 2014 (Haswell-EP). In May 2016, X99's processor support was extended to the Broadwell (microarchitecture), Broadwell variants of the Intel Core i7 Extreme and Intel Xeon E5-16xx v4 and E5-26xx v4 processors, which belong to the Broadwell-E a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ivy Bridge (microarchitecture)

Ivy Bridge is the codename for Intel's 22 nm microarchitecture used in the third generation of the Intel Core processors (Core i7, i5, i3). Ivy Bridge is a die shrink to 22 nm process based on FinFET ("3D") Tri-Gate transistors, from the former generation's 32 nm Sandy Bridge microarchitecture—also known as tick–tock model. The name is also applied more broadly to the Xeon and Core i7 Ivy Bridge-E series of processors released in 2013. Ivy Bridge processors are backward compatible with the Sandy Bridge platform, but such systems might require a firmware update (vendor specific). In 2011, Intel released the 7-series Panther Point chipsets with integrated USB 3.0 and SATA 3.0 to complement Ivy Bridge. Volume production of Ivy Bridge chips began in the third quarter of 2011. Quad-core and dual-core-mobile models launched on April 29, 2012 and May 31, 2012 respectively. Core i3 desktop processors, as well as the first 22 nm Pentium, wer ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sandy Bridge

Sandy Bridge is the codename for Intel's 32 nm microarchitecture used in the second generation of the Intel Core processors (Core i7, i5, i3). The Sandy Bridge microarchitecture is the successor to Nehalem and Westmere microarchitecture. Intel demonstrated a Sandy Bridge processor in 2009, and released first products based on the architecture in January 2011 under the Core brand. Sandy Bridge is manufactured in the 32 nm process and has a soldered contact with the die and IHS (Integrated Heat Spreader), while Intel's subsequent generation Ivy Bridge uses a 22 nm die shrink and a TIM (Thermal Interface Material) between the die and the IHS. Technology Intel demonstrated a Sandy Bridge processor with A1 stepping at 2 GHz during the Intel Developer Forum in September 2009. Upgraded features from Nehalem include: CPU * Intel Turbo Boost 2.0 * 32 KB data + 32 KB instruction L1 cache and 256 KB L2 cache per core * Shared L3 cache which inclu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Direct Media Interface

In computing, Direct Media Interface (DMI) is Intel's proprietary link between the northbridge and southbridge on a computer motherboard. It was first used between the 9xx chipsets and the ICH6, released in 2004. Previous Intel chipsets had used the Intel Hub Architecture to perform the same function, and server chipsets use a similar interface called ''Enterprise Southbridge Interface'' (ESI). While the "DMI" name dates back to ICH6, Intel mandates specific combinations of compatible devices, so the presence of a DMI interface does not guarantee by itself that a particular northbridge–southbridge combination is allowed. DMI shares many characteristics with PCI Express, using multiple lanes and differential signaling to form a point-to-point link. Most implementations use a ×4 link, while some mobile systems (e.g. 915GMS, 945GMS/GSE/GU and the Atom N450) use a ×2 link, halving the bandwidth. The original implementation provides 10 Gbit/s (1 GB/s) in each di ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel X58

The Intel X58 ( codenamed ''Tylersburg'') is an Intel chip designed to connect Intel processors with Intel QuickPath Interconnect (QPI) interface to peripheral devices. Supported processors implement the Nehalem microarchitecture and therefore have an integrated memory controller (IMC), so the X58 does not have a memory interface. Initially supported processors were the Core i7, but the chip also supported Nehalem and Westmere-based Xeon processors. Description The QuickPath architecture differs considerably from earlier Intel architectures, and is much closer to AMD's HyperTransport architecture. Except for the lack of a memory interface, the X58 is similar to the traditional northbridge: it communicates with the processor(s) via the high bandwidth QuickPath Interconnect, it communicates with the southbridge via Direct Media Interface (DMI), and it communicates with high bandwidth peripherals via PCI Express (PCIe). The X58 is not a ''memory controller hub'' (MCH), becaus ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |