|

Multi-level Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) whic ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hardware Cache

In computing, a cache ( ) is a hardware or software component that stores data so that future requests for that data can be served faster; the data stored in a cache might be the result of an earlier computation or a copy of data stored elsewhere. A ''cache hit'' occurs when the requested data can be found in a cache, while a ''cache miss'' occurs when it cannot. Cache hits are served by reading data from the cache, which is faster than recomputing a result or reading from a slower data store; thus, the more requests that can be served from the cache, the faster the system performs. To be cost-effective and to enable efficient use of data, caches must be relatively small. Nevertheless, caches have proven themselves in many areas of computing, because typical Application software, computer applications access data with a high degree of locality of reference. Such access patterns exhibit temporal locality, where data is requested that has been recently requested already, and memo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Titan (1963 Computer)

Titan was the prototype of the Atlas 2 computer developed by Ferranti and the University of Cambridge Mathematical Laboratory in Cambridge, England. It was designed starting in 1963, and in operation from 1964 to 1973. History In 1961, the University of Cambridge found itself unable to fund a suitably powerful computer for its needs at the time, so the University purchased from Ferranti the main Atlas processing units and then jointly designed the memory and peripheral equipment. The joint effort led to a cheaper and simpler version of the Atlas that Ferranti could market, leaving Cambridge with the prototype version, named Titan. The Atlas hardware arrived in Cambridge in 1963, although software design was already underway. David Wheeler was in charge of the joint effort between the University and Ferranti. In 1965 the Cambridge side of the team decided to add a time-sharing facility for Titan, necessitating the acquisition of additional hardware. When Titan came into full se ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

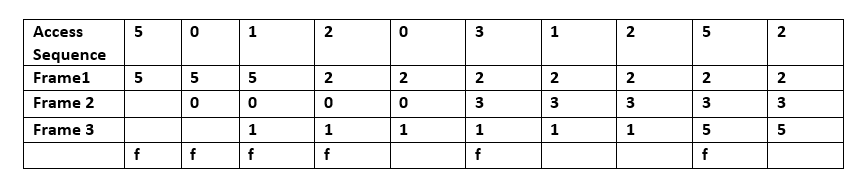

Least-recently Used

In computing, cache algorithms (also frequently called cache replacement algorithms or cache replacement policies) are optimizing instructions, or algorithms, that a computer program or a hardware-maintained structure can utilize in order to manage a cache of information stored on the computer. Caching improves performance by keeping recent or often-used data items in memory locations that are faster or computationally cheaper to access than normal memory stores. When the cache is full, the algorithm must choose which items to discard to make room for the new ones. Overview The average memory reference time is : T = m \times T_m + T_h + E where : m = miss ratio = 1 - (hit ratio) : T_m = time to make a main memory access when there is a miss (or, with multi-level cache, average memory reference time for the next-lower cache) : T_h= the latency: the time to reference the cache (should be the same for hits and misses) : E = various secondary effects, such as queuing effects in mult ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Atom

Intel Atom is the brand name for a line of IA-32 and x86-64 instruction set ultra-low-voltage processors by Intel Corporation designed to reduce electric consumption and power dissipation in comparison with ordinary processors of the Intel Core series. Atom is mainly used in netbooks, nettops, embedded applications ranging from health care to advanced robotics, mobile Internet devices (MIDs) and phones. The line was originally designed in 45 nm complementary metal–oxide–semiconductor (CMOS) technology and subsequent models, codenamed ''Cedar'', used a 32 nm process. The first generation of Atom processors are based on the Bonnell microarchitecture. On December 21, 2009, Intel announced the ''Pine Trail'' platform, including new Atom processor code-named ''Pineview'' (Atom N450), with total kit power consumption down 20%. On December 28, 2011, Intel updated the Atom line with the ''Cedar'' processors. In December 2012, Intel launched the 64-bit ''Centerton'' family of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ice Lake (microprocessor)

Ice Lake is Intel's codename for the 10th generation Intel Core mobile and 3rd generation Xeon Scalable server processors based on the Sunny Cove microarchitecture. Ice Lake represents an Architecture step in Intel's Process-Architecture-Optimization model. Produced on the second generation of Intel's 10 nm process, 10 nm+, Ice Lake is Intel's second microarchitecture to be manufactured on the 10 nm process, following the limited launch of Cannon Lake in 2018. However, Intel altered their naming scheme in 2020 for the 10 nm process. In this new naming scheme, Ice Lake's manufacturing process is called simply 10 nm, without any appended pluses. Ice Lake CPUs are sold together with the 14 nm Comet Lake CPUs as Intel's "10th Generation Core" product family. There are no Ice Lake desktop or high-power mobile processors; Comet Lake fulfills this role. Sunny Cove-based Xeon Scalable CPUs (codenamed "Ice Lake-SP") officially launched on April 6, 2021 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Z13 (microprocessor)

The z13 is a microprocessor made by IBM for their z13 mainframe computers, announced on January 14, 2015. Manufactured at GlobalFoundries' East Fishkill, New York fabrication plant (formerly IBM's own plant). IBM stated that it is the world's fastest microprocessor and is about 10% faster than its predecessor the zEC12 in general single-threaded computing, but significantly more when doing specialized tasks. The IBM z13 is the last z Systems server to support running an operating system in ESA/390 architecture mode. However, all 24-bit and 31-bit problem-state application programs originally written to run on the ESA/390 architecture are unaffected by this change. Description The Processor Unit chip (PU chip) has an area of 678 mm2 and contains 3.99 billion transistors. It is fabricated using IBM's 22 nm CMOS silicon on insulator fabrication process, using 17 metal layers and supporting speeds of 5.0 GHz, which is less than its predecessor, the zEC12. The PU c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM ZEC12 (microprocessor)

The zEC12 microprocessor (''zEnterprise EC12'' or just ''z12'') is a chip made by IBM for their zEnterprise EC12 and zEnterprise BC12 mainframe computers, announced on August 28, 2012. It is manufactured at the East Fishkill, New York fabrication plant (previously owned by IBM but production will continue for ten years by new owner GlobalFoundries). The processor began shipping in the fall of 2012. IBM stated that it was the world's fastest microprocessor and is about 25% faster than its predecessor the z196. Description The chip measures 597.24 mm2 and consists of 2.75 billion transistors fabricated in IBM's 32 nm CMOS silicon on insulator fabrication process, supporting speeds of 5.5 GHz, the highest clock speed CPU ever produced for commercial sale. The processor implements the CISC z/Architecture with a superscalar, out-of-order pipeline and some new instructions mainly related to transactional execution. The cores have numerous other enhancements such as ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Core 2 Duo

Intel Core is a line of streamlined midrange consumer, workstation and enthusiast computer central processing units (CPUs) marketed by Intel Corporation. These processors displaced the existing mid- to high-end Pentium processors at the time of their introduction, moving the Pentium to the entry level. Identical or more capable versions of Core processors are also sold as Xeon processors for the server and workstation markets. The lineup of Core processors includes the Intel Core i3, Intel Core i5, Intel Core i7, and Intel Core i9, along with the X-series of Intel Core CPUs. Outline Although Intel Core is a brand that promises no internal consistency or continuity, the processors within this family have been, for the most part, broadly similar. The first products receiving this designation were the Core Solo and Core Duo Yonah processors for mobile from the Pentium M design tree, fabricated at 65 nm and brought to market in January 2006. These are substantially differ ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Mebibyte

The byte is a unit of digital information that most commonly consists of eight bits. Historically, the byte was the number of bits used to encode a single character of text in a computer and for this reason it is the smallest addressable unit of memory in many computer architectures. To disambiguate arbitrarily sized bytes from the common 8-bit definition, network protocol documents such as The Internet Protocol () refer to an 8-bit byte as an octet. Those bits in an octet are usually counted with numbering from 0 to 7 or 7 to 0 depending on the bit endianness. The first bit is number 0, making the eighth bit number 7. The size of the byte has historically been hardware-dependent and no definitive standards existed that mandated the size. Sizes from 1 to 48 bits have been used. The six-bit character code was an often-used implementation in early encoding systems, and computers using six-bit and nine-bit bytes were common in the 1960s. These systems often had memory words ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Kibibyte

The byte is a unit of digital information that most commonly consists of eight bits. Historically, the byte was the number of bits used to encode a single character of text in a computer and for this reason it is the smallest addressable unit of memory in many computer architectures. To disambiguate arbitrarily sized bytes from the common 8-bit definition, network protocol documents such as The Internet Protocol () refer to an 8-bit byte as an octet. Those bits in an octet are usually counted with numbering from 0 to 7 or 7 to 0 depending on the bit endianness. The first bit is number 0, making the eighth bit number 7. The size of the byte has historically been hardware-dependent and no definitive standards existed that mandated the size. Sizes from 1 to 48 bits have been used. The six-bit character code was an often-used implementation in early encoding systems, and computers using six-bit and nine-bit bytes were common in the 1960s. These systems often had memory words ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Dynamic Random-access Memory

Dynamic random-access memory (dynamic RAM or DRAM) is a type of random-access semiconductor memory that stores each bit of data in a memory cell, usually consisting of a tiny capacitor and a transistor, both typically based on metal-oxide-semiconductor (MOS) technology. While most DRAM memory cell designs use a capacitor and transistor, some only use two transistors. In the designs where a capacitor is used, the capacitor can either be charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1. The electric charge on the capacitors gradually leaks away; without intervention the data on the capacitor would soon be lost. To prevent this, DRAM requires an external ''memory refresh'' circuit which periodically rewrites the data in the capacitors, restoring them to their original charge. This refresh process is the defining characteristic of dynamic random-access memory, in contrast to static random-access memory (SRAM ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-core Processor

A multi-core processor is a microprocessor on a single integrated circuit with two or more separate processing units, called cores, each of which reads and executes program instructions. The instructions are ordinary CPU instructions (such as add, move data, and branch) but the single processor can run instructions on separate cores at the same time, increasing overall speed for programs that support multithreading or other parallel computing techniques. Manufacturers typically integrate the cores onto a single integrated circuit die (known as a chip multiprocessor or CMP) or onto multiple dies in a single chip package. The microprocessors currently used in almost all personal computers are multi-core. A multi-core processor implements multiprocessing in a single physical package. Designers may couple cores in a multi-core device tightly or loosely. For example, cores may or may not share caches, and they may implement message passing or shared-memory inter-core communica ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |