|

Machine State Register

A machine state register (MSR) is one of three process control registers present in the PowerPC processor architecture. Processors The implementation details of the machine state register will vary from model to model. Below are two representative implementations, the 32-bit Freescale e200z3 PowerPC core and the 64-bit IBM PowerPC. e200z3 PowerPC core Uses of the machine state register This 32-bit register either controls and/or reports several important processor states. Reading and writing the machine state register The contents of the register may be read using the ''move from machine state register'' (mfmsr) instruction and may be modified by executing the ''return from interrupt'' (rfi, rfci, rfdi), ''system call'' (sc) and ''move to machine state register'' (mtmsr) instructions. PowerPC Uses of the machine state register This 64-bit register either controls and/or reports several important processor states. {, class="wikitable" , - ! Mnemonic !! Descri ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

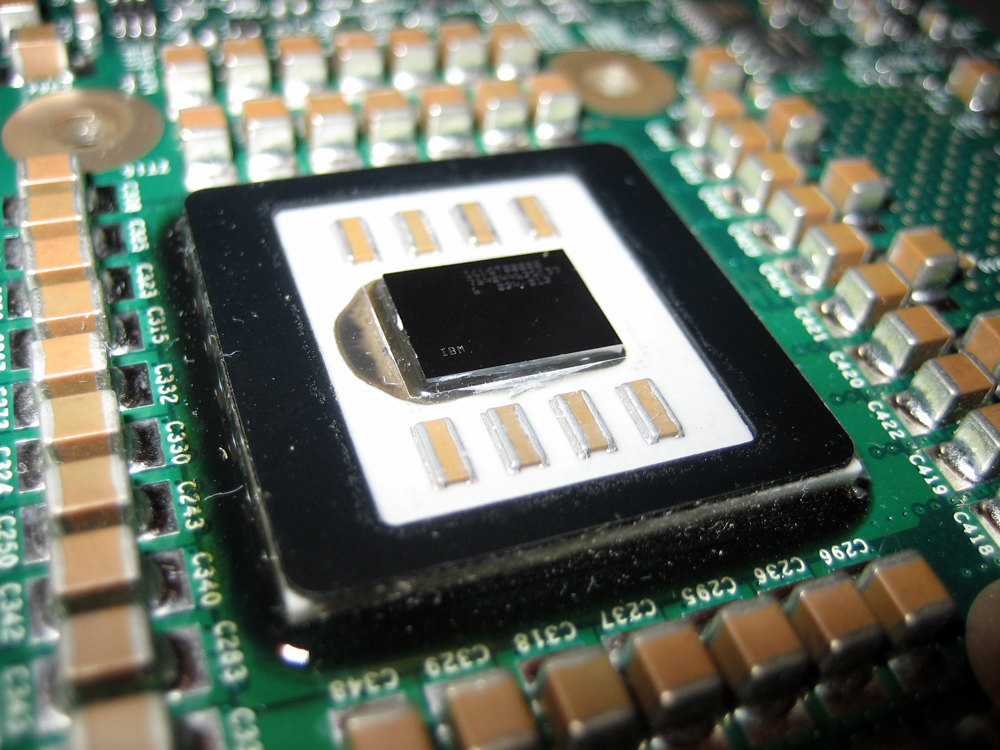

PowerPC

PowerPC (with the backronym Performance Optimization With Enhanced RISC – Performance Computing, sometimes abbreviated as PPC) is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple– IBM–Motorola alliance, known as AIM. PowerPC, as an evolving instruction set, has been named Power ISA since 2006, while the old name lives on as a trademark for some implementations of Power Architecture–based processors. PowerPC was the cornerstone of AIM's PReP and Common Hardware Reference Platform (CHRP) initiatives in the 1990s. Originally intended for personal computers, the architecture is well known for being used by Apple's Power Macintosh, PowerBook, iMac, iBook, eMac, Mac Mini, and Xserve lines from 1994 until 2005, when Apple migrated to Intel's x86. It has since become a niche in personal computers, but remains popular for embedded and high-performance processors. Its use in 7th generation of video game consol ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Freescale

Freescale Semiconductor, Inc. was an American semiconductor manufacturer. It was created by the divestiture of the Semiconductor Products Sector of Motorola in 2004. Freescale focused their integrated circuit products on the automotive, embedded and communications markets. It was bought by a private investor group in 2006, and subsequently merged into NXP Semiconductors in 2015. History As of 2003, Motorola Semiconductor Products Sector earned US$5.0 billion in semiconductor sales in 2002 (out of US$27 billion sales for all of Motorola). Motorola announced that their semiconductor division would be divested on October 6, 2003, to create Freescale. Freescale completed its Initial public offering (IPO) on July 16, 2004, at a price of US$13. In its announcement, it estimated the stock price to be US$17.50- 19.50 but following a cooling of the market towards tech stocks, it lowered its price to US$13. Existing shareholders of Motorola stock received 0.110415 shares of Freescale ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC E200

The PowerPC e200 is a family of 32-bit Power ISA microprocessor cores developed by Freescale for primary use in automotive and industrial control systems. The cores are designed to form the CPU part in system-on-a-chip (SoC) designs with speed ranging up to 600 MHz, thus making them ideal for embedded applications. The e200 core is developed from the MPC5xx family processors, which in turn is derived from the MPC8xx core in the PowerQUICC SoC processors. e200 adheres to the Power ISA v.2.03 as well as the previous ''Book E'' specification. All e200 core based microprocessors are named in the MPC55xx and MPC56xx/JPC56x scheme, not to be confused with the MPC52xx processors which is based on the PowerPC e300 core. In April 2007 Freescale and IPextreme opened up the e200 cores for licensing to other manufacturers. Continental AG and Freescale are developing SPACE, a tri-core e200 based processor designed for electronic brake systems in cars. STMicroelectronics and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Userspace

A modern computer operating system usually segregates virtual memory into user space and kernel space. Primarily, this separation serves to provide memory protection and hardware protection from malicious or errant software behaviour. Kernel space is strictly reserved for running a privileged operating system kernel, kernel extensions, and most device drivers. In contrast, user space is the memory area where application software and some drivers execute. Overview The term user space (or userland) refers to all code that runs outside the operating system's kernel. User space usually refers to the various programs and libraries that the operating system uses to interact with the kernel: software that performs input/output, manipulates file system objects, application software, etc. Each user space process normally runs in its own virtual memory space, and, unless explicitly allowed, cannot access the memory of other processes. This is the basis for memory protection in tod ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CPU Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Interrupts

In digital computers, an interrupt (sometimes referred to as a trap) is a request for the processor to ''interrupt'' currently executing code (when permitted), so that the event can be processed in a timely manner. If the request is accepted, the processor will suspend its current activities, save its state, and execute a function called an ''interrupt handler'' (or an ''interrupt service routine'', ISR) to deal with the event. This interruption is often temporary, allowing the software to resume normal activities after the interrupt handler finishes, although the interrupt could instead indicate a fatal error. Interrupts are commonly used by hardware devices to indicate electronic or physical state changes that require time-sensitive attention. Interrupts are also commonly used to implement computer multitasking, especially in real-time computing. Systems that use interrupts in these ways are said to be interrupt-driven. Types Interrupt signals may be issued in response to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ring (computer Security)

In computer science, hierarchical protection domains, often called protection rings, are mechanisms to protect data and functionality from faults (by improving fault tolerance) and malicious behavior (by providing computer security). Computer operating systems provide different levels of access to resources. A protection ring is one of two or more hierarchical ''levels'' or ''layers'' of privilege within the architecture of a computer system. This is generally hardware-enforced by some CPU architectures that provide different CPU modes at the hardware or microcode level. Rings are arranged in a hierarchy from most privileged (most trusted, usually numbered zero) to least privileged (least trusted, usually with the highest ring number). Ring 0 is the level with the most privileges and allows direct interaction with the physical hardware such as certain CPU functionality and chips on the motherboard. Special call gates between rings are provided to allow an outer ring to acces ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating Point

In computing, floating-point arithmetic (FP) is arithmetic that represents real numbers approximately, using an integer with a fixed precision, called the significand, scaled by an integer exponent of a fixed base. For example, 12.345 can be represented as a base-ten floating-point number: 12.345 = \underbrace_\text \times \underbrace_\text\!\!\!\!\!\!^ In practice, most floating-point systems use base two, though base ten ( decimal floating point) is also common. The term ''floating point'' refers to the fact that the number's radix point can "float" anywhere to the left, right, or between the significant digits of the number. This position is indicated by the exponent, so floating point can be considered a form of scientific notation. A floating-point system can be used to represent, with a fixed number of digits, numbers of very different orders of magnitude — such as the number of meters between galaxies or between protons in an atom. For this reason, floating-poi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Machine Check

A machine check exception (MCE) is a type of computer error that occurs when a problem involving the computer's hardware is detected. With most mass-market personal computers, an MCE indicates faulty or misconfigured hardware. The nature and causes of MCEs can vary by architecture and generation of system. In some designs, an MCE is always an unrecoverable error, that halts the machine, requiring a reboot. In other architectures, some MCEs may be non-fatal, such as for single-bit errors corrected by ECC memory. On some architectures, such as PowerPC, certain software bugs can cause MCEs, such as an invalid memory access. On other architectures, such as x86, MCEs typically originate from hardware only. Reporting Microsoft Windows On Microsoft Windows platforms, in the event of an unrecoverable MCEs, the system generates a BugCheck — also called a STOP error, or a Blue Screen of Death. More recent versions of Windows use the Windows Hardware Error Architecture (WHE ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC 970

The PowerPC 970, PowerPC 970FX, and PowerPC 970MP are 64-bit PowerPC processors from IBM introduced in 2002. When used in PowerPC-based Macintosh computers, Apple referred to them as the PowerPC G5. The 970 family was created through a collaboration between IBM and Apple. The project went under the codename GP-UL or Giga Processor Ultra Light, where Giga Processor was the codename for the POWER4 from which the core was derived. When Apple introduced the Power Mac G5, they stated that this was a five-year collaborative effort, with multi-generation roadmap. This forecast however was short-lived when Apple later had to retract its promise to deliver a 3 GHz processor only one year after its introduction. IBM was also unable to reduce power consumption to levels necessary for laptop computers. Ultimately, Apple only used three variants of the processor. IBM's JS20/JS21 blade modules and some low-end workstations and System p servers are based on the PowerPC 970. It is also ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Model-specific Register

A model-specific register (MSR) is any of various control registers in the x86 instruction set used for debugging, program execution tracing, computer performance monitoring, and toggling certain CPU features. History With the introduction of the 80386 processor, Intel began introducing "experimental" features that would not necessarily be present in future versions of the processor. The first of these were two "test registers" (TR6 and TR7) that enabled testing of the processor's translation lookaside buffer (TLB); a special variant of the instruction allowed moving to and from the test registers. Three additional test registers followed in the 80486 (TR3–TR5) that enabled testing of the processor's caches for code and data. None of these five registers were implemented in the subsequent Pentium processor; the special variant of generated an invalid opcode exception. With the introduction of the Pentium processor, Intel provided a pair of instructions ( and ) to access curre ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IA-32

IA-32 (short for "Intel Architecture, 32-bit", commonly called i386) is the 32-bit version of the x86 instruction set architecture, designed by Intel and first implemented in the 80386 microprocessor in 1985. IA-32 is the first incarnation of x86 that supports 32-bit computing; as a result, the "IA-32" term may be used as a metonym to refer to all x86 versions that support 32-bit computing. Within various programming language directives, IA-32 is still sometimes referred to as the "i386" architecture. In some other contexts, certain iterations of the IA-32 ISA are sometimes labelled i486, i586 and i686, referring to the instruction supersets offered by the 80486, the P5 and the P6 microarchitectures respectively. These updates offered numerous additions alongside the base IA-32 set including floating-point capabilities and the MMX extensions. Intel was historically the largest manufacturer of IA-32 processors, with the second biggest supplier having been AMD. During th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |