|

DDR-SDRAM

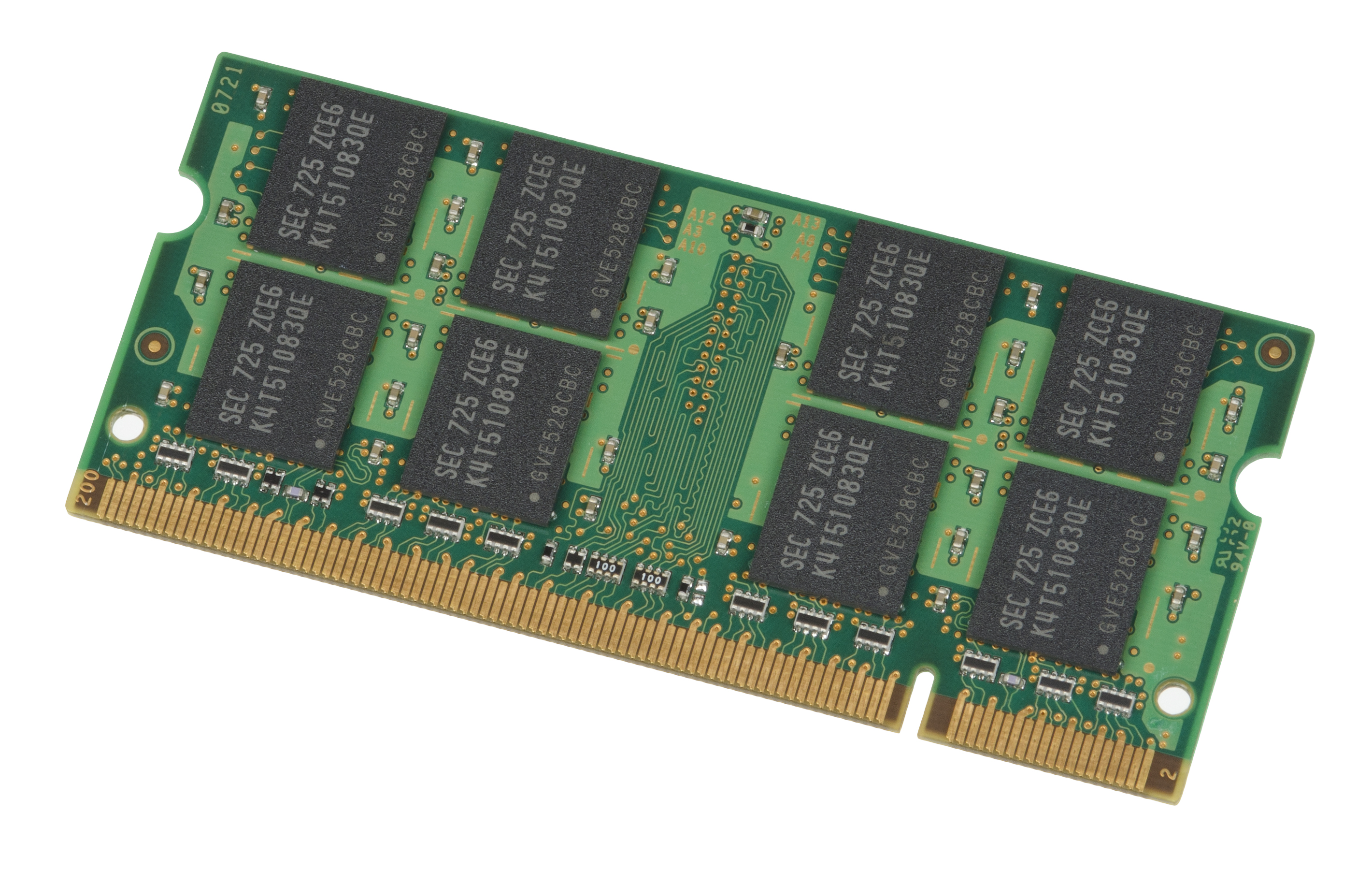

Double Data Rate Synchronous Dynamic Random-Access Memory (DDR SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) class of memory integrated circuits used in computers. DDR SDRAM, also retroactively called DDR1 SDRAM, has been superseded by DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM and DDR5 SDRAM. None of its successors are forward or backward compatible with DDR1 SDRAM, meaning DDR2, DDR3, DDR4 and DDR5 memory modules will not work in DDR1-equipped motherboards, and vice versa. Compared to single data rate ( SDR) SDRAM, the DDR SDRAM interface makes higher transfer rates possible by more strict control of the timing of the electrical data and clock signals. Implementations often have to use schemes such as phase-locked loops and self-calibration to reach the required timing accuracy. The interface uses double pumping (transferring data on both the rising and falling edges of the clock signal) to double data bus bandwidth without a corresponding increa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR5 SDRAM

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM, DDR5 was planned to reduce power consumption, while doubling bandwidth. The standard, originally targeted for 2018, was released on July 14, 2020. A new feature called Decision Feedback Equalization (DFE) enables I/O speed scalability for higher bandwidth and performance improvement. DDR5 supports more bandwidth than its predecessor, DDR4, with 4.8 gigabits per second possible, but not shipping at launch. DDR5 has about the same latency as DDR4 and DDR3. DDR5 octuples the maximum DIMM capacity from 64 GB to 512 GB. DDR5 also has higher frequencies than DDR4. Rambus announced a working DDR5 DIMM in September 2017. On November 15, 2018, SK Hynix announced completion of its first DDR5 RAM chip; it runs at 5200 MT/s at 1.1 V. In February 2019, SK Hynix announced a 6400 MT/s chip, the highest speed specified by the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR4 SDRAM

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth (" double data rate") interface. Released to the market in 2014, it is a variant of dynamic random-access memory (DRAM), of which some have been in use since the early 1970s, and a higher-speed successor to the DDR2 and DDR3 technologies. DDR4 is not compatible with any earlier type of random-access memory (RAM) due to different signaling voltage and physical interface, besides other factors. DDR4 SDRAM was released to the public market in Q2 2014, focusing on ECC memory, while the non-ECC DDR4 modules became available in Q3 2014, accompanying the launch of Haswell-E processors that require DDR4 memory. Features The primary advantages of DDR4 over its predecessor, DDR3, include higher module density and lower voltage requirements, coupled with higher data rate transfer speeds. The DDR4 standard allows for DIMMs of up ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR3 SDRAM

Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth (" double data rate") interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors. DDR3 is a DRAM interface specification. The actual DRAM arrays that store the data are similar to earlier types, with similar performance. The primary benefit of DDR3 SDRAM over its immediate predecessor DDR2 SDRAM, is its ability to transfer data at twice the rate (eight times the speed of its internal memory arrays), enabling higher bandwidth or peak data rates. The DDR3 standard permits DRAM chip capacities of up to 8 gigabits (Gbit), and up to four ranks ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR2 SDRAM

Double Data Rate 2 Synchronous Dynamic Random-Access Memory (DDR2 SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It superseded the original DDR SDRAM specification, and was itself superseded by DDR3 SDRAM (launched in 2007). DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR. In addition to double pumping the data bus as in DDR SDRAM (transferring data on the rising and falling edges of the bus clock signal), DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as DDR results in DDR2 being able to provide the same bandwidth but with better latency. Alternatively, DDR2 memory operating at twice the external data ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR3

Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth ("double data rate") interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors. DDR3 is a DRAM interface specification. The actual DRAM arrays that store the data are similar to earlier types, with similar performance. The primary benefit of DDR3 SDRAM over its immediate predecessor DDR2 SDRAM, is its ability to transfer data at twice the rate (eight times the speed of its internal memory arrays), enabling higher bandwidth or peak data rates. The DDR3 standard permits DRAM chip capacities of up to 8 gigabits (Gbit), and up to four ranks o ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR4

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth ("double data rate") interface. Released to the market in 2014, it is a variant of dynamic random-access memory (DRAM), of which some have been in use since the early 1970s, and a higher-speed successor to the DDR2 and DDR3 technologies. DDR4 is not compatible with any earlier type of random-access memory (RAM) due to different signaling voltage and physical interface, besides other factors. DDR4 SDRAM was released to the public market in Q2 2014, focusing on ECC memory, while the non-ECC DDR4 modules became available in Q3 2014, accompanying the launch of Haswell-E processors that require DDR4 memory. Features The primary advantages of DDR4 over its predecessor, DDR3, include higher module density and lower voltage requirements, coupled with higher data rate transfer speeds. The DDR4 standard allows for DIMMs of up t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR5

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth (" double data rate") interface. Released to the market in 2014, it is a variant of dynamic r ..., DDR5 was planned to reduce power consumption, while doubling Bandwidth (computing), bandwidth. The standard, originally targeted for 2018, was released on July 14, 2020. A new feature called Decision Feedback Equalization (DFE) enables I/O speed scalability for higher bandwidth and performance improvement. DDR5 supports more Bandwidth (computing), bandwidth than its predecessor, DDR4 SDRAM, DDR4, with 4.8 gigabits per second possible, but not shipping at launch. DDR5 has about the same memory timings, latency as DDR4 and DDR3. DDR5 octuples the maximum DIMM capac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Data Bus

In computer architecture, a bus (shortened form of the Latin '' omnibus'', and historically also called data highway or databus) is a communication system that transfers data between components inside a computer, or between computers. This expression covers all related hardware components (wire, optical fiber, etc.) and software, including communication protocols. Early computer buses were parallel electrical wires with multiple hardware connections, but the term is now used for any physical arrangement that provides the same logical function as a parallel electrical busbar. Modern computer buses can use both parallel and bit serial connections, and can be wired in either a multidrop (electrical parallel) or daisy chain topology, or connected by switched hubs, as in the case of Universal Serial Bus (USB). Background and nomenclature Computer systems generally consist of three main parts: * The central processing unit (CPU) that processes data, * The memory that holds the p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Phase-locked Loop

A phase-locked loop or phase lock loop (PLL) is a control system that generates an output signal whose phase is related to the phase of an input signal. There are several different types; the simplest is an electronic circuit consisting of a variable frequency oscillator and a phase detector in a feedback loop. The oscillator's frequency and phase are controlled proportionally by an applied voltage, hence the term voltage-controlled oscillator (VCO). The oscillator generates a periodic signal of a specific frequency, and the phase detector compares the phase of that signal with the phase of the input periodic signal, to adjust the oscillator to keep the phases matched. Keeping the input and output phase in lockstep also implies keeping the input and output frequencies the same. Consequently, in addition to synchronizing signals, a phase-locked loop can track an input frequency, or it can generate a frequency that is a multiple of the input frequency. These properties are use ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Clock Signal

In electronics and especially synchronous digital circuits, a clock signal (historically also known as ''logic beat'') oscillates between a high and a low state and is used like a metronome to coordinate actions of digital circuits. A clock signal is produced by a clock generator. Although more complex arrangements are used, the most common clock signal is in the form of a square wave with a 50% duty cycle, usually with a fixed, constant frequency. Circuits using the clock signal for synchronization may become active at either the rising edge, falling edge, or, in the case of double data rate, both in the rising and in the falling edges of the clock cycle. Digital circuits Most integrated circuits (ICs) of sufficient complexity use a clock signal in order to synchronize different parts of the circuit, cycling at a rate slower than the worst-case internal propagation delays. In some cases, more than one clock cycle is required to perform a predictable action. As ICs become mo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MB/s

In telecommunications, data-transfer rate is the average number of bits (bitrate), characters or symbols (baudrate), or data blocks per unit time passing through a communication link in a data-transmission system. Common data rate units are multiples of bits per second (bit/s) and bytes per second (B/s). For example, the data rates of modern residential high-speed Internet connections are commonly expressed in megabits per second (Mbit/s). Standards for unit symbols and prefixes Unit symbol The ISQ symbols for the bit and byte are ''bit'' and ''B'', respectively. In the context of data-rate units, one byte consists of 8 bits, and is synonymous with the unit octet. The abbreviation bps is often used to mean bit/s, so that when a ''1 Mbps'' connection is advertised, it usually means that the maximum achievable bandwidth is 1 Mbit/s (one million bits per second), which is 0.125 MB/s (megabyte per second), or about 0.1192 MiB/s (mebibyte per second). The Institu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Signal Integrity

Signal integrity or SI is a set of measures of the quality of an electrical signal. In digital electronics, a stream of binary values is represented by a voltage (or current) waveform. However, digital signals are fundamentally analog in nature, and all signals are subject to effects such as noise, distortion, and loss. Over short distances and at low bit rates, a simple conductor can transmit this with sufficient fidelity. At high bit rates and over longer distances or through various mediums, various effects can degrade the electrical signal to the point where errors occur and the system or device fails. Signal integrity engineering is the task of analyzing and mitigating these effects. It is an important activity at all levels of electronics packaging and assembly, from internal connections of an integrated circuit (IC), A survey of the field of electronic design automation. Portions of IC section of this article were derived (with permission) from Vol II, Chapter 21, ''Noise ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)