Larrabee (microarchitecture) on:

[Wikipedia]

[Google]

[Amazon]

Larrabee is the

Larrabee is the

Larrabee can be considered a hybrid between a

Larrabee can be considered a hybrid between a

Intel's

Intel's

Video of a raytracer running on one of the first Larrabee cards at IDF '09Whitepapers on LRBni, Physics Simulations and more using LarrabeeRasterization on LarrabeeA First Look at the Larrabee New Instructions (LRBni)C++ implementation of the Larrabee new instructionsGame Physics Performance on LarrabeeIntel's SIGGRAPH 2008 paper on LarrabeeTechgage.com - Discusses how Larrabee differs from normal GPUs, includes block diagram illustrationIntel's Larrabee Architecture Disclosure: A Calculated First Move

{{Intel processors, * Intel graphics Intel x86 microprocessors Intel microarchitectures Graphics cards X86 microarchitectures

Larrabee is the

Larrabee is the codename

A code name, call sign or cryptonym is a Code word (figure of speech), code word or name used, sometimes clandestinely, to refer to another name, word, project, or person. Code names are often used for military purposes, or in espionage. They may ...

for a cancelled GPGPU

General-purpose computing on graphics processing units (GPGPU, or less often GPGP) is the use of a graphics processing unit (GPU), which typically handles computation only for computer graphics, to perform computation in applications traditiona ...

chip that Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 seri ...

was developing separately from its current line of integrated graphics accelerators. It is named after either Mount Larrabee

Mount Larrabee is a Skagit Range mountain summit situated 1.4 mile south of the Canada–United States border, in the North Cascades of Washington (state), Washington state. It is located immediately southeast of American Border Peak within the ...

or Larrabee State Park

Larrabee State Park is a public recreation area located on Samish Bay on the western side of Chuckanut Mountain, south of the city of Bellingham, Washington. It was created in 1915 as Washington's first state park. The park covers and feat ...

in Whatcom County, Washington

Whatcom County is a county located in the northwestern corner of the U.S. state of Washington, bordered by the Canadian Lower Mainland (the Metro Vancouver and Fraser Valley Regional Districts of British Columbia) to the north, Okanogan Coun ...

, near the town of Bellingham. The chip was to be released in 2010 as the core of a consumer 3D graphics card

A graphics card (also called a video card, display card, graphics adapter, VGA card/VGA, video adapter, display adapter, or mistakenly GPU) is an expansion card which generates a feed of output images to a display device, such as a computer moni ...

, but these plans were cancelled due to delays and disappointing early performance figures. The project to produce a GPU retail product directly from the Larrabee research project was terminated in May 2010 and its technology was passed on to the Xeon Phi

Xeon Phi was a series of x86 manycore processors designed and made by Intel. It was intended for use in supercomputers, servers, and high-end workstations. Its architecture allowed use of standard programming languages and application program ...

. The Intel MIC

Xeon Phi was a series of x86 manycore processors designed and made by Intel. It was intended for use in supercomputers, servers, and high-end workstations. Its architecture allowed use of standard programming languages and application programm ...

multiprocessor architecture announced in 2010 inherited many design elements from the Larrabee project, but does not function as a graphics processing unit; the product is intended as a co-processor

A coprocessor is a computer processor used to supplement the functions of the primary processor (the CPU). Operations performed by the coprocessor may be floating-point arithmetic, graphics, signal processing, string processing, cryptography o ...

for high performance computing

High-performance computing (HPC) uses supercomputers and computer clusters to solve advanced computation problems.

Overview

HPC integrates systems administration (including network and security knowledge) and parallel programming into a multid ...

.

Almost a decade later, on June 12, 2018; the idea of an Intel dedicated GPU was revived again with Intel's desire to create a discrete GPU by 2020. This project would eventually become the Intel Xe

Intel Xe (stylized as Xe and pronounced as two separate letters, abbreviation for "eXascale for everyone"), earlier known unofficially as Gen12, is a GPU architecture developed by Intel.

Intel Xe includes a new instruction set architecture. Th ...

and Intel Arc

Intel Arc is a brand of graphics processing units designed by Intel. These are discrete GPUs mostly marketed for the high-margin PC gaming market. The brand also covers Intel's consumer graphics software and services.

Intel Arc is competing wit ...

series, released in September 2020 and March 2022, respectively - but both were unconnected to the work on the Larrabee project.

Project status

On December 4, 2009, Intel officially announced that the first-generation Larrabee would not be released as a consumer GPU product. Instead, it was to be released as a development platform for graphics andhigh-performance computing

High-performance computing (HPC) uses supercomputers and computer clusters to solve advanced computation problems.

Overview

HPC integrates systems administration (including network and security knowledge) and parallel programming into a mult ...

. The official reason for the strategic reset was attributed to delays in hardware and software development. On May 25, 2010, the Technology@Intel blog announced that Larrabee would not be released as a GPU, but instead would be released as a product for high-performance computing competing with the Nvidia Tesla

Nvidia Tesla was the name of Nvidia's line of products targeted at stream processing or general-purpose graphics processing units (GPGPU), named after pioneering electrical engineer Nikola Tesla. Its products began using GPUs from the G80 ser ...

.

The project to produce a GPU retail product directly from the Larrabee research project was terminated in May 2010. The Intel MIC

Xeon Phi was a series of x86 manycore processors designed and made by Intel. It was intended for use in supercomputers, servers, and high-end workstations. Its architecture allowed use of standard programming languages and application programm ...

multiprocessor architecture announced in 2010 inherited many design elements from the Larrabee project, but does not function as a graphics processing unit; the product is intended as a co-processor for high performance computing. The prototype card was named Knights Ferry, a production card built at a 22 nm process named Knights Corner was planned for production in 2012 or later.

Comparison with competing products

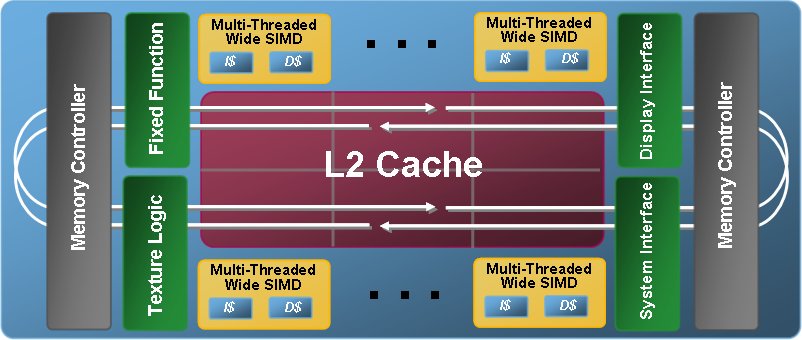

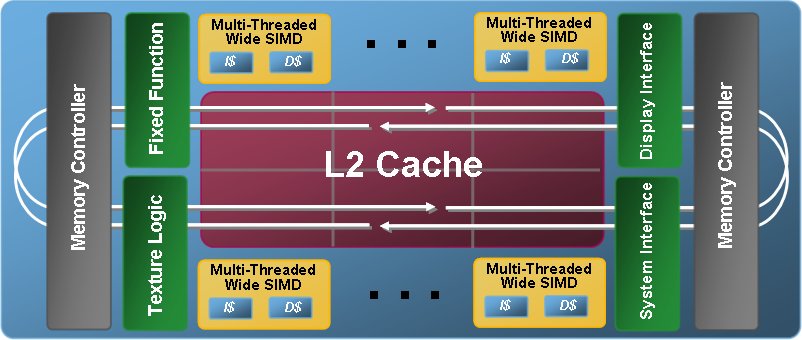

Larrabee can be considered a hybrid between a

Larrabee can be considered a hybrid between a multi-core

A multi-core processor is a microprocessor on a single integrated circuit with two or more separate processing units, called cores, each of which reads and executes program instructions. The instructions are ordinary CPU instructions (such a ...

CPU and a GPU

A graphics processing unit (GPU) is a specialized electronic circuit designed to manipulate and alter memory to accelerate the creation of images in a frame buffer intended for output to a display device. GPUs are used in embedded systems, mobi ...

, and has similarities to both. Its coherent cache

In computer architecture, cache coherence is the uniformity of shared resource data that ends up stored in multiple local caches. When clients in a system maintain caches of a common memory resource, problems may arise with incoherent data, whi ...

hierarchy

A hierarchy (from Greek: , from , 'president of sacred rites') is an arrangement of items (objects, names, values, categories, etc.) that are represented as being "above", "below", or "at the same level as" one another. Hierarchy is an important ...

and x86 architecture

x86 (also known as 80x86 or the 8086 family) is a family of complex instruction set computer (CISC) instruction set architectures initially developed by Intel based on the Intel 8086 microprocessor and its 8088 variant. The 8086 was introd ...

compatibility are CPU-like, while its wide SIMD

Single instruction, multiple data (SIMD) is a type of parallel processing in Flynn's taxonomy. SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it should ...

vector units and texture sampling hardware are GPU-like.

As a GPU, Larrabee would have supported traditional rasterized 3D graphics

3D computer graphics, or “3D graphics,” sometimes called CGI, 3D-CGI or three-dimensional computer graphics are graphics that use a three-dimensional representation of geometric data (often Cartesian) that is stored in the computer for the ...

(Direct3D

Direct3D is a graphics application programming interface (API) for Microsoft Windows. Part of DirectX, Direct3D is used to render three-dimensional graphics in applications where performance is important, such as games. Direct3D uses hardware a ...

& OpenGL

OpenGL (Open Graphics Library) is a cross-language, cross-platform application programming interface (API) for rendering 2D and 3D vector graphics. The API is typically used to interact with a graphics processing unit (GPU), to achieve hardwa ...

) for games. However, its hybridization of CPU and GPU features should also have been suitable for general purpose GPU (GPGPU) or stream processing

In computer science, stream processing (also known as event stream processing, data stream processing, or distributed stream processing) is a programming paradigm which views data streams, or sequences of events in time, as the central input and ou ...

tasks. For example, it might have performed ray tracing or physics processing, in real time for games or offline for scientific research as a component of a supercomputer

A supercomputer is a computer with a high level of performance as compared to a general-purpose computer. The performance of a supercomputer is commonly measured in floating-point operations per second ( FLOPS) instead of million instructions ...

.

Larrabee's early presentation drew some criticism from GPU competitors. At NVISION 08, an Nvidia

Nvidia CorporationOfficially written as NVIDIA and stylized in its logo as VIDIA with the lowercase "n" the same height as the uppercase "VIDIA"; formerly stylized as VIDIA with a large italicized lowercase "n" on products from the mid 1990s to ...

employee called Intel's SIGGRAPH

SIGGRAPH (Special Interest Group on Computer Graphics and Interactive Techniques) is an annual conference on computer graphics (CG) organized by the ACM SIGGRAPH, starting in 1974. The main conference is held in North America; SIGGRAPH Asia ...

paper about Larrabee "marketing puff" and quoted an industry analyst ( Peter Glaskowsky) who speculated that the Larrabee architecture was "like a GPU

A graphics processing unit (GPU) is a specialized electronic circuit designed to manipulate and alter memory to accelerate the creation of images in a frame buffer intended for output to a display device. GPUs are used in embedded systems, mobi ...

from 2006". By June 2009, Intel claimed that prototypes of Larrabee were on par with the Nvidia GeForce GTX 285. Justin Rattner

Justin R. Rattner is a retired Intel Senior Fellow, Corporate Vice President and former director of Intel Labs. Previously, he served as the corporation's Chief Technology Officer, where he was responsible for leading Intel's microprocessor, com ...

, Intel CTO, delivered a keynote at the Supercomputing 2009 conference on November 17, 2009. During his talk he demonstrated an overclocked Larrabee processor topping one teraFLOPS in performance. He claimed this was the first public demonstration of a single-chip system exceeding one teraFLOPS. He pointed out this was early silicon, thereby leaving open the question on eventual performance for the architecture. Because this was only one fifth that of available competing graphics boards, Larrabee was cancelled "as a standalone discrete graphics product" on December 4, 2009.

Differences with contemporary GPUs

Larrabee was intended to differ from older discrete GPUs such as theGeForce 200 Series

The GeForce 200 series is a series of Tesla-based GeForce graphics processing units developed by Nvidia.

Architecture

The GeForce 200 Series introduced Nvidia's second generation of Tesla (microarchitecture), Nvidia's unified shader architec ...

and the Radeon 4000 series in three major ways:

* It was to use the x86

x86 (also known as 80x86 or the 8086 family) is a family of complex instruction set computer (CISC) instruction set architectures initially developed by Intel based on the Intel 8086 microprocessor and its 8088 variant. The 8086 was introd ...

instruction set with Larrabee-specific extensions.

* It was to feature cache coherency

In computer architecture, cache coherence is the uniformity of shared resource data that ends up stored in multiple local caches. When clients in a system maintain caches of a common memory resource, problems may arise with incoherent data, whi ...

across all its cores.

* It was to include very little specialized graphics hardware, instead performing tasks like z-buffering, clipping, and blending in software, using a tile-based rendering approach.

This had been expected to make Larrabee more flexible than current GPUs, allowing more differentiation in appearance between games or other 3D applications. Intel's SIGGRAPH 2008 paper mentioned several rendering features that were difficult to achieve on current GPUs: render target read, order-independent transparency Order-independent transparency (OIT) is a class of techniques in rasterisational computer graphics for rendering transparency in a 3D scene, which do not require rendering geometry in sorted order for alpha compositing.

Description

Commonly, 3D g ...

, irregular shadow mapping, and real-time raytracing.

More recent GPUs such as ATI's Radeon HD 5xxx and Nvidia's GeForce 400 Series

Serving as the introduction of Fermi, the GeForce 400 series is a series of graphics processing units developed by Nvidia. Its release was originally slated in November 2009; however, after delays, it was released on March 26, 2010 with availa ...

feature increasingly broad general-purpose computing capabilities via DirectX11 DirectCompute and OpenCL, as well as Nvidia's proprietary CUDA

CUDA (or Compute Unified Device Architecture) is a parallel computing platform and application programming interface (API) that allows software to use certain types of graphics processing units (GPUs) for general purpose processing, an approach ca ...

technology, giving them many of the capabilities of Larrabee.

Differences with CPUs

The x86 processor cores in Larrabee differed in several ways from the cores in current Intel CPUs such as theCore 2 Duo

Intel Core is a line of streamlined midrange consumer, workstation and enthusiast computer central processing units (CPUs) marketed by Intel, Intel Corporation. These processors displaced the existing mid- to high-end Pentium processors at the ...

or Core i7

The following is a list of Intel Core i7 brand microprocessors. Introduced in 2008, the Core i7 line of microprocessors are intended to be used by high-end users.

Desktop processors

Nehalem microarchitecture (1st generation)

"Bloomfield" ...

:

* Its x86 cores were based on the much simpler P54C

The Pentium (also referred to as P5, its microarchitecture, or i586) is a fifth generation, 32-bit x86 microprocessor that was introduced by Intel on March 22, 1993, as the very first CPU in the Pentium brand. It was instruction set compatible ...

Pentium

Pentium is a brand used for a series of x86 architecture-compatible microprocessors produced by Intel. The original Pentium processor from which the brand took its name was first released on March 22, 1993. After that, the Pentium II and Pe ...

design which is still being maintained for use in embedded applications. The P54C-derived core is superscalar

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a sup ...

but does not include out-of-order execution

In computer engineering, out-of-order execution (or more formally dynamic execution) is a paradigm used in most high-performance central processing units to make use of instruction cycles that would otherwise be wasted. In this paradigm, a proce ...

, though it has been updated with modern features such as x86-64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit version of the x86 instruction set, first released in 1999. It introduced two new modes of operation, 64-bit mode and compatibility mode, along with a new 4-level paging mod ...

support, similar to the Bonnell microarchitecture used in Atom

Every atom is composed of a nucleus and one or more electrons bound to the nucleus. The nucleus is made of one or more protons and a number of neutrons. Only the most common variety of hydrogen has no neutrons.

Every solid, liquid, gas, and ...

. In-order execution means lower performance for individual cores, but since they are smaller, more can fit on a single chip, increasing overall throughput. Execution is also more deterministic so instruction and task scheduling can be done by the compiler.

* Each core contained a 512-bit vector processing

In computing, a vector processor or array processor is a central processing unit (CPU) that implements an instruction set where its instructions are designed to operate efficiently and effectively on large one-dimensional arrays of data called ' ...

unit, able to process 16 single precision floating point numbers at a time. This is similar to, but four times larger than, the SSE units on most x86 processors, with additional features like scatter/gather instructions and a mask register designed to make using the vector unit easier and more efficient. Larrabee was to derive most of its number-crunching power from these vector units.

* It included one major fixed-function

Fixed-function is a term canonically used to contrast 3D graphics APIs and earlier GPUs designed prior to the advent of shader-based 3D graphics APIs and GPU architectures.

History

Historically fixed-function APIs consisted of a set of function ...

graphics hardware feature: texture sampling unit

This is a glossary of terms relating to computer graphics.

For more general computer hardware terms, see glossary of computer hardware terms

This glossary of computer hardware terms is a list of definitions of terms and concepts related to com ...

s. These perform trilinear and anisotropic filtering

In 3D computer graphics, anisotropic filtering (abbreviated AF) is a method of enhancing the image quality of textures on surfaces of computer graphics that are at oblique viewing angles with respect to the camera where the projection of the t ...

and texture decompression.

* It had a 1024-bit (512-bit each way) ring bus for communication between cores and to memory. This bus can be configured in two modes to support Larrabee products with 16 cores or more, or fewer than 16 cores.

* It included explicit cache control instructions to reduce cache thrashing

In computer science, thrashing occurs when a computer's virtual memory resources are overused, leading to a constant state of paging and page faults, inhibiting most application-level processing. This causes the performance of the computer to d ...

during streaming operations which only read/write data once. Explicit prefetching into L2 or L1 cache is also supported.

* Each core supported four-way interleaved multithreading, with four copies of each processor register

A processor register is a quickly accessible location available to a computer's processor. Registers usually consist of a small amount of fast storage, although some registers have specific hardware functions, and may be read-only or write-only. ...

.

Theoretically Larrabee's x86 processor cores would have been able to run existing PC software, or even operating systems. A different version of the processor might sit in motherboard CPU sockets using QuickPath

The Intel QuickPath Interconnect (QPI) is a point-to-point processor interconnect developed by Intel which replaced the front-side bus (FSB) in Xeon, Itanium, and certain desktop platforms starting in 2008. It increased the scalability and availa ...

, but Intel never announced any plans for this. Though Larrabee's native C/C++ compiler included auto-vectorization and many applications were able to execute correctly after having been recompiled, maximum efficiency was expected to have required code optimization using C++ vector intrinsics or inline Larrabee assembly code. However, as in all GPGPUs, not all software would have benefited from utilization of a vector processing unit. One tech journalism site claims that Larrabee's graphics capabilities were planned to be integrated in CPUs based on the Haswell microarchitecture.

Comparison with the Cell broadband engine

Larrabee's philosophy of using many small, simple cores was similar to the ideas behind theCell processor

Cell is a Multi-core processor, multi-core microprocessor microarchitecture that combines a general-purpose PowerPC Central processing unit, core of modest performance with streamlined coprocessor, coprocessing elements which greatly accelerate m ...

. There are some further commonalities, such as the use of a high-bandwidth ring bus to communicate between cores. However, there were many significant differences in implementation which were expected to make programming Larrabee simpler.

* The Cell processor includes one main processor which controls many smaller processors. Additionally, the main processor can run an operating system. In contrast, all of Larrabee's cores are the same, and the Larrabee was not expected to run an OS.

* Each computer core in the Cell (SPE

SPE may refer to:

Science and technology

* Spe (planet), 14 Andromedae b

* Serum protein electrophoresis

* Solar particle event,generating very high energy protons

* Solid phase extraction, from a mixture

* Epitaxy#Solid-phase, Solid-phase epitax ...

) has a local store, for which explicit ( DMA) operations are used for all accesses to DRAM. Ordinary reads and writes to DRAM are not allowed. In Larrabee, all on-chip and off-chip memories are under automatically managed coherent cache hierarchy

Cache hierarchy, or multi-level caches, refers to a memory architecture that uses a hierarchy of memory stores based on varying access speeds to cache data. Highly requested data is cached in high-speed access memory stores, allowing swifter access ...

, so that its cores virtually shared a uniform memory space through standard copy ( MOV) instructions. Larrabee cores each had 256 KB of local L2 cache, and an access which hits another L2 segment takes longer to access.

* Because of the cache coherency noted above, each program running in Larrabee had virtually a large linear memory just as in traditional general-purpose CPU; whereas an application for Cell should be programmed taking into consideration limited memory footprint of the local store associated with each SPE (for details see this article) but with theoretically higher bandwidth. However, since local L2 is faster to access, an advantage can still be gained from using Cell-style programming methods.

* Cell uses DMA for data transfer to and from on-chip local memories, which enables explicit maintenance of overlays stored in local memory to bring memory closer to the core and reduce access latencies, but requiring additional effort to maintain coherency with main memory; whereas Larrabee used a coherent cache with special instructions for cache manipulation (notably cache eviction hints and pre-fetch instructions), which mitigated miss and eviction penalties and reduce cache pollution (e.g. for rendering pipelines and other stream-like computation) at the cost of additional traffic and overhead to maintain cache coherency.

* Each compute core in the Cell runs only one thread at a time, in-order. A core in Larrabee ran up to four threads, but only one at a time. Larrabee's hyperthreading helped hide the latencies inherent to in-order execution.

Comparison with Intel GMA

Intel began integrating a line of GPUs onto motherboards under theIntel GMA

The Intel Graphics Media Accelerator (GMA) is a series of integrated graphics processors introduced in 2004 by Intel, replacing the earlier Intel Extreme Graphics series and being succeeded by the Intel HD and Iris Graphics series.

This series t ...

brand in 2004. Being integrated onto motherboards (newer versions, such as those released with Sandy Bridge, are incorporated onto the same die as the CPU) these chips were not sold separately. Though the low cost and power consumption

Electric energy consumption is the form of energy consumption that uses electrical energy. Electric energy consumption is the actual energy demand made on existing electricity supply for transportation, residential, industrial, commercial, and o ...

of Intel GMA chips made them suitable for small laptops and less demanding tasks, they lack the 3D graphics processing power to compete with contemporary Nvidia and AMD/ATI GPUs for a share of the high-end gaming computer market, the HPC market, or a place in popular video game console

A video game console is an electronic device that Input/output, outputs a video signal or image to display a video game that can be played with a game controller. These may be home video game console, home consoles, which are generally placed i ...

s. In contrast, Larrabee was to be sold as a discrete GPU, separate from motherboards, and was expected to perform well enough for consideration in the next generation of video game consoles.

The team working on Larrabee was separate from the Intel GMA team. The hardware was designed by a newly formed team at Intel's Hillsboro, Oregon

Hillsboro ( ) is the fifth-largest city in the U.S. state of Oregon and is the county seat of Washington County. Situated in the Tualatin Valley on the west side of the Portland metropolitan area, the city hosts many high-technology companies, ...

, site, separate from those that designed the Nehalem. The software and drivers were written by a newly formed team. The 3D stack specifically was written by developers at RAD Game Tools (including Michael Abrash

Michael Abrash is a programmer and technical writer specializing in code optimization and 80x86 assembly language. He wrote the 1990 book ''Zen of Assembly Language Volume 1: Knowledge'' and a monthly column in '' Dr. Dobb's Journal'' in the ea ...

).

The Intel Visual Computing Institute will research basic and applied technologies that could be applied to Larrabee-based products.

Projected performance data

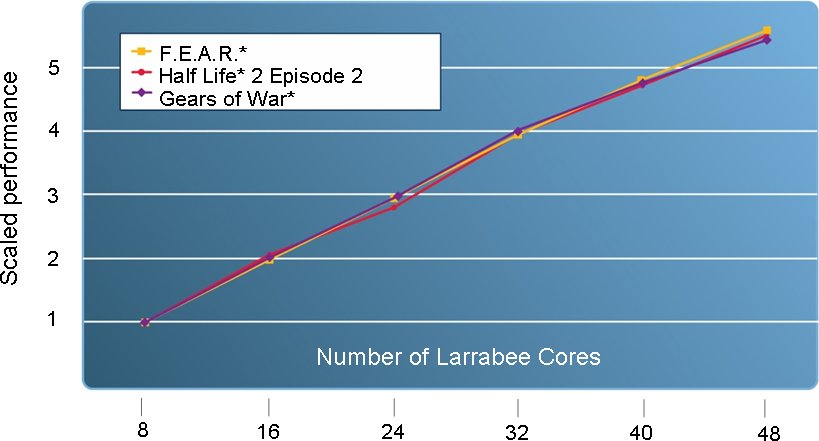

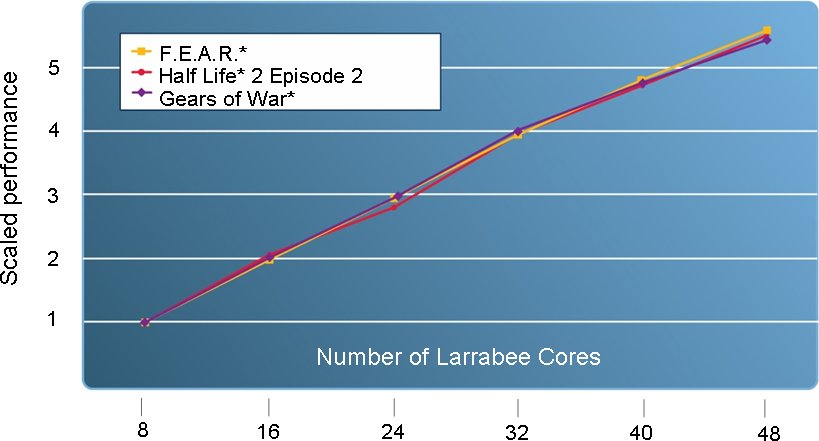

Intel's

Intel's SIGGRAPH

SIGGRAPH (Special Interest Group on Computer Graphics and Interactive Techniques) is an annual conference on computer graphics (CG) organized by the ACM SIGGRAPH, starting in 1974. The main conference is held in North America; SIGGRAPH Asia ...

2008 paper describes cycle-accurate simulations (limitations of memory, caches and texture units was included) of Larrabee's projected performance. Graphs show how many 1 GHz Larrabee cores are required to maintain 60 frame/s at 1600×1200 resolution in several popular games. Roughly 25 cores are required for ''Gears of War

''Gears of War'' is a media franchise centered on a series of video games created by Epic Games, developed and managed by The Coalition, and owned and published by Xbox Game Studios. The franchise is best known for its third-person shooter vide ...

'' with no antialiasing, 25 cores for F.E.A.R

''F.E.A.R.'' is a first-person shooter Horror game#Psychological horror, psychological horror video game series created by Craig Hubbard in 2005. Released on Microsoft Windows, PlayStation 3, and Xbox 360, there are three main games in the seri ...

with 4× antialiasing, and 10 cores for '' Half-Life 2: Episode Two'' with 4× antialiasing. Intel claimed that Larrabee would likely run faster than 1 GHz, so these numbers do not represent actual cores, rather virtual timeslices of such. Another graph shows that performance on these games scales nearly linearly with the number of cores up to 32 cores. At 48 cores the performance drops to 90% of what would be expected if the linear relationship continued.

A June 2007 ''PC Watch'' article suggested that the first Larrabee chips would feature 32 x86 processor cores and come out in late 2009, fabricated on a 45 nanometer process. Chips with a few defective cores due to yield issues would be sold as a 24-core version. Later in 2010, Larrabee would be shrunk for a 32 nanometer fabrication process to enable a 48-core version.

The last statement of performance can be calculated (theoretically this is maximum possible performance) as follows: 32 cores × 16 single-precision float SIMD/core × 2 FLOP (fused multiply-add) × 2 GHz = 2 TFLOPS theoretically.

Public demonstrations

A public demonstration of the Larrabee ray-tracing capabilities took place at theIntel Developer Forum

The Intel Developer Forum (IDF) was a biannual gathering of technologists to discuss Intel products and products based on Intel products. The first IDF was held in 1997.

To emphasize the importance of China, the Spring 2007 IDF was held in Beiji ...

in San Francisco on September 22, 2009. An experimental version of Enemy Territory: Quake Wars titled Quake Wars: Ray Traced was shown in real-time. The scene contained a ray traced water surface that reflected the surrounding objects, like a ship and several flying vehicles, accurately.

A second demo was given at the SC09 conference in Portland at November 17, 2009 during a keynote by Intel CTO Justin Rattner

Justin R. Rattner is a retired Intel Senior Fellow, Corporate Vice President and former director of Intel Labs. Previously, he served as the corporation's Chief Technology Officer, where he was responsible for leading Intel's microprocessor, com ...

. A Larrabee card was able to achieve 1006 GFLops in the SGEMM 4Kx4K calculation.

An engineering sample of a Larrabee card was procured and reviewed by Linus Sebastian

Linus Gabriel Sebastian (born August 20, 1986) is a Canadian YouTuber. Sebastian is best known for creating and hosting YouTube channels that cover technology, especially ''Linus Tech Tips'' (LTT)''.'' His channels have a combined subscriber ...

in a video published May 14, 2018. He was unable to make the card give video output however, with the motherboard displaying POST code D6.

See also

*Xeon Phi

Xeon Phi was a series of x86 manycore processors designed and made by Intel. It was intended for use in supercomputers, servers, and high-end workstations. Its architecture allowed use of standard programming languages and application program ...

* Intel740

The Intel740, or i740 (codenamed ''Auburn''), is a 350 nm graphics processing unit using an AGP interface released by Intel on February 12, 1998. Intel was hoping to use the i740 to popularize the Accelerated Graphics Port, while most grap ...

* Intel GMA

The Intel Graphics Media Accelerator (GMA) is a series of integrated graphics processors introduced in 2004 by Intel, replacing the earlier Intel Extreme Graphics series and being succeeded by the Intel HD and Iris Graphics series.

This series t ...

* x86

x86 (also known as 80x86 or the 8086 family) is a family of complex instruction set computer (CISC) instruction set architectures initially developed by Intel based on the Intel 8086 microprocessor and its 8088 variant. The 8086 was introd ...

* x86-64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit version of the x86 instruction set, first released in 1999. It introduced two new modes of operation, 64-bit mode and compatibility mode, along with a new 4-level paging mod ...

* P5 (microarchitecture)

The Pentium (also referred to as P5, its microarchitecture, or i586) is a fifth generation, 32-bit x86 microprocessor that was introduced by Intel on March 22, 1993, as the very first CPU in the Pentium brand. It was instruction set compatible ...

* Bonnell (microarchitecture)

Bonnell is a CPU microarchitecture used by Intel Atom processors which can execute up to two instructions per cycle. Like many other x86 microprocessors, it translates x86 instructions ( CISC instructions) into simpler internal operations (somet ...

* List of Intel CPU microarchitectures

The following is a ''partial'' list of Intel CPU microarchitectures. The list is ''incomplete''. Additional details can be found in Intel's Tick–tock model and Process–architecture–optimization model.

x86 microarchitectures

16-bit

; ...

* Intel MIC

Xeon Phi was a series of x86 manycore processors designed and made by Intel. It was intended for use in supercomputers, servers, and high-end workstations. Its architecture allowed use of standard programming languages and application programm ...

* Nvidia Tesla

Nvidia Tesla was the name of Nvidia's line of products targeted at stream processing or general-purpose graphics processing units (GPGPU), named after pioneering electrical engineer Nikola Tesla. Its products began using GPUs from the G80 ser ...

* AMD Fusion

AMD Accelerated Processing Unit (APU), formerly known as Fusion, is a series of 64-bit microprocessors from Advanced Micro Devices (AMD), combining a general-purpose AMD64 central processing unit (CPU) and integrated graphics processing unit ...

* AVX-512 AVX-512 are 512-bit extensions to the 256-bit Advanced Vector Extensions SIMD instructions for x86 instruction set architecture (ISA) proposed by Intel in July 2013, and implemented in Intel's Xeon Phi x200 (Knights Landing) and Skylake-X CPUs; thi ...

References

External links

Video of a raytracer running on one of the first Larrabee cards at IDF '09

{{Intel processors, * Intel graphics Intel x86 microprocessors Intel microarchitectures Graphics cards X86 microarchitectures