|

Socket SP6

Socket SP6 (LGA 4844) is a zero insertion force land grid array CPU socket designed by AMD supporting its Zen 4c-based ''Siena'' Epyc server processors that launched on September 18, 2023. It is designed for server systems targeting infrastructure and edge computing segments. History In November 2022, AMD launched the SP5 socket alongside its Epyc 9004 series of processors, codenamed Genoa. The large physical socket and thermal footprint excluded SP5 from certain edge applications. Socket SP6 was created as a smaller variant of socket SP5 with fewer pins and less memory support, reducing the footprint from 72×75.4 mm to 58.5×75.4 mm, identical to that of SP3. The SP6 platform comes in at a lower cost than the SP5 platform's Genoa and Bergamo server processors. Socket SP6 serves segments of the server market where performance is not a priority, but cost, value, small footprint, and low power consumption / heat dissipation are. Examples of this are infrastructure c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Land Grid Array

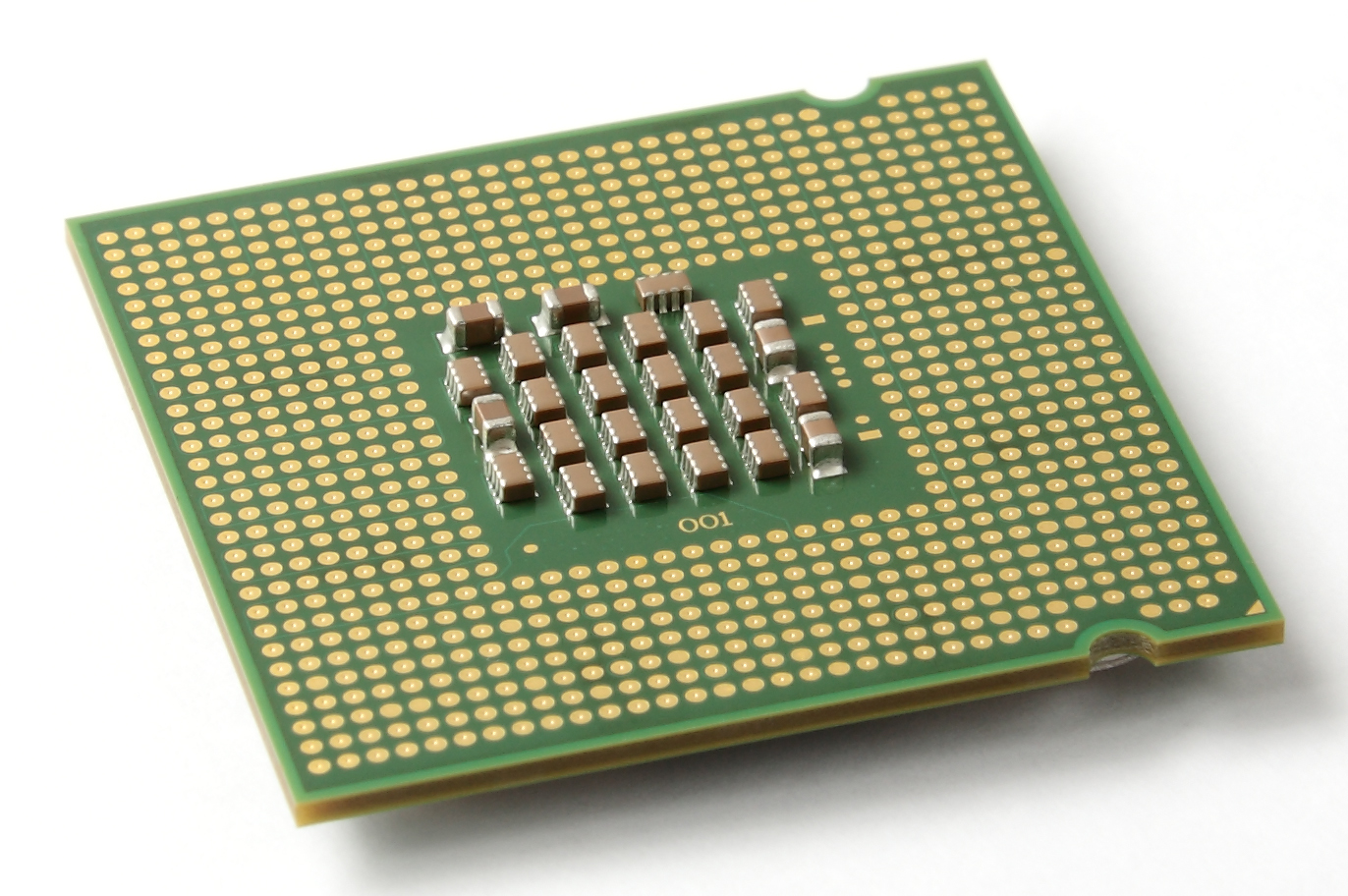

The land grid array (LGA) is a type of surface-mount packaging for integrated circuits (ICs) that is notable for having the pins on the socket (when a socket is used) — as opposed to pins on the integrated circuit, known as a '' pin grid array'' (PGA). An LGA can be electrically connected to a printed circuit board (PCB) either by the use of a socket or by soldering directly to the board. Description The ''land grid array'' is a packaging technology with a grid of contacts, 'lands', on the underside of a package. The contacts are to be connected to a grid of contacts on the PCB. Not all rows and columns of the grid need to be used. The contacts can either be connected by using an LGA socket, or by surface-mount soldering using solder paste. The grid elements found in use can be e.g. circular, triangular or other polygonal shapes and might have even different sizes. Grids might sometimes appear like honey comb patterns. Designs are often optimized for factors like contact likelin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CPU Socket

In computer hardware, a CPU socket or CPU slot contains one or more mechanical components providing mechanical and electrical connections between a microprocessor and a printed circuit board (PCB). This allows for placing and replacing the central processing unit (CPU) without soldering. Common sockets have retention clips that apply a constant force, which must be overcome when a device is inserted. For chips with many pins, zero insertion force (ZIF) sockets are preferred. Common sockets include pin grid array (PGA) or land grid array (LGA). These designs apply a compression force once either a handle (PGA type) or a surface plate (LGA type) is put into place. This provides superior mechanical retention while avoiding the risk of bending pins when inserting the chip into the socket. Certain devices use Ball Grid Array (BGA) sockets, although these require soldering and are generally not considered user replaceable. CPU sockets are used on the motherboard in desktop and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Compute Express Link

Compute Express Link (CXL) is an open standard interconnect for high-speed, high capacity CPU-to-device and CPU-to-memory connections, designed for high performance data center computers. CXL is built on the serial PCI Express (PCIe) physical and electrical interface and includes PCIe-based block input/output protocol (CXL.io) and new cache-coherent protocols for accessing system memory (CXL.cache) and device memory (CXL.mem). The serial communication and pooling capabilities allows CXL memory to overcome performance and socket packaging limitations of common DIMM memory when implementing high storage capacities. History The CXL technology was primarily developed by Intel. The CXL Consortium was formed in March 2019 by founding members Alibaba Group, Cisco Systems, Dell EMC, Meta, Google, Hewlett Packard Enterprise (HPE), Huawei, Intel Corporation and Microsoft, and officially incorporated in September 2019. As of January 2022, AMD, Nvidia, Samsung Electronics and Xilin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PCI Express 5

PCI may refer to: Business and economics * Payment card industry, businesses associated with debit, credit, and other payment cards ** Payment Card Industry Data Security Standard, a set of security requirements for credit card processors * Provincial Competitiveness Index, a governance index of Vietnamese provinces * Ceridian-UCLA Pulse of Commerce Index, a U.S. economic indicator based on trucking fuel consumption * Per capita income * Equitable PCI Bank, a Philippine bank Science and technology * Panel call indicator, telephone signalling system * Pavement condition index, used in transportation civil engineering * Picocurie (pCi), a unit of radioactivity * Peripheral Component Interconnect, a computer bus ** PCI-X (PCI eXtended), a computer bus ** PCI Express (PCIe), a computer bus * Projects of Common Interest, a category of EU projects for interconnecting energy infrastructures * Protocol-control information, in telecommunication * Pulverized coal injection method, in blas ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Random-access Memory

Random-access memory (RAM; ) is a form of Computer memory, electronic computer memory that can be read and changed in any order, typically used to store working Data (computing), data and machine code. A random-access memory device allows data items to be read (computer), read or written in almost the same amount of time irrespective of the physical location of data inside the memory, in contrast with other direct-access data storage media (such as hard disks and Magnetic tape data storage, magnetic tape), where the time required to read and write data items varies significantly depending on their physical locations on the recording medium, due to mechanical limitations such as media rotation speeds and arm movement. In today's technology, random-access memory takes the form of integrated circuit (IC) chips with MOSFET, MOS (metal–oxide–semiconductor) Memory cell (computing), memory cells. RAM is normally associated with Volatile memory, volatile types of memory where s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ECC Memory

Error correction code memory (ECC memory) is a type of computer data storage that uses an error correction code (ECC) to detect and correct ''n''-bit data corruption which occurs in memory. Typically, ECC memory maintains a memory system immune to single-bit errors: the data that is read from each word is always the same as the data that had been written to it, even if one of the bits actually stored has been flipped to the wrong state. Most non-ECC memory cannot detect errors, although some non-ECC memory with parity support allows detection but not correction. ECC memory is used in most computers where data corruption cannot be tolerated, like industrial control applications, critical databases, and infrastructural memory caches. Concept Error correction codes protect against undetected data corruption and are used in computers where such corruption is unacceptable, examples being scientific and financial computing applications, or in database and file servers. ECC can a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR5

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM, DDR5 was planned to reduce power consumption, while doubling bandwidth. The standard, originally targeted for 2018, was released on July 14, 2020. A new feature called Decision Feedback Equalization (DFE) enables input/output (I/O) speed scalability for higher bandwidth and performance improvement. DDR5 has about the same latency as DDR4 and DDR3. DDR5 octuples the maximum DIMM capacity from 64 GB to 512 GB. DDR5 also has higher frequencies than DDR4, up to 9600 MT/s is currently possible, 8200 MT/s translates into around 66 GB/s of bandwidth. Using liquid nitrogen 13000 MT/s speeds were achieved. Rambus announced a working DDR5 dual in-line memory module (DIMM) in September 2017. On November 15, 2018, SK Hynix announced completion of its first DDR5 RAM chip; running at 5.2 GT/s at 1.1 V. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Socket SP5

Socket SP5 (LGA 6096) is a zero insertion force land grid array CPU socket designed by AMD supporting its Zen 4-based Epyc server processors codenamed ''Genoa'' that launched on November 10, 2022. History In June 2017, with the launch of the first generation Epyc server processors, AMD introduced the SP3 socket. The SP3 socket covered three generations of Epyc processors, including Naples, Rome and Milan. AMD's Genoa processors contain up to 96 Zen 4 cores compared to Milan's maximum of 64 cores. In support of Genoa's 96 cores, AMD introduced the SP5 socket with 2022 more contact pins than the SP3 socket to provide greater power delivery and signal integrity. SP5 can provide a peak power of up to 700 W. The SP5 socket supports Epyc processors codenamed Bergamo, which have up to 128 small Zen 4c cores and were launched on June 13, 2023. Features * Supports 12 channels of DDR5 ECC RAM with 6 TB maximum capacity per socket. Using a dual socket system can allow up ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen 4c

Zen 4 is the name for a CPU microarchitecture designed by Advanced Micro Devices, AMD, released on September 27, 2022. It is the successor to Zen 3 and uses TSMC's N6 process for I/O dies, 5 nm process, N5 process for CPU die, CCDs, and N4 process for APUs. Zen 4 powers Ryzen 7000 performance desktop processors (codenamed "Raphael"), Ryzen 8000G series mainstream desktop APUs (codenamed "Phoenix"), and Ryzen Threadripper 7000 series HEDT and workstation processors (codenamed "Storm Peak"). It is also used in extreme mobile processors (codenamed "Dragon Range"), thin & light mobile processors (codenamed "Phoenix" and "Hawk Point"), as well as Epyc, EPYC 8004/9004 server processors (codenamed "Siena", "Genoa" and "Bergamo"). Zen 4 is the first microarchitecture whose chips (Ryzen 7000) use the Socket AM5, AM5 motherboard socket. Features Like its predecessor, Zen 4 in its Desktop Ryzen variants features one or two Core Complex Dies (CCDs) built on TSMC's 5 nm process and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |