|

Sapphire Rapids (microprocessor)

Sapphire Rapids is a codename for Intel's server (fourth generation Xeon Scalable) and workstation (Xeon W-2400/2500 and Xeon W-3400/3500) processors based on the Golden Cove microarchitecture and produced using Intel 7. It features up to 60 cores and an array of accelerators, and it is the first generation of Intel server and workstation processors to use a chiplet design. Sapphire Rapids is part of the Eagle Stream server platform. In addition, it powers Aurora, an exascale supercomputer in the United States, at Argonne National Laboratory. History Sapphire Rapids has been a long-standing Intel project along Alder Lake in development for over five years and has been subjected to many delays. It was first announced by Intel at their Investor Meeting in May 2019 with the intention of Sapphire Rapids succeeding Ice Lake and Cooper Lake in 2021. Intel again announced details on Sapphire Rapids in their August 2021 Architecture Day presentation with no mention of a launch da ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California, and Delaware General Corporation Law, incorporated in Delaware. Intel designs, manufactures, and sells computer components such as central processing units (CPUs) and related products for business and consumer markets. It is one of the world's List of largest semiconductor chip manufacturers, largest semiconductor chip manufacturers by revenue, and ranked in the Fortune 500, ''Fortune'' 500 list of the List of largest companies in the United States by revenue, largest United States corporations by revenue for nearly a decade, from 2007 to 2016 Fiscal year, fiscal years, until it was removed from the ranking in 2018. In 2020, it was reinstated and ranked 45th, being the List of Fortune 500 computer software and information companies, 7th-largest technology company in the ranking. It was one of the first companies listed on Nasdaq. Intel supplies List of I ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CLMUL Instruction Set

Carry-less Multiplication (CLMUL) is an extension to the x86 instruction set used by microprocessors from Intel and AMD which was proposed by Intel in March 2008 and made available in the Intel Westmere processors announced in early 2010. Mathematically, the instruction implements multiplication of polynomials over the finite field GF(2) where the bitstring a_0a_1\ldots a_ represents the polynomial a_0 + a_1X + a_2X^2 + \cdots + a_X^. The CLMUL instruction also allows a more efficient implementation of the closely related multiplication of larger finite fields GF(2''k'') than the traditional instruction set. One use of these instructions is to improve the speed of applications doing block cipher encryption in Galois/Counter Mode, which depends on finite field GF(2''k'') multiplication. Another application is the fast calculation of CRC values, including those used to implement the LZ77 sliding window DEFLATE algorithm in zlib and pngcrush. ARMv8 also has a version of CLMU ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ice Lake (microprocessor)

Ice Lake is Intel's List of Intel codenames, codename for the 10th generation Intel Core mobile and 3rd generation Xeon Scalable server processors based on the Sunny Cove (microarchitecture), Sunny Cove microarchitecture. Ice Lake represents an Architecture step in Intel's process–architecture–optimization model. Produced on the second generation of Intel's 10 nanometer, 10 nm process, 10 nm+, Ice Lake is Intel's second microarchitecture to be manufactured on the 10 nm process, following the limited launch of Cannon Lake (microarchitecture), Cannon Lake in 2018. However, Intel altered their naming scheme in 2020 for the 10 nm process. In this new naming scheme, Ice Lake's manufacturing process is called simply 10 nm, without any appended pluses. Ice Lake CPUs are sold together with the 14 nm Comet Lake CPUs as Intel's "10th Generation Core" product family. There are no Ice Lake desktop or high-power mobile processors; Comet Lake fulfills this ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Xeon

Xeon (; ) is a brand of x86 microprocessors designed, manufactured, and marketed by Intel, targeted at the non-consumer workstation, server, and embedded markets. It was introduced in June 1998. Xeon processors are based on the same architecture as regular desktop-grade CPUs, but have advanced features such as support for error correction code (ECC) memory, higher core counts, more PCI Express lanes, support for larger amounts of RAM, larger cache memory and extra provision for enterprise-grade reliability, availability and serviceability (RAS) features responsible for handling hardware exceptions through the Machine Check Architecture (MCA). They are often capable of safely continuing execution where a normal processor cannot due to these extra RAS features, depending on the type and severity of the machine-check exception (MCE). Some also support multi-socket systems with two, four, or eight sockets through use of the Ultra Path Interconnect (UPI) bus, which replaced ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LGA 4677

LGA 4677 (Socket E) is a zero insertion force flip-chip land grid array (LGA) CPU socket designed by Intel, compatible with Sapphire Rapids server and workstation processors, which was released in January 2023. Features * Support for PCI Express 5.0 and Direct Media Interface 4.0 * Supports 8 channels of DDR5 RAM with error correction code support * Intel Smart Sound Technology that provides dedicated audio voice processing to support voice wake functions is currently available only on the W790 chipset. Chipsets See also * List of Intel microprocessors This generational list of Intel processors attempts to present all of Intel's processors from the 4-bit 4004 (1971) to the present high-end offerings. Concise technical data is given for each product. Latest 15th generation Core Deskto ... * List of Intel chipsets References Intel CPU sockets {{Compu-hardware-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

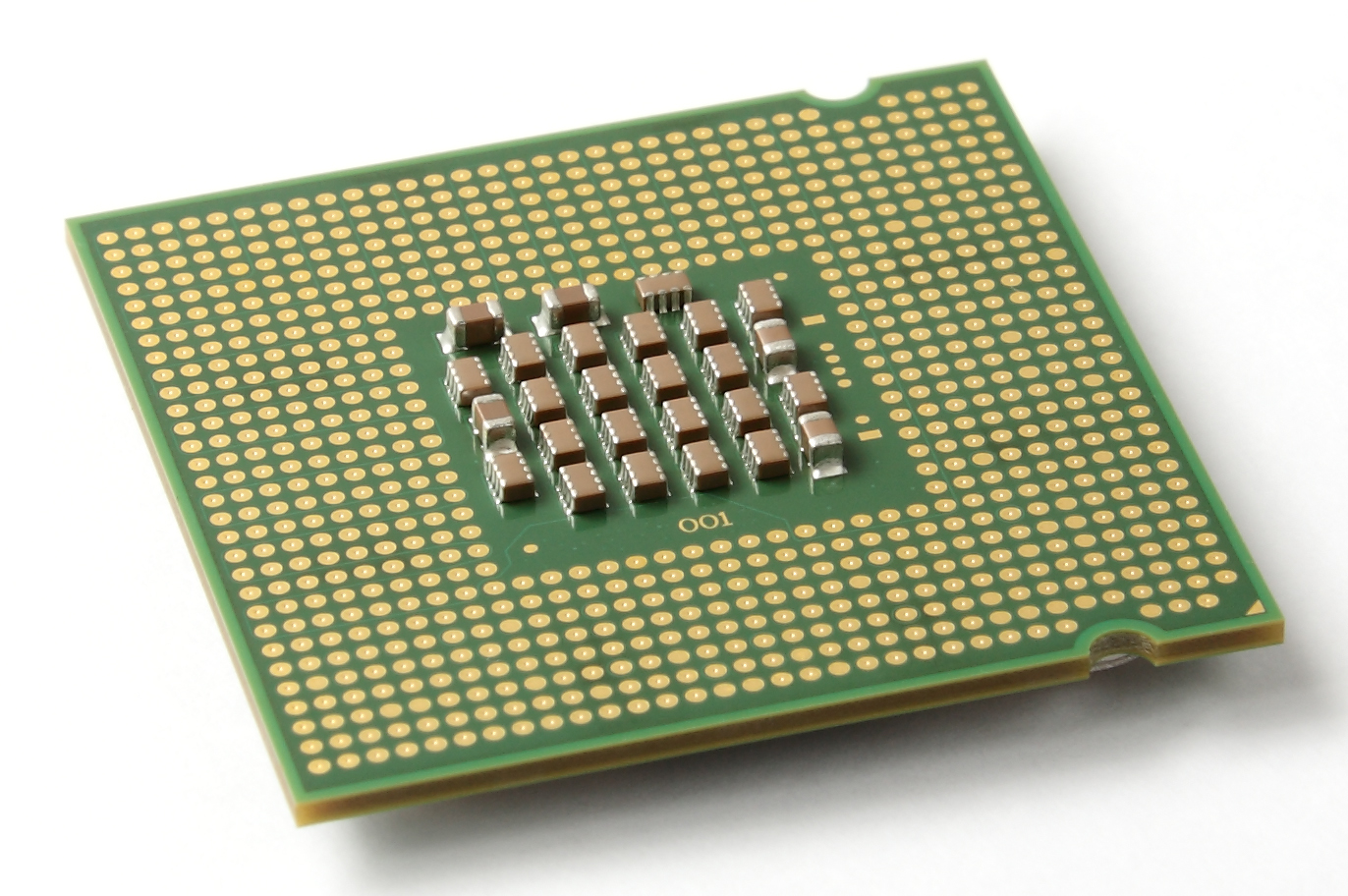

Land Grid Array

The land grid array (LGA) is a type of surface-mount packaging for integrated circuits (ICs) that is notable for having the pins on the socket (when a socket is used) — as opposed to pins on the integrated circuit, known as a '' pin grid array'' (PGA). An LGA can be electrically connected to a printed circuit board (PCB) either by the use of a socket or by soldering directly to the board. Description The ''land grid array'' is a packaging technology with a grid of contacts, 'lands', on the underside of a package. The contacts are to be connected to a grid of contacts on the PCB. Not all rows and columns of the grid need to be used. The contacts can either be connected by using an LGA socket, or by surface-mount soldering using solder paste. The grid elements found in use can be e.g. circular, triangular or other polygonal shapes and might have even different sizes. Grids might sometimes appear like honey comb patterns. Designs are often optimized for factors like contact likelin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Flip Chip

Flip chip, also known as controlled collapse chip connection or its abbreviation, C4, is a method for interconnecting dies such as semiconductor devices, IC chips, integrated passive devices and microelectromechanical systems (MEMS), to external circuitry with solder bumps that have been deposited onto the chip pads. The technique was developed by General Electric's Light Military Electronics Department, Utica, New York. The solder bumps are deposited on the chip pads on the top side of the wafer during the final wafer processing step. In order to mount the chip to external circuitry (e.g., a circuit board or another chip or wafer), it is flipped over so that its top side faces down, and aligned so that its pads align with matching pads on the external circuit, and then the solder is reflowed to complete the interconnect. This is in contrast to wire bonding, in which the chip is mounted upright and fine wires are welded onto the chip pads and lead frame contacts to interconne ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Error Correction Code

In computing, telecommunication, information theory, and coding theory, forward error correction (FEC) or channel coding is a technique used for controlling errors in data transmission over unreliable or noisy communication channels. The central idea is that the sender encodes the message in a redundant way, most often by using an error correction code, or error correcting code (ECC). The redundancy allows the receiver not only to detect errors that may occur anywhere in the message, but often to correct a limited number of errors. Therefore a reverse channel to request re-transmission may not be needed. The cost is a fixed, higher forward channel bandwidth. The American mathematician Richard Hamming pioneered this field in the 1940s and invented the first error-correcting code in 1950: the Hamming (7,4) code. FEC can be applied in situations where re-transmissions are costly or impossible, such as one-way communication links or when transmitting to multiple receivers in m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR5 SDRAM

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM, DDR5 was planned to reduce power consumption, while doubling bandwidth. The standard, originally targeted for 2018, was released on July 14, 2020. A new feature called Decision Feedback Equalization (DFE) enables input/output (I/O) speed scalability for higher bandwidth and performance improvement. DDR5 has about the same latency as DDR4 and DDR3. DDR5 octuples the maximum DIMM capacity from 64 GB to 512 GB. DDR5 also has higher frequencies than DDR4, up to 9600 MT/s is currently possible, 8200 MT/s translates into around 66 GB/s of bandwidth. Using liquid nitrogen 13000 MT/s speeds were achieved. Rambus announced a working DDR5 dual in-line memory module (DIMM) in September 2017. On November 15, 2018, SK Hynix announced completion of its first DDR5 RAM chip; running at 5.2 GT/s at 1.1 V ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

VT-d

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel ( VT-x) and AMD (AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Trusted Execution Technology

Intel Trusted Execution Technology (Intel TXT, formerly known as LaGrande Technology) is a computer hardware technology of which the primary goals are: * Attestation of the authenticity of a platform and its operating system. * Assuring that an authentic operating system starts in a trusted environment, which can then be considered trusted. * Provision of a trusted operating system with additional security capabilities not available to an unproven one. Intel TXT uses a Trusted Platform Module (TPM) and cryptographic techniques to provide measurements of software and platform components so that system software as well as local and remote management applications may use those measurements to make trust decisions. It complements Intel Management Engine. This technology is based on an industry initiative by the Trusted Computing Group (TCG) to promote safer computing. It defends against software-based attacks aimed at stealing sensitive information by corrupting system or BIOS code ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |