|

POWER6

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA#Power ISA v.2.05, Power ISA v.2.05. When it became available in systems in 2007, it succeeded the POWER5#POWER5+, POWER5+ as IBM's flagship Power microprocessor. It is claimed to be part of the eCLipz project, said to have a goal of converging IBM's server hardware where practical (hence "ipz" in the acronym: IBM AS/400, iSeries, pSeries, and zSeries). History POWER6 was described at the International Solid-State Circuits Conference (ISSCC) in February 2006, and additional details were added at the Microprocessor Forum in October 2006 and at the next ISSCC in February 2007. It was formally announced on May 21, 2007. It was released on June 8, 2007 at speeds of 3.5, 4.2 and 4.7 GHz, but the company has noted prototypes have reached 6 GHz. POWER6 reached first silicon in the middle of 2005, and was bumped to 5.0 GHz in May 2008 with the introduction of the P595. Description The POWE ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

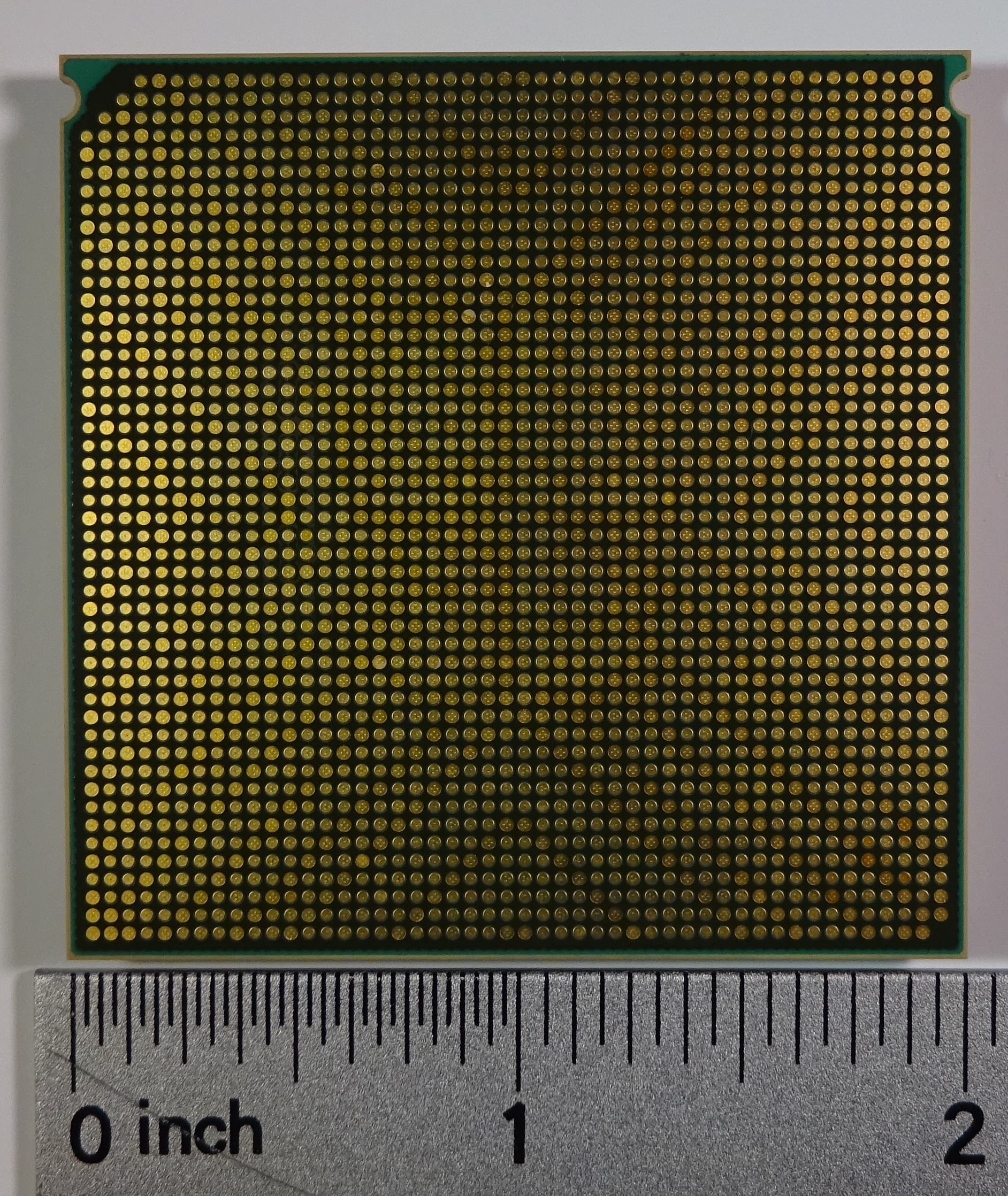

Power6 Ceramic Base

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA v.2.05. When it became available in systems in 2007, it succeeded the POWER5+ as IBM's flagship Power microprocessor. It is claimed to be part of the eCLipz project, said to have a goal of converging IBM's server hardware where practical (hence "ipz" in the acronym: iSeries, pSeries, and zSeries). History POWER6 was described at the International Solid-State Circuits Conference (ISSCC) in February 2006, and additional details were added at the Microprocessor Forum in October 2006 and at the next ISSCC in February 2007. It was formally announced on May 21, 2007. It was released on June 8, 2007 at speeds of 3.5, 4.2 and 4.7 GHz, but the company has noted prototypes have reached 6 GHz. POWER6 reached first silicon in the middle of 2005, and was bumped to 5.0 GHz in May 2008 with the introduction of the P595. Description The POWER6 is a dual-core processor. Each core is capable of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

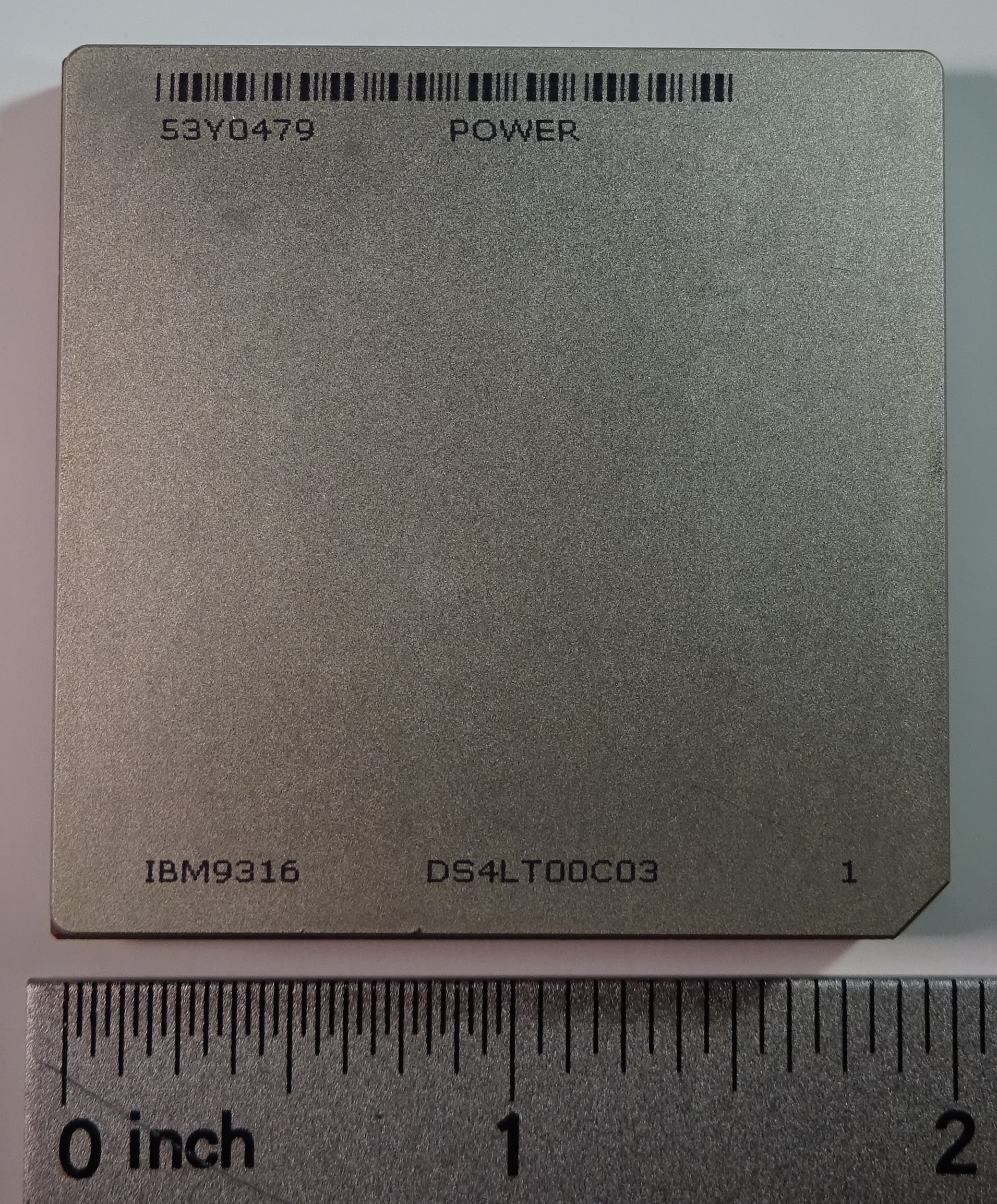

Power6 Bottom

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA#Power ISA v.2.05, Power ISA v.2.05. When it became available in systems in 2007, it succeeded the POWER5#POWER5+, POWER5+ as IBM's flagship Power microprocessor. It is claimed to be part of the eCLipz project, said to have a goal of converging IBM's server hardware where practical (hence "ipz" in the acronym: IBM AS/400, iSeries, pSeries, and zSeries). History POWER6 was described at the International Solid-State Circuits Conference (ISSCC) in February 2006, and additional details were added at the Microprocessor Forum in October 2006 and at the next ISSCC in February 2007. It was formally announced on May 21, 2007. It was released on June 8, 2007 at speeds of 3.5, 4.2 and 4.7 GHz, but the company has noted prototypes have reached 6 GHz. POWER6 reached first silicon in the middle of 2005, and was bumped to 5.0 GHz in May 2008 with the introduction of the P595. Description The POWE ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Power6 Ceramic No Cap

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA v.2.05. When it became available in systems in 2007, it succeeded the POWER5+ as IBM's flagship Power microprocessor. It is claimed to be part of the eCLipz project, said to have a goal of converging IBM's server hardware where practical (hence "ipz" in the acronym: iSeries, pSeries, and zSeries). History POWER6 was described at the International Solid-State Circuits Conference (ISSCC) in February 2006, and additional details were added at the Microprocessor Forum in October 2006 and at the next ISSCC in February 2007. It was formally announced on May 21, 2007. It was released on June 8, 2007 at speeds of 3.5, 4.2 and 4.7 GHz, but the company has noted prototypes have reached 6 GHz. POWER6 reached first silicon in the middle of 2005, and was bumped to 5.0 GHz in May 2008 with the introduction of the P595. Description The POWER6 is a dual-core processor. Each core is capable of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

POWER7

POWER7 is a family of superscalar multi-core microprocessors based on the Power ISA 2.06 instruction set architecture released in 2010 that succeeded the POWER6 and POWER6+. POWER7 was developed by IBM at several sites including IBM's Rochester, MN; Austin, TX; Essex Junction, VT; T. J. Watson Research Center, NY; Bromont, QC and IBM Deutschland Research & Development GmbH, Böblingen, Germany laboratories. IBM announced servers based on POWER7 on 8 February 2010. History IBM won a $244 million DARPA contract in November 2006 to develop a petascale supercomputer architecture before the end of 2010 in the HPCS project. The contract also states that the architecture shall be available commercially. IBM's proposal, PERCS (Productive, Easy-to-use, Reliable Computer System), which won them the contract, is based on the POWER7 processor, AIX operating system and General Parallel File System. One feature that IBM and DARPA collaborated on is modifying the addressing an ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PSeries

The IBM System p is a high-end line of RISC ( Power)/UNIX-based servers. It was the successor of the RS/6000 line, and predecessor of the IBM Power Systems server series. History The previous RS/6000 line was originally a line of workstations and servers. The first System p server line was named the ''e''Server pSeries in 2000 as part of the e-Server branding initiative. In 2004, with the advent of the POWER5 processor, the server family was rebranded the ''e''Server p5. In 2005, following IBM's move to streamline its server and storage brands worldwide, and incorporating the "System" brand with the Systems Agenda, the family was again renamed to System p5. The System p5 now encompassed the IBM OpenPower product line. In 2007, after the introduction of the POWER6 processor models, the last rename under the System p brand dropped the p (numbered) designation. In April 2008, IBM announced a rebranding of the System p and its unification with the mid-range System i platform. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM AS/400

The IBM AS/400 (Application System/400) is a family of midrange computers from IBM announced in June 1988 and released in August 1988. It was the successor to the System/36 and System/38 platforms, and ran the OS/400 operating system. Lower-cost but more powerful than its predecessors, an estimated 111,000 installations existed by the end of 1990 and annual revenue reaching $14 billion that year, increasing to 250,000 systems by 1994, and about 500,000 shipped by 1997. A key concept in the AS/400 platform is IBM i#TIMI, Technology Independent Machine Interface (TIMI), a platform-independent instruction set architecture (ISA) that is translated to native machine language instructions. The platform has used this capability to change the underlying processor architecture without breaking application compatibility. Early systems were based on a 48-bit Complex instruction set computer, CISC instruction set architecture known as the ''Internal Microprogrammed Interface'' (IMPI), original ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Power ISA

Power ISA is a reduced instruction set computer (RISC) instruction set architecture (ISA) currently developed by the OpenPOWER Foundation, led by IBM. It was originally developed by IBM and the now-defunct Power.org industry group. Power ISA is an evolution of the PowerPC ISA, created by the mergers of the core PowerPC ISA and the optional Book E for embedded applications. The merger of these two components in 2006 was led by Power.org founders IBM and Freescale Semiconductor. Prior to version 3.0, the ISA is divided into several categories. Processors implement a set of these categories as required for their task. Different classes of processors are required to implement certain categories, for example a server-class processor includes the categories: ''Base'', ''Server'', ''Floating-Point'', ''64-Bit'', etc. All processors implement the Base category. Power ISA is a RISC load/store architecture. It has multiple sets of registers: * ''32'' × 32-bit or 64-bit general- ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Z10

The z10 is a microprocessor chip made by IBM for their System z10 mainframe computers, released February 26, 2008. It was called "z6" during development. Description The processor implements the CISC z/Architecture and has four cores. Each core has a 64 KB L1 instruction cache, a 128 KB L1 data cache and a 3 MB L2 cache (called the L1.5 cache by IBM). Finally, there is a 24 MB shared L3 cache (referred to as the L2 cache by IBM). The chip measures 21.7×20.0 mm and consists of 993 million transistors fabricated in IBM's 65 nm SOI fabrication process (CMOS 11S), supporting speeds of 4.4 GHz and above – more than twice the clock speed as former mainframes – with a 15 FO4 cycle. Each z10 chip has two 48 GB/s (48 billion bytes per second) SMP hub ports, four 13 GB/s memory ports, two 17 GB/s I/O ports, and 8765 contacts. The z10 processor was co-developed with and shares many design traits with the POWER6 processor, such as fabrication technology, logi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

POWER5

The POWER5 is a microprocessor developed and fabricated by IBM. It is an improved version of the POWER4. The principal improvements are support for simultaneous multithreading (SMT) and an on-die memory controller. The POWER5 is a dual-core microprocessor, with each core supporting one physical Thread (computing), thread and two logical threads, for a total of two physical threads and four logical threads. History Technical details of the microprocessor were first presented at the 2003 Hot Chips (symposium), Hot Chips conference. A more complete description was given at Microprocessor Forum 2003 on 14 October 2003. The POWER5 was not sold openly and was used exclusively by IBM and their partners. Systems using the microprocessor were introduced in 2004. The POWER5 competed in the high-end enterprise server market, mostly against the Intel Itanium 2 and to a lesser extent, the Sun Microsystems UltraSPARC IV and the Fujitsu SPARC64 V. It was superseded in 2005 by an improve ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Out-of-order Execution

In computer engineering, out-of-order execution (or more formally dynamic execution) is an instruction scheduling paradigm used in high-performance central processing units to make use of instruction cycles that would otherwise be wasted. In this paradigm, a processor executes instructions in an order governed by the availability of input data and execution units, rather than by their original order in a program. In doing so, the processor can avoid being idle while waiting for the preceding instruction to complete and can, in the meantime, process the next instructions that are able to run immediately and independently. History Out-of-order execution is a restricted form of dataflow architecture, which was a major research area in computer architecture in the 1970s and early 1980s. Early use in supercomputers The first machine to use out-of-order execution was the CDC 6600 (1964), designed by James E. Thornton, which uses a scoreboard to avoid conflicts. It permits ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Decimal Floating Point

Decimal floating-point (DFP) arithmetic refers to both a representation and operations on Decimal data type, decimal floating-point numbers. Working directly with decimal (base-10) fractions can avoid the rounding errors that otherwise typically occur when converting between decimal fractions (common in human-entered data, such as measurements or financial information) and binary (base-2) fractions. The advantage of decimal floating-point representation over decimal Fixed-point arithmetic, fixed-point and Integer (computer science), integer representation is that it supports a much wider range of values. For example, while a fixed-point representation that allocates 8 decimal digits and 2 decimal places can represent the numbers 123456.78, 8765.43, 123.00, and so on, a floating-point representation with 8 decimal digits could also represent 1.2345678, 1234567.8, 0.000012345678, 12345678000000000, and so on. This wider range can dramatically slow the accumulation of rounding error ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |