|

List Of Intel Pentium Microprocessors

The Intel Pentium brand was a line of mainstream x86-architecture microprocessors from Intel. Processors branded Pentium Processor with MMX Technology (and referred to as Pentium MMX for brevity) are also listed here. It was replaced by the Intel Processor brand in 2023. Desktop processors P5 based Pentiums "P5" (800 nm) * Based on P5 * Steppings: B1, C1, D1 (Note: D1 stepping processors do not have FDIV bug) "P54C" (600 nm) * Based on P5 microarchitecture * Steppings: B1, B3, B5, C2, E0 (Note: D1 stepping processors do not have FDIV bug) "P54CQS" (350 nm) * Based on P5 microarchitecture "P54CS" (350 nm) * Based on P5 microarchitecture "P55C" (350 nm) * Based on P5 microarchitecture P6 based Pentiums Desktop processors based on the P6 microarchitecture were marketed as Pentium Pro, Pentium II and Pentium III, as well as variations of these names. NetBurst based Pentiums Desktop processors based on the NetBurst m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Pentium Processor

Pentium is a series of x86 architecture-compatible microprocessors produced by Intel from 1993 to 2023. The original Pentium was Intel's fifth generation processor, succeeding the i486; Pentium was Intel's flagship processor line for over a decade until the introduction of the Intel Core line in 2006. Pentium-branded processors released from 2009 onwards were considered entry-level products positioned above the low-end Atom and Celeron series, but below the faster Core lineup and workstation/server Xeon series. The later Pentiums, which have little more than their name in common with earlier Pentiums, were based on both the architecture used in Atom and that of Core processors. In the case of Atom architectures, Pentiums were the highest performance implementations of the architecture. Pentium processors with Core architectures prior to 2017 were distinguished from the faster, higher-end i-series processors by lower clock rates and disabling some features, such as hyper-t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Pentium Dual-Core

The Pentium Dual-Core brand was used for mainstream x86-architecture microprocessors from Intel from 2006 to 2009, when it was renamed to Pentium. The processors are based on either the 32-bit '' Yonah'' or (with quite different microarchitectures) 64-bit '' Merom-2M'', '' Allendale'', and '' Wolfdale-3M'' core, targeted at mobile or desktop computers. In terms of features, price, and performance at a given clock frequency, Pentium Dual-Core processors were positioned above Celeron but below Core and Core 2 processors in Intel's product range. The Pentium Dual-Core was also a very popular choice for overclocking, as it can deliver high performance (when overclocked) at a low price. Processor cores In 2006, Intel announced a plan to return the Pentium trademark from retirement to the market, as a moniker of low-cost Core microarchitecture processors based on the single-core Conroe-L but with 1 MB of cache. The identification numbers for those planned Pentiums were similar ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel VT-x

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel (VT-x) and AMD (AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited acc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Wolfdale (microprocessor)

Wolfdale is the code name for a processor from Intel that is sold in varying configurations as Core 2 Duo, Celeron, Pentium and Xeon. In Intel's Tick-Tock cycle, the 2007/2008 "Tick" was Penryn microarchitecture, the shrink of the Merom microarchitecture to 45 nanometers as CPUID model 23. This replaced the Conroe processor with ''Wolfdale''. The Wolfdale chips come in four sizes, with 6 MB and 3 MB L2 cache (Core 2 Duo); the smaller version is commonly called Wolfdale-3M, 2 MB L2 (Pentium), and 1 MB L2 (Celeron). The mobile version of Wolfdale is Penryn and the dual-socket server version is Wolfdale-DP. The Yorkfield desktop processor is a quad-core Multi-chip module of Wolfdale. Wolfdale was replaced by Nehalem based Clarkdale. Variants Wolfdale Wolfdale is the codename for the E8000 series of Core 2 Duo desktop processors and the Xeon 3100 server processor family. Released on January 20, 2008, the chips are manufactured using a 45-nanometer process and featu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

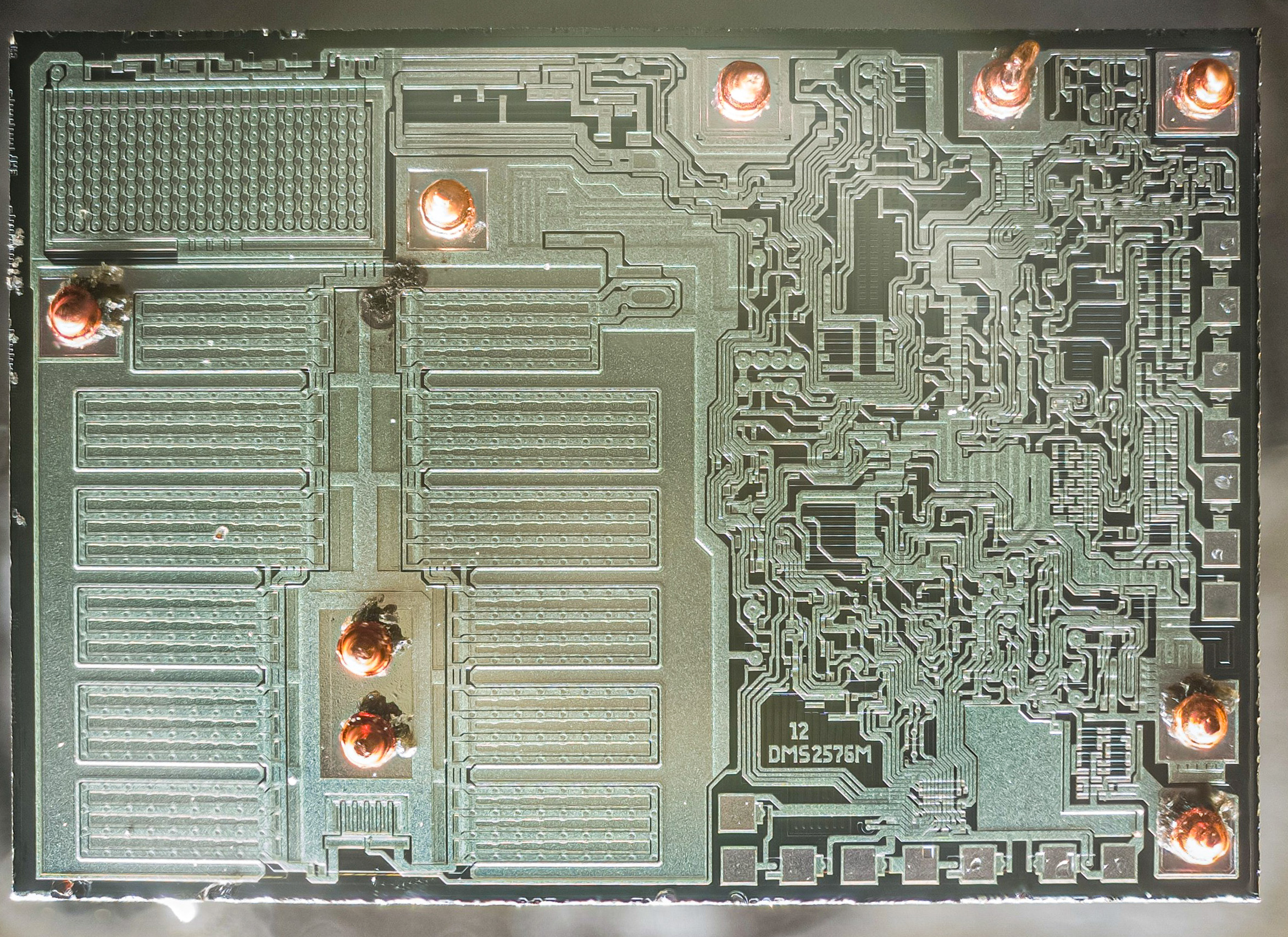

Die (integrated Circuit)

A die, in the context of integrated circuits, is a small block of semiconducting material on which a given functional circuit is Semiconductor fabrication, fabricated. Typically, integrated circuits are produced in large batches on a single wafer (electronics), wafer of electronic-grade Monocrystalline silicon, silicon (EGS) or other semiconductor (such as Gallium arsenide, GaAs) through processes such as photolithography. The wafer is cut (wafer dicing, diced) into many pieces, each containing one copy of the circuit. Each of these pieces is called a die. There are three commonly used plural forms: ''dice'', ''dies,'' and ''die''. To simplify handling and integration onto a printed circuit board, most dies are integrated circuit packaging, packaged in List of electronic component packaging types, various forms. Manufacturing process Most dies are composed of silicon and used for integrated circuits. The process begins with the production of Single crystal, monocrystalline sili ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

NX Bit

The NX bit (no-execute bit) is a processor feature that separates areas of a virtual address space (the memory layout a program uses) into sections for storing data or program instructions. An operating system supporting the NX bit can mark certain areas of the virtual address space as non-executable, preventing the processor from running any code stored there. This technique, known as executable space protection or Write XOR Execute, protects computers from malicious software that attempts to insert harmful code into another program’s data storage area and execute it, such as in a buffer overflow attack. The term "NX bit" was introduced by Advanced Micro Devices (AMD) as a marketing term. Intel markets this feature as the XD bit (execute disable), while the MIPS architecture refers to it as the XI bit (execute inhibit). In the ARM architecture, introduced in ARMv6, it is known as XN (execute never). The term NX bit is often used broadly to describe similar executable space p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel 64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit extension of the x86 instruction set. It was announced in 1999 and first available in the AMD Opteron family in 2003. It introduces two new operating modes: 64-bit mode and compatibility mode, along with a new four-level paging mechanism. In 64-bit mode, x86-64 supports significantly larger amounts of virtual memory and physical memory compared to its 32-bit predecessors, allowing programs to utilize more memory for data storage. The architecture expands the number of general-purpose registers from 8 to 16, all fully general-purpose, and extends their width to 64 bits. Floating-point arithmetic is supported through mandatory SSE2 instructions in 64-bit mode. While the older x87 FPU and MMX registers are still available, they are generally superseded by a set of sixteen 128-bit vector registers (XMM registers). Each of these vector registers can store one or two double-precision floating-point numbers, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SpeedStep

Enhanced SpeedStep is a series of dynamic frequency scaling technologies (codenamed Geyserville and including SpeedStep, SpeedStep II, and SpeedStep III) built into some Intel's microprocessors that allow the clock speed of the processor to be dynamically changed (to different ''P-states'') by software. This allows the processor to meet the instantaneous performance needs of the operation being performed, while minimizing power draw and heat generation. EIST (SpeedStep III) was introduced in several Prescott 6 series in the first quarter of 2005, namely the Pentium 4 660. Intel Speed Shift Technology (SST) was introduced in Intel Skylake Processor. Enhanced Intel SpeedStep Technology is sometimes abbreviated as EIST. Intel's trademark of "Intel SpeedStep" was canceled due to the trademark being invalidated in 2012. Explanation Running a processor at high clock speeds allows for better performance. However, when the same processor is run at a lower frequency (speed), it gene ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSSE3

Supplemental Streaming SIMD Extensions 3 (SSSE3 or SSE3S) is a SIMD instruction set created by Intel and is the fourth iteration of the SSE technology. History SSSE3 was first introduced with Intel processors based on the Core microarchitecture on June 26, 2006 with the "Woodcrest" Xeons. SSSE3 has been referred to by the codenames Tejas New Instructions (TNI) or Merom New Instructions (MNI) for the first processor designs intended to support it. SSSE3 has enhanced for HD audio/video decoding/encoding, for example AAC. Functionality SSSE3 contains 16 new discrete instructions. Each instruction can act on 64-bit MMX or 128-bit XMM registers. Therefore, Intel's materials refer to 32 new instructions. They include: * Twelve instructions that perform horizontal addition or subtraction operations. * Six instructions that evaluate absolute values. * Two instructions that perform multiply-and-add operations and speed up the evaluation of dot products. * Two instructions tha ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSE3

SSE3, Streaming SIMD Extensions 3, also known by its Intel code name Prescott New Instructions (PNI), is the third iteration of the SSE instruction set for the IA-32 (x86) architecture. Intel introduced SSE3 in early 2004 with the Prescott revision of their Pentium 4 CPU. In April 2005, AMD introduced a subset of SSE3 in revision E (Venice and San Diego) of their Athlon 64 CPUs. The earlier SIMD instruction sets on the x86 platform, from oldest to newest, are MMX, 3DNow! (developed by AMD, no longer supported on newer CPUs), SSE, and SSE2. SSE3 contains 13 new instructions over SSE2. Changes The most notable change is the capability to work horizontally in a register, as opposed to the more or less strictly vertical operation of all previous SSE instructions. More specifically, instructions to add and subtract the multiple values stored within a single register have been added. These instructions can be used to speed up the implementation of a number of DSP and 3D op ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSE2

SSE2 (Streaming SIMD Extensions 2) is one of the Intel SIMD (Single Instruction, Multiple Data) processor supplementary instruction sets introduced by Intel with the initial version of the Pentium 4 in 2000. SSE2 instructions allow the use of XMM (SIMD) registers on x86 instruction set architecture processors. These registers can load up to 128 bits of data and perform instructions, such as vector addition and multiplication, simultaneously. SSE2 introduced double-precision floating point instructions in addition to the single-precision floating point and integer instructions found in SSE. SSE2 extends earlier SSE instruction set by adding 144 new instructions to the previous 70 instructions. SSE2 intends to fully replace MMX, a SIMD instruction set found on IA-32 architecture processors. Competing chip-maker AMD added support for SSE2 with the introduction of their Opteron and Athlon 64 ranges of AMD64 64-bit CPUs in 2003. SSE2 was extended to create SSE3 in 2004, and e ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data ( SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in its Pentium III series of central processing units (CPUs) shortly after the appearance of Advanced Micro Devices (AMD's) 3DNow!. SSE contains 70 new instructions (65 unique mnemonics using 70 encodings), most of which work on single precision floating-point data. SIMD instructions can greatly increase performance when exactly the same operations are to be performed on multiple data objects. Typical applications are digital signal processing and graphics processing. Intel's first IA-32 SIMD effort was the MMX instruction set. MMX had two main problems: it re-used existing x87 floating-point registers making the CPUs unable to work on both floating-point and SIMD data at the same time, and it only worked on integers. SSE floating-point instructions operate on a new independent register s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |