|

Hopper (microarchitecture)

Hopper is the codename for Nvidia's GPU Datacenter microarchitecture that will be parallel release of Ada Lovelace (for the consumer segment). It is named after the American computer scientist and United States Navy Rear Admiral Grace Hopper. Hopper was once rumored to be Nvidia's first generation of GPUs that will use multi-chip modules (MCMs), although the H100 announcement showed a massive monolithic die. Nvidia officially announced the Hopper GPU microarchitecture and H100 GPU at GTC 2022 on March 22, 2022. Details Architectural improvements of the Hopper architecture include the following: * CUDA Compute Capability 9.0 * TSMC N4 FinFET process * Fourth-generation Tensor Cores with FP8, FP16, bfloat16, TensorFloat-32 (TF32) and FP64 support and sparsity acceleration. * New Nvidia Transformer Engine with FP8 and FP16 * New DPX instructions * High Bandwidth Memory 3 (HBM3) on H100 80GB * Double FP32 cores per Streaming Multiprocessor (SM) * NVLink 4.0 * PCI Express 5.0 w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

5 Nm Process

In semiconductor manufacturing, the International Roadmap for Devices and Systems defines the 5 nm process as the MOSFET technology node following the 7 nm node. In 2020, Samsung and TSMC entered volume production of 5 nm chips, manufactured for companies including Apple, Marvell, Huawei and Qualcomm. The term "5 nanometer" has no relation to any actual physical feature (such as gate length, metal pitch or gate pitch) of the transistors. According to the projections contained in the 2021 update of the International Roadmap for Devices and Systems published by IEEE Standards Association Industry Connection, a 5 nm node is expected to have a contacted gate pitch of 51 nanometers and a tightest metal pitch of 30 nanometers. However, in real world commercial practice, "5 nm" is used primarily as a marketing term by individual microchip manufacturers to refer to a new, improved generation of silicon semiconductor chips in terms of increased transistor density (i.e. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

HBM3

High Bandwidth Memory (HBM) is a high-speed computer memory interface for 3D-stacked synchronous dynamic random-access memory (SDRAM) initially from Samsung, AMD and SK Hynix. It is used in conjunction with high-performance graphics accelerators, network devices, high-performance datacenter AI ASICs and FPGAs and in some supercomputers (such as the NEC SX-Aurora TSUBASA and Fujitsu A64FX). The first HBM memory chip was produced by SK Hynix in 2013, and the first devices to use HBM were the AMD Fiji GPUs in 2015. High Bandwidth Memory has been adopted by JEDEC as an industry standard in October 2013.High Bandwidth Memory (HBM) DRAM (JESD235) JEDEC, October 2013 The second generation, HBM2, was accepted by JEDEC in January 2016. Technology < ...

|

Nvidia Tesla

Nvidia Tesla was the name of Nvidia's line of products targeted at stream processing or general-purpose graphics processing units (GPGPU), named after pioneering electrical engineer Nikola Tesla. Its products began using GPUs from the G80 series, and have continued to accompany the release of new chips. They are programmable using the CUDA or OpenCL APIs. The Nvidia Tesla product line competed with AMD's Radeon Instinct and Intel Xeon Phi lines of deep learning and GPU cards. Nvidia retired the Tesla brand in May 2020, reportedly because of potential confusion with the brand of cars. Its new GPUs are branded Nvidia Data Center GPUs, as in the Ampere A100 GPU. Overview Offering computational power much greater than traditional microprocessors, the Tesla products targeted the high-performance computing market. , Nvidia Teslas power some of the world's fastest supercomputers, including Summit at Oak Ridge National Laboratory and Tianhe-1A, in Tianjin, China. Tesla cards h ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Library (computing)

In computer science, a library is a collection of non-volatile memory, non-volatile resources used by computer programs, often for software development. These may include configuration data, documentation, help data, message templates, Code reuse, pre-written code and subroutines, Class (computer science), classes, Value (computer science), values or Data type, type specifications. In OS/360 and successors, IBM's OS/360 and its successors they are referred to as Data set (IBM mainframe)#Partitioned datasets, partitioned data sets. A library is also a collection of implementations of behavior, written in terms of a language, that has a well-defined interface (computing), interface by which the behavior is invoked. For instance, people who want to write a higher-level program can use a library to make system calls instead of implementing those system calls over and over again. In addition, the behavior is provided for reuse by multiple independent programs. A program invokes the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

JPEG

JPEG ( ) is a commonly used method of lossy compression for digital images, particularly for those images produced by digital photography. The degree of compression can be adjusted, allowing a selectable tradeoff between storage size and image quality. JPEG typically achieves 10:1 compression with little perceptible loss in image quality. Since its introduction in 1992, JPEG has been the most widely used image compression standard in the world, and the most widely used digital image format, with several billion JPEG images produced every day as of 2015. The term "JPEG" is an acronym for the Joint Photographic Experts Group, which created the standard in 1992. JPEG was largely responsible for the proliferation of digital images and digital photos across the Internet, and later social media. JPEG compression is used in a number of image file formats. JPEG/Exif is the most common image format used by digital cameras and other photographic image capture devices; along with JPEG ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nvidia NVDEC

Nvidia NVDEC (formerly known as NVCUVID) is a feature in its graphics cards that performs video decoding, offloading this compute-intensive task from the CPU. It is accompanied by NVENC for video ''encoding'' in Nvidia's Video Codec SDK. Technology NVDEC can offload video decoding to full fixed-function decoding hardware (Nvidia PureVideo), or (partially) decode via CUDA software running on the GPU, if fixed-function hardware is not available. Depending on the GPU architecture, the following codecs are supported: * MPEG-2 * VC-1 * H.264 (AVC) * H.265 (HEVC) * VP8 * VP9 * AV1 Versions NVCUVID was originally distributed as part of the Nvidia CUDA Toolkit. Later, it was renamed to NVDEC and moved to the Nvidia Video Codec SDK. Operating system support NVDEC is available for Windows and Linux operating systems. As NVDEC is a proprietary API (as opposed to the open-source VDPAU API), it is only supported by the proprietary Nvidia driver on Linux. Application and library s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nvidia PureVideo

PureVideo is Nvidia's hardware SIP core that performs video decoding. PureVideo is integrated into some of the Nvidia GPUs, and it supports hardware decoding of multiple video codec standards: MPEG-2, VC-1, H.264, HEVC, and AV1. PureVideo occupies a considerable amount of a GPU's die area and should not be confused with Nvidia NVENC. In addition to video decoding on chip, PureVideo offers features such as edge enhancement, noise reduction, deinterlacing, dynamic contrast enhancement and color enhancement. Operating system support The PureVideo SIP core needs to be supported by the device driver, which provides one or more interfaces such as NVDEC, VDPAU, VAAPI or DXVA. One of these interfaces is then used by end-user software, for example VLC media player or GStreamer, to access the PureVideo hardware and make use of it. Nvidia's proprietary device driver is available for multiple operating systems and support for PureVideo has been added to it. Additionally, a free device d ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

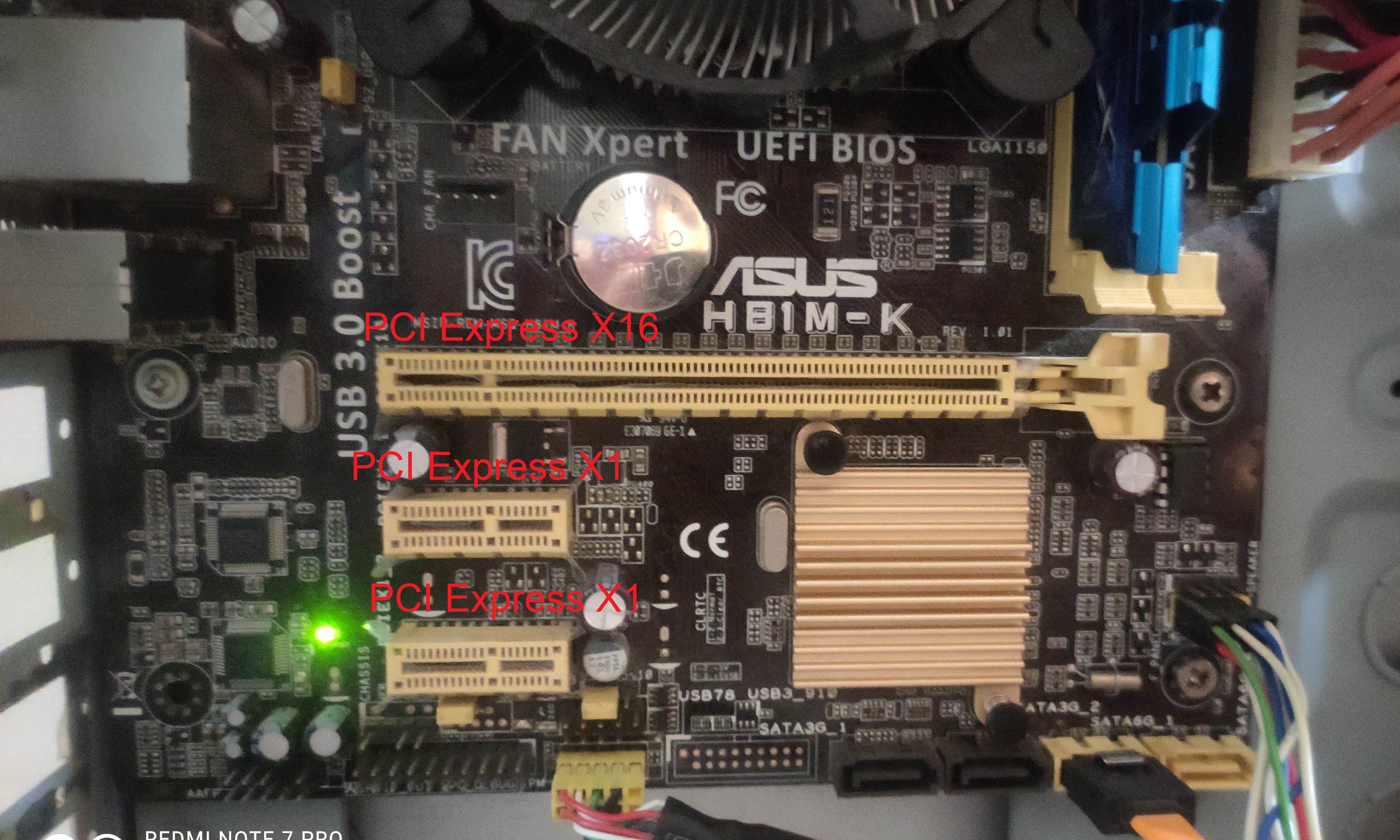

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directions. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

NVLink

NVLink is a wire-based serial multi-lane near-range communications link developed by Nvidia. Unlike PCI Express, a device can consist of multiple NVLinks, and devices use mesh networking to communicate instead of a central hub. The protocol was first announced in March 2014 and uses a proprietary high-speed signaling interconnect (NVHS). Principle NVLink is a wire-based communications protocol for near-range semiconductor communications developed by Nvidia that can be used for data and control code transfers in processor systems between CPUs and GPUs and solely between GPUs. NVLink specifies a point-to-point connection with data rates of 20, 25 and 50 Gbit/s (v1.0/v2.0/v3.0 resp.) per differential pair. Eight differential pairs form a "sub-link" and two "sub-links", one for each direction, form a "link". The total data rate for a sub-link is 25 GByte/s and the total data rate for a link is 50 GByte/s. Each V100 GPU supports up to six links. Thus, each GPU is capable of supporti ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FinFET

A fin field-effect transistor (FinFET) is a multigate device, a MOSFET (metal-oxide-semiconductor field-effect transistor) built on a substrate where the gate is placed on two, three, or four sides of the channel or wrapped around the channel, forming a double or even multi gate structure. These devices have been given the generic name "FinFETs" because the source/drain region forms fins on the silicon surface. The FinFET devices have significantly faster switching times and higher current density than planar CMOS (complementary metal-oxide-semiconductor) technology. FinFET is a type of non-planar transistor, or "3D" transistor. It is the basis for modern nanoelectronic semiconductor device fabrication. Microchips utilizing FinFET gates first became commercialized in the first half of the 2010s, and became the dominant gate design at 14 nm, 10 nm and 7 nm process nodes. It is common for a single FinFET transistor to contain several fins, arranged side by side and all covered ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

TSMC

Taiwan Semiconductor Manufacturing Company Limited (TSMC; also called Taiwan Semiconductor) is a Taiwanese multinational corporation, multinational semiconductor contract manufacturing and design company. It is the world's most valuable semiconductor company, the world's largest dedicated independent (Pure-play semiconductor foundry, pure-play) Foundry (electronics), semiconductor foundry, and one of Taiwan's largest companies, with its headquarters and main operations located in the Hsinchu Science Park in Hsinchu. It is majority owned by foreign investors. Founded in Taiwan in 1987 by Morris Chang, TSMC was the world's first dedicated semiconductor foundry and has long been the leading company in its field. When Chang retired in 2018, after 31 years of TSMC leadership, Mark Liu became chairman and C. C. Wei became Chief Executive. It has been listed on the Taiwan Stock Exchange (TWSE: 2330) since 1993; in 1997 it became the first Taiwanese company to be listed on the New York ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CUDA

CUDA (or Compute Unified Device Architecture) is a parallel computing platform and application programming interface (API) that allows software to use certain types of graphics processing units (GPUs) for general purpose processing, an approach called general-purpose computing on GPUs (GPGPU). CUDA is a software layer that gives direct access to the GPU's virtual instruction set and parallel computational elements, for the execution of compute kernels. CUDA is designed to work with programming languages such as C, C++, and Fortran. This accessibility makes it easier for specialists in parallel programming to use GPU resources, in contrast to prior APIs like Direct3D and OpenGL, which required advanced skills in graphics programming. CUDA-powered GPUs also support programming frameworks such as OpenMP, OpenACC and OpenCL; and HIP by compiling such code to CUDA. CUDA was created by Nvidia. When it was first introduced, the name was an acronym for Compute Unified Device Architectur ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)