|

Fault Models

A fault model is an engineering model of something that could go wrong in the construction or operation of a piece of equipment. From the model, the designer or user can then predict the consequences of this particular fault. Fault models can be used in almost all branches of engineering. Basic fault models Basic fault models in digital circuits include: *Static faults, which give incorrect values at any speed and sensitized by performing only one operation: ** The stuck-at fault model. A signal, or gate output, is stuck at a 0 or 1 value, independent of the inputs to the circuit. ** The bridging fault model. Two signals are connected together when they should not be. Depending on the logic circuitry employed, this may result in a ''wired-OR'' or ''wired-AND'' logic function. Since there are ''O(n^2)'' potential bridging faults, they are normally restricted to signals that are physically adjacent in the design. ** The transistor faults. This model is used to describe faults ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Digital Circuit

In theoretical computer science, a circuit is a model of computation in which input values proceed through a sequence of gates, each of which computes a function. Circuits of this kind provide a generalization of Boolean circuits and a mathematical model for digital logic circuits. Circuits are defined by the gates they contain and the values the gates can produce. For example, the values in a Boolean circuit are Boolean values, and the circuit includes conjunction, disjunction, and negation gates. The values in an integer circuit are sets of integers and the gates compute set union, set intersection, and set complement, as well as the arithmetic operations addition and multiplication. Formal definition A circuit is a triplet (M, L, G), where * M is a set of values, * L is a set of gate labels, each of which is a function from M^ to M for some non-negative integer i (where i represents the number of inputs to the gate), and * G is a labelled graph, labelled directed acyclic gra ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Stuck-at Fault

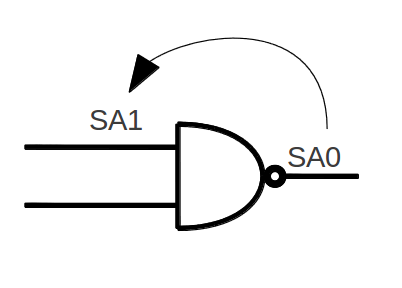

A stuck-at fault is a particular fault model used by fault simulators and automatic test pattern generation (ATPG) tools to mimic a manufacturing defect within an integrated circuit. Individual signals and pins are assumed to be ''stuck'' at Logical '1', '0' and 'X'. For example, an input is tied to a logical 1 state during test generation to assure that a manufacturing defect with that type of behavior can be found with a specific test pattern. Likewise the input could be tied to a logical 0 to model the behavior of a defective circuit that cannot switch its output pin. Not all faults can be analyzed using the stuck-at fault model. Compensation for static hazards, namely branching signals, can render a circuit untestable using this model. Also, redundant circuits cannot be tested using this model, since by design there is no change in any output as a result of a single fault. Single stuck at line Single stuck line is a fault model used in digital circuits. It is used for post ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bridging Fault

In electronic engineering, a bridging fault consists of two signals that are connected when they should not be. Depending on the logic circuitry employed, this may result in a wired-OR or wired-AND logic function. Since there are O(n^2) potential bridging faults, they are normally restricted to signals that are physically adjacent in the design. Modeling bridge fault Bridging to VDD or Vss is equivalent to stuck at fault model. Traditionally bridged signals were modeled with logic AND or OR of signals. If one driver dominates the other driver in a bridging situation, the dominant driver forces the logic to the other one, in such case a ''dominant bridging fault'' is used. To better reflect the reality of CMOS VLSI devices, a ''dominant AND or dominant OR bridging fault model'' is used where dominant driver keeps its value, while the other signal value is the result of AND (or OR) of its own value with the dominant driver. References"Bridging Fault Model"from ''Test and Diagnosis fo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Transistor Fault

Transistor Fault model is a Fault model used to describe faults for CMOS logic gates. At transistor level, a transistor may be stuck-short or stuck-open. In stuck-short, a transistor behaves as it is always conducts (or stuck-on), and stuck-open is when a transistor never conducts current (or stuck-off). Stuck-short will usually produce a short between VDD and VSS.  In the example picture, a faulty PMOS logic, PMOS transistor in a CMOS NAND Gate is shown (M3-highlighted transistor). If M3 is stuck-open, then in case we apply A=1 and B=0 then the output of the circuit will become Z. And if M3 is stuck-short, then the output will always be connected to 1, and it also may short VCC to GND in case we apply A=B=1.

Digital electronics

Electronic design

Elect ...

In the example picture, a faulty PMOS logic, PMOS transistor in a CMOS NAND Gate is shown (M3-highlighted transistor). If M3 is stuck-open, then in case we apply A=1 and B=0 then the output of the circuit will become Z. And if M3 is stuck-short, then the output will always be connected to 1, and it also may short VCC to GND in case we apply A=B=1.

Digital electronics

Electronic design

Elect ...

[...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Open Fault

Open or OPEN may refer to: Music * Open (band), Australian pop/rock band * The Open (band), English indie rock band * ''Open'' (Blues Image album), 1969 * ''Open'' (Gerd Dudek, Buschi Niebergall, and Edward Vesala album), 1979 * ''Open'' (Gotthard album), 1999 * ''Open'' (Cowboy Junkies album), 2001 * ''Open'' (YFriday album), 2001 * ''Open'' (Shaznay Lewis album), 2004 * ''Open'' (Jon Anderson EP), 2011 * ''Open'' (Stick Men album), 2012 * ''Open'' (The Necks album), 2013 * Open (Kwon Eun-bi EP), 2021 * ''Open'', a 1967 album by Julie Driscoll, Brian Auger and the Trinity * ''Open'', a 1979 album by Steve Hillage * "Open" (Queensrÿche song) * "Open" (Mýa song) * "Open", the first song on The Cure album ''Wish'' Literature * ''Open'' (Mexican magazine), a lifestyle Mexican publication * ''Open'' (Indian magazine), an Indian weekly English language magazine featuring current affairs * ''OPEN'' (North Dakota magazine), an out-of-print magazine that was printed in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Delay Fault

Delay or DeLay may refer to: People * B. H. DeLay (1891–1923), American aviator and movie stunt pilot * Dorothy DeLay (1917–2002), American violin instructor * Florence Delay (born 1941), French academician and actor * Jan Delay, stage name of German musician Jan Phillip Eißfeldt (born 1976) * Jason Delay (born 1995), American baseball player * Jean Delay (1907–1987), French psychiatrist, neurologist, and writer * Paul deLay (1952–2007), American blues musician * Tom DeLay (born 1947), American politician * Tom Delay (businessman) (born 1959), British businessman * Vladislav Delay (born 1976), Finnish musician Other uses * Delay (audio effect), a technology for producing delayed playback of an audio signal * Delay (programming), a programming language construct for delaying evaluation of an expression * ''Delay 1968 ''Delay 1968'' is a compilation album by the German experimental rock band Can released in 1981. It comprises previously unreleased work recorded for Ca ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Fault Dominance Example

Fault commonly refers to: *Fault (geology), planar rock fractures showing evidence of relative movement *Fault (law), blameworthiness or responsibility Fault(s) may also refer to: Arts, entertainment, and media * "Fault", a song by Taproot from ''Welcome'' * "Fault" (''Law & Order: Special Victims Unit''), 2006 * ''Faults'' (film), 2014 Science and technology *Fault (computing), also called a ''trap'' or an ''exception'', a type of interrupt in software or operating systems *Fault (technology), an abnormal condition or defect that may lead to a failure *Electrical fault, an abnormal current Sport and competition *Fault (breeding), an undesirable aspect of structure or appearance of an animal *Fault, in pickleball, any infringement of the rules by a player *Fault, in show jumping, a penalty *Fault, in tennis jargon, a serve that fails to place a tennis ball in the correct area of play See also *Blame * Defect (other) *Error * Mistake (other) *Software bug ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Line-replaceable Unit

A line-replaceable unit (LRU), lower line-replaceable unit (LLRU), line-replaceable component (LRC), or line-replaceable item (LRI) is a modular component of an airplane, ship or spacecraft (or any other manufactured device) that is designed to be replaced quickly at an operating location (1st line). The different lines (distances) are essential for logistics planning and operation. An LRU is usually a sealed unit such as a radio or other auxiliary equipment. LRUs are typically assigned logistics control numbers (LCNs) or work unit codes (WUCs) to manage logistics operations. LRUs can improve maintenance operations, because they can be stocked and replaced quickly from distributed nearby on-site inventories (sometimes mobile storage), restoring the mobile systems to service, while the failed (unserviceable) LRU is undergoing complicated repair and overhaul actions in other support locations (lines). Because of their modularity, LRUs also can contribute reducing system costs and i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Auxiliary Power Unit

An auxiliary power unit (APU) is a device on a vehicle that provides energy for functions other than propulsion. They are commonly found on large aircraft and naval ships as well as some large land vehicles. Aircraft APUs generally produce 115 V AC voltage at 400 Hz (rather than 50/60 Hz in mains supply), to run the electrical systems of the aircraft; others can produce 28 V DC voltage. APUs can provide power through single or three-phase systems. A jet fuel starter (JFS) is a similar device to an APU but directly linked to the main engine and started by an onboard compressed air bottle. Transport aircraft History During World War I, the British Coastal class blimps, one of several types of airship operated by the Royal Navy, carried a ABC auxiliary engine. These powered a generator for the craft's radio transmitter and, in an emergency, could power an auxiliary air blower. One of the first military fixed-wing aircraft to use an APU was the British, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Automatic Test Pattern Generation

ATPG (acronym for both automatic test pattern generation and automatic test pattern generator) is an electronic design automation method or technology used to find an input (or test) sequence that, when applied to a digital circuit, enables automatic test equipment to distinguish between the correct circuit behavior and the faulty circuit behavior caused by defects. The generated patterns are used to test semiconductor devices after manufacture, or to assist with determining the cause of failure (failure analysis). The effectiveness of ATPG is measured by the number of modeled defects, or fault models, detectable and by the number of generated patterns. These metrics generally indicate test quality (higher with more fault detections) and test application time (higher with more patterns). ATPG efficiency is another important consideration that is influenced by the fault model under consideration, the type of circuit under test ( full scan, synchronous sequential, or asynchronous se ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Fault Coverage

Fault coverage refers to the percentage of some type of fault that can be detected during the test of any engineered system. High fault coverage is particularly valuable during manufacturing test, and techniques such as Design For Test (DFT) and automatic test pattern generation are used to increase it. Applications Digital electronics In digital electronics, fault coverage refers to stuck-at fault coverage.{{Cite book , last=Williams , first=Thomas W. , title=How Should Fault Coverage Be Defined? , last2=Sunter , first2=Stephen K. , publisher=18th IEEE VLSI Test Symposium (VTS 2000), 30 April - 4 May 2000, Montreal, Canada , year=2000 , pages=325-328 , doi=10.1109/VTS.2000.10003 It is measured by sticking each pin of the hardware model at logic '0' and logic '1', respectively, and running the test vectors. If at least one of the outputs differs from what is to be expected, the fault is said to be detected. Conceptually, the total number of simulation runs is twice the numbe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Single Stuck Line

A stuck-at fault is a particular fault model used by fault simulators and automatic test pattern generation (ATPG) tools to mimic a manufacturing defect within an integrated circuit. Individual signals and pins are assumed to be ''stuck'' at Logical '1', '0' and 'X'. For example, an input is tied to a logical 1 state during test generation to assure that a manufacturing defect with that type of behavior can be found with a specific test pattern. Likewise the input could be tied to a logical 0 to model the behavior of a defective circuit that cannot switch its output pin. Not all faults can be analyzed using the stuck-at fault model. Compensation for static hazards, namely branching signals, can render a circuit untestable using this model. Also, redundant circuits cannot be tested using this model, since by design there is no change in any output as a result of a single fault. Single stuck at line Single stuck line is a fault model used in digital circuits. It is used for post ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |