|

Stuck-at Fault

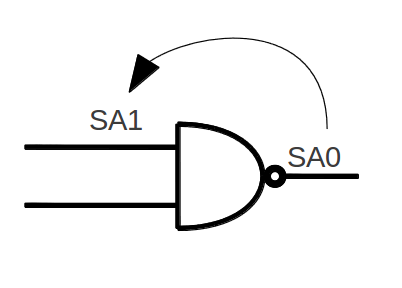

A stuck-at fault is a particular fault model used by fault simulators and automatic test pattern generation (ATPG) tools to mimic a manufacturing defect within an integrated circuit. Individual signals and pins are assumed to be ''stuck'' at Logical '1', '0' and 'X'. For example, an input is tied to a logical 1 state during test generation to assure that a manufacturing defect with that type of behavior can be found with a specific test pattern. Likewise the input could be tied to a logical 0 to model the behavior of a defective circuit that cannot switch its output pin. Not all faults can be analyzed using the stuck-at fault model. Compensation for static hazards, namely branching signals, can render a circuit untestable using this model. Also, redundant circuits cannot be tested using this model, since by design there is no change in any output as a result of a single fault. Single stuck at line Single stuck line is a fault model used in digital circuits. It is used for post ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Fault Model

A fault model is an engineering model of something that could go wrong in the construction or operation of a piece of equipment. From the model, the designer or user can then predict the consequences of this particular fault. Fault models can be used in almost all branches of engineering. Basic fault models Basic fault models in digital circuits include: *Static faults, which give incorrect values at any speed and sensitized by performing only one operation: ** The stuck-at fault model. A signal, or gate output, is stuck at a 0 or 1 value, independent of the inputs to the circuit. ** The bridging fault model. Two signals are connected together when they should not be. Depending on the logic circuitry employed, this may result in a ''wired-OR'' or ''wired-AND'' logic function. Since there are ''O(n^2)'' potential bridging faults, they are normally restricted to signals that are physically adjacent in the design. ** The transistor faults. This model is used to describe faults f ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Automatic Test Pattern Generation

ATPG (acronym for both automatic test pattern generation and automatic test pattern generator) is an electronic design automation method or technology used to find an input (or test) sequence that, when applied to a digital circuit, enables automatic test equipment to distinguish between the correct circuit behavior and the faulty circuit behavior caused by defects. The generated patterns are used to test semiconductor devices after manufacture, or to assist with determining the cause of failure (failure analysis). The effectiveness of ATPG is measured by the number of modeled defects, or fault models, detectable and by the number of generated patterns. These metrics generally indicate test quality (higher with more fault detections) and test application time (higher with more patterns). ATPG efficiency is another important consideration that is influenced by the fault model under consideration, the type of circuit under test ( full scan, synchronous sequential, or asynchronous se ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Integrated Circuit

An integrated circuit (IC), also known as a microchip or simply chip, is a set of electronic circuits, consisting of various electronic components (such as transistors, resistors, and capacitors) and their interconnections. These components are etched onto a small, flat piece ("chip") of semiconductor material, usually silicon. Integrated circuits are used in a wide range of electronic devices, including computers, smartphones, and televisions, to perform various functions such as processing and storing information. They have greatly impacted the field of electronics by enabling device miniaturization and enhanced functionality. Integrated circuits are orders of magnitude smaller, faster, and less expensive than those constructed of discrete components, allowing a large transistor count. The IC's mass production capability, reliability, and building-block approach to integrated circuit design have ensured the rapid adoption of standardized ICs in place of designs using discre ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Digital Circuits

Digital electronics is a field of electronics involving the study of digital signals and the engineering of devices that use or produce them. It deals with the relationship between binary inputs and outputs by passing electrical signals through logical gates, resistors, capacitors, amplifiers, and other electrical components. The field of digital electronics is in contrast to analog electronics which work primarily with analog signals (signals with varying degrees of intensity as opposed to on/off two state binary signals). Despite the name, digital electronics designs include important analog design considerations. Large assemblies of logic gates, used to represent more complex ideas, are often packaged into integrated circuits. Complex devices may have simple electronic representations of Boolean logic functions. History The binary number system was refined by Gottfried Wilhelm Leibniz (published in 1705) and he also established that by using the binary system, the pr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Negated AND Gate

In digital electronics, a NAND (NOT AND) gate is a logic gate which produces an output which is false only if all its inputs are true; thus its output is complement to that of an AND gate. A LOW (0) output results only if all the inputs to the gate are HIGH (1); if any input is LOW (0), a HIGH (1) output results. A NAND gate is made using transistors and junction diodes. By De Morgan's laws, a two-input NAND gate's logic may be expressed as \overline \lor \overline = \overline, making a NAND gate equivalent to inverters followed by an OR gate. The NAND gate is significant because any Boolean function can be implemented by using a combination of NAND gates. This property is called "functional completeness". It shares this property with the NOR gate. Digital systems employing certain logic circuits take advantage of NAND's functional completeness. NAND gates with two or more inputs are available as integrated circuits in transistor–transistor logic, CMOS, and other logic familie ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

OR Gate

The OR gate is a digital logic gate that implements logical disjunction. The OR gate outputs "true" if any of its inputs is "true"; otherwise it outputs "false". The input and output states are normally represented by different voltage levels. Description Any OR gate can be constructed with two or more inputs. It outputs a 1 if any of these inputs are 1, or outputs a 0 only if all inputs are 0. The inputs and outputs are binary digits ("bits") which have two possible truth value, logical states. In addition to 1 and 0, these states may be called true and false, high and low, active and inactive, or other such pairs of symbols. Thus it performs a logical disjunction (∨) from mathematical logic. The gate can be represented with the plus sign (+) because it can be used for Disjunction introduction, logical addition. Equivalently, an OR gate finds the ''maximum'' between two binary digits, just as the AND gate finds the ''minimum''. Together with the AND gate and the NOT gate, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

XOR Gate

XOR gate (sometimes EOR, or EXOR and pronounced as Exclusive OR) is a digital logic gate that gives a true (1 or HIGH) output when the number of true inputs is odd. An XOR gate implements an exclusive disjunction, exclusive or (\nleftrightarrow) from mathematical logic; that is, a true output results if one, and only one, of the inputs to the gate is true. If both inputs are false (0/LOW) or both are true, a false output results. XOR represents the inequality function, i.e., the output is true if the inputs are not alike otherwise the output is false. A way to remember XOR is "must have one or the other but not both". An XOR gate may serve as a "programmable inverter" in which one input determines whether to invert the other input, or to simply pass it along with no change. Hence it functions as a Inverter (logic gate), inverter (a NOT gate) which may be activated or deactivated by a switch. XOR can also be viewed as addition Modular arithmetic, modulo 2. As a result, XOR gates ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Transistor–transistor Logic

Transistor–transistor logic (TTL) is a logic family built from bipolar junction transistors (BJTs). Its name signifies that transistors perform both the logic function (the first "transistor") and the amplifying function (the second "transistor"), as opposed to earlier resistor–transistor logic (RTL) and diode–transistor logic (DTL). TTL integrated circuits (ICs) were widely used in applications such as computers, industrial controls, test equipment and instrumentation, consumer electronics, and synthesizers. After their introduction in integrated circuit form in 1963 by Sylvania Electric Products, TTL integrated circuits were manufactured by several semiconductor companies. The 7400 series by Texas Instruments became particularly popular. TTL manufacturers offered a wide range of logic gates, flip-flops, counters, and other circuits. Variations of the original TTL circuit design offered higher speed or lower power dissipation to allow design optimization. TTL devices w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Fault Coverage

Fault coverage refers to the percentage of some type of fault that can be detected during the test of any engineered system. High fault coverage is particularly valuable during manufacturing test, and techniques such as Design For Test (DFT) and automatic test pattern generation are used to increase it. Applications Digital electronics In digital electronics, fault coverage refers to stuck-at fault coverage.{{Cite book , last=Williams , first=Thomas W. , title=How Should Fault Coverage Be Defined? , last2=Sunter , first2=Stephen K. , publisher=18th IEEE VLSI Test Symposium (VTS 2000), 30 April - 4 May 2000, Montreal, Canada , year=2000 , pages=325-328 , doi=10.1109/VTS.2000.10003 It is measured by sticking each pin of the hardware model at logic '0' and logic '1', respectively, and running the test vectors. If at least one of the outputs differs from what is to be expected, the fault is said to be detected. Conceptually, the total number of simulation runs is twice the numbe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CMOS

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss ", , ) is a type of MOSFET, metal–oxide–semiconductor field-effect transistor (MOSFET) semiconductor device fabrication, fabrication process that uses complementary and symmetrical pairs of p-type semiconductor, p-type and n-type semiconductor, n-type MOSFETs for logic functions. CMOS technology is used for constructing integrated circuit (IC) chips, including microprocessors, microcontrollers, memory chips (including Nonvolatile BIOS memory, CMOS BIOS), and other digital logic circuits. CMOS technology is also used for analog circuits such as image sensors (CMOS sensors), data conversion, data converters, RF circuits (RF CMOS), and highly integrated transceivers for many types of communication. In 1948, Bardeen and Brattain patented an insulated-gate transistor (IGFET) with an inversion layer. Bardeen's concept forms the basis of CMOS technology today. The CMOS process was presented by Fairchild Semico ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Serendipity

Serendipity is an unplanned fortunate discovery. The term was coined by Horace Walpole in 1754. The concept is often associated with scientific and technological breakthroughs, where accidental discoveries led to new insights or inventions. Many significant discoveries in history were serendipitous, including penicillin, Post-it notes, Popsicles, and the microwave oven, arising from unforeseen circumstances that were then recognized and capitalized upon. Definition Christian Busch views serendipity as "active luck", where chance encounters and human action come together. A missed flight or a casual walk in the park can lead to new friendships, interests, or even career opportunities. While serendipity in popular usage is often understood as a matter of pure chance, scientific discussions emphasize the crucial role of human agency—recognizing, interpreting, and acting upon unexpected opportunities. This interaction between chance and conscious action has been a key theme ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Iddq Testing

Iddq testing is a method for testing CMOS integrated circuits for the presence of manufacturing faults. It relies on measuring the supply current (Idd) in the quiescent state (when the circuit is not switching and inputs are held at static values). The current consumed in the state is commonly called Iddq for Idd (quiescent) and hence the name. Iddq testing uses the principle that in a correctly operating quiescent CMOS digital circuit, there is no static current path between the power supply and ground, except for a small amount of leakage. Many common semiconductor manufacturing faults will cause the current to increase by orders of magnitude, which can be easily detected. This has the advantage of checking the chip for many possible faults with one measurement. Another advantage is that it may catch faults that are not found by conventional stuck-at fault test vectors. Iddq testing is somewhat more complex than just measuring the supply current. If a line is shorted to Vd ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |