|

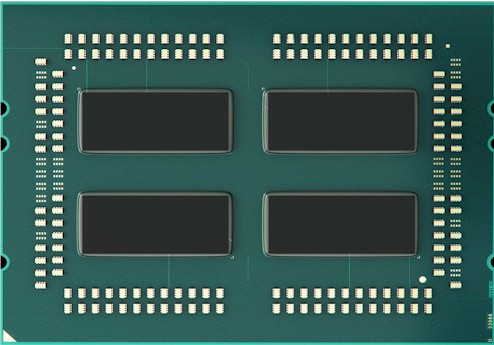

EPYC

Epyc is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets. Epyc processors share the same microarchitecture as their regular desktop-grade counterparts, but have enterprise-grade features such as higher core counts, more PCI Express lanes, support for larger amounts of RAM, and larger cache memory. They also support multi-chip and dual-socket system configurations by using the Infinity Fabric interconnect. History In March 2017, AMD announced plans to re-enter the server market with a platform based on the Zen microarchitecture, codenamed Naples, and officially revealed it under the brand name Epyc in May. That June, AMD officially launched Epyc 7001 series processors, offering up to 32 cores per socket, and enabling performance that allowed Epyc to be competitive with the competing Intel Xeon product line. Two years ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen 2

Zen 2 is a computer processor microarchitecture by AMD. It is the successor of AMD's Zen and Zen+ microarchitectures, and is fabricated on the 7 nanometer MOSFET node from TSMC. The microarchitecture powers the third generation of Ryzen processors, known as Ryzen 3000 for the mainstream desktop chips (codename "Matisse"), Ryzen 4000U/H (codename "Renoir") and Ryzen 5000U (codename "Lucienne") for mobile applications, as Threadripper 3000 for high-end desktop systems, and as Ryzen 4000G for accelerated processing units (APUs). The Ryzen 3000 series CPUs were released on 7 July 2019, while the Zen 2-based Epyc server CPUs (codename "Rome") were released on 7 August 2019. An additional chip, the Ryzen 9 3950X, was released in November 2019. At CES 2019, AMD showed a Ryzen third-generation engineering sample that contained one chiplet with eight cores and 16 threads. AMD CEO Lisa Su also said to expect more than eight cores in the final lineup. At Computex 2019, AMD revealed that ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen (first Generation Microarchitecture)

Zen is the codename for the first iteration in a family of computer processor microarchitectures of the same name from AMD. It was first used with their Ryzen series of CPUs in February 2017. The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017 and Zen-based APUs arrived in November 2017. Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer architecture. Zen-based processors use a 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. SMT has been introduced, allowing each core to run two threads. The cache system has also been redesigned, making the L1 cache write-back. Zen processors use three different sockets: desktop and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Secure Memory Encryption

Zen is the codename for the first iteration in a family of computer processor microarchitectures of the same name from AMD. It was first used with their Ryzen series of CPUs in February 2017. The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017 and Zen-based APUs arrived in November 2017. Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer architecture. Zen-based processors use a 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. SMT has been introduced, allowing each core to run two threads. The cache system has also been redesigned, making the L1 cache write-back. Zen processors use three different sockets: desktop and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

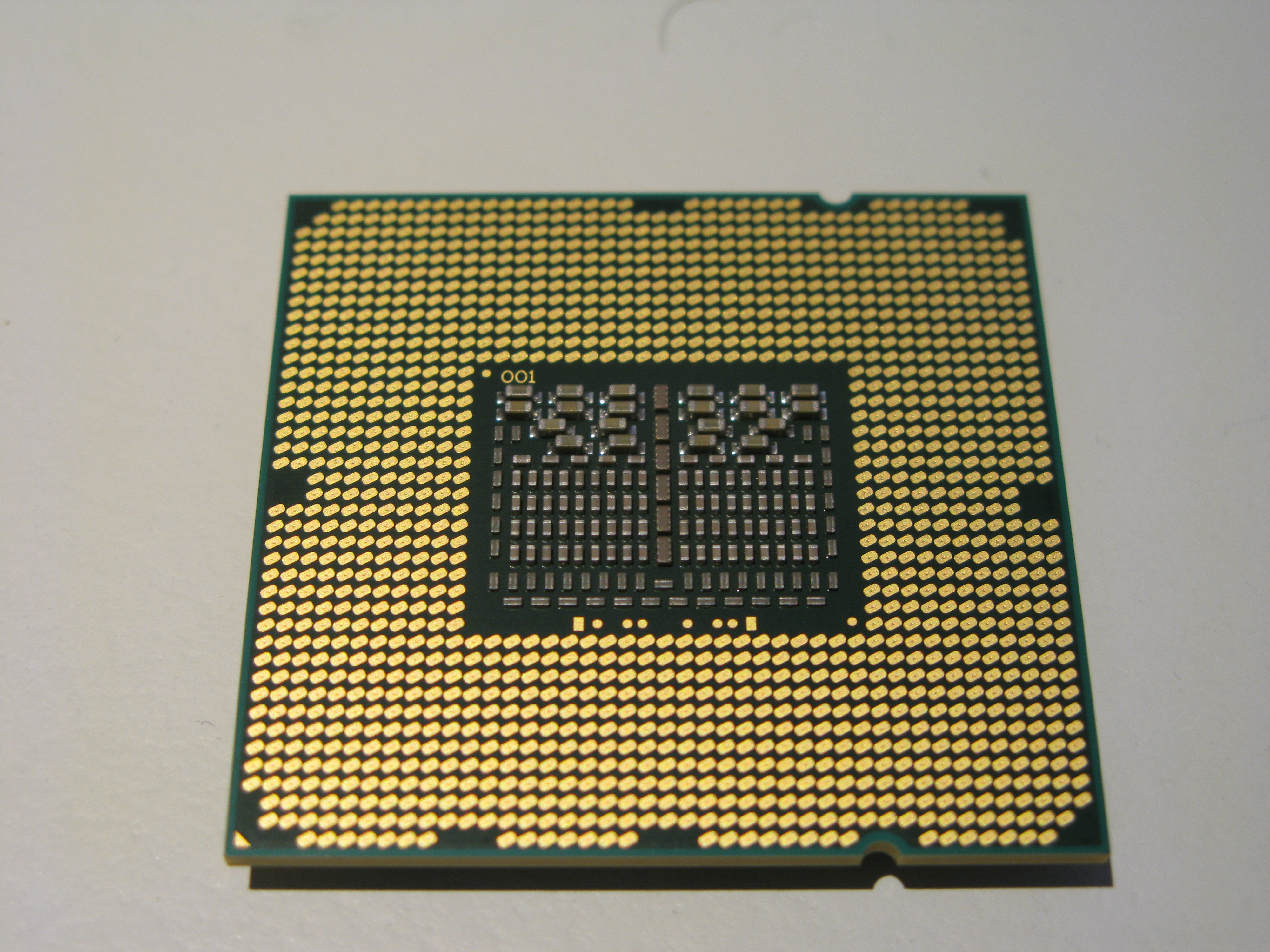

Socket SP5

Socket SP5 (LGA 6096) is a zero insertion force land grid array CPU socket designed by AMD supporting its Zen 4-based Epyc server processors that launched on November 10, 2022. History In June 2017, with the launch of the first generation Epyc server processors, AMD introduced the SP3 socket. The SP3 socket covered three generations of Epyc processors, including Naples, Rome and Milan. AMD's Genoa processors contain up to 96 Zen 4 cores compared to Milan's maximum of 64 cores. In support of Genoa's 96 cores, AMD introduced the SP5 socket with 2002 more contact pins than the SP3 socket to provide greater power delivery and signal integrity. SP5 can provide a peak power of up to 700W. The SP5 socket will support future Epyc processors, codenamed Bergamo, which has up to 128 Zen 4c cores and are set to debut in the first half of 2023. Additionally, some Bergamo processors will use SP5's successor, Socket SP6. Features * Supports 12 channels of DDR5 ECC RAM with 6TB maximum ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

7 Nm Process

In semiconductor manufacturing, the International Technology Roadmap for Semiconductors defines the 7 nm process as the MOSFET technology node following the 10 nm node. It is based on FinFET (fin field-effect transistor) technology, a type of multi-gate MOSFET technology. Taiwan Semiconductor Manufacturing Company (TSMC) began production of 256 Mbit SRAM memory chips using a 7 nm process called N7 in June 2016, before Samsung began mass production of their 7 nm process called 7LPP devices in 2018. The first mainstream 7 nm mobile processor intended for mass market use, the Apple A12 Bionic, was released at Apple's September 2018 event. Although Huawei announced its own 7 nm processor before the Apple A12 Bionic, the Kirin 980 on August 31, 2018, the Apple A12 Bionic was released for public, mass market use to consumers before the Kirin 980. Both chips are manufactured by TSMC. AMD has released their "Rome" (EPYC 2) processors for servers ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Socket SP3

Socket SP3 is a zero insertion force land grid array CPU socket designed by AMD supporting its Zen-, Zen 2- and Zen 3-based Epyc server processors, launched on June 20, 2017. Because the socket is the same size as Socket TR4, and Socket sTRX4, users can use CPU coolers designed for not only those sockets, but CPU coolers designed for sTR4 and sTRX4. Socket SP3 is a system in a package socket - that means most features required to make the system fully functional (such as memory, PCI Express, SATA controllers etc.) are fully integrated into the processor, eliminating the need for a chipset to be placed on a motherboard. Variants for desktop platforms (as said below) are, eventually, requiring additional chipset to provide improved functionality of the system. A processor using socket SP3 is mounted by inserting the CPU into a slide and fixing the slide assembly by tightening three screws using the torque wrenches normally provided alongside the motherboard. Automated processor mo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ryzen

Ryzen ( ) is a brand of multi-core x86-64 microprocessors designed and marketed by AMD for desktop, mobile, server, and embedded platforms based on the Zen microarchitecture. It consists of central processing units (CPUs) marketed for mainstream, enthusiast, server, and workstation segments and accelerated processing units (APUs) marketed for mainstream and entry-level segments and embedded systems applications. AMD announced a new series of processors on December 13, 2016, named "Ryzen", and delivered them in Q1 2017, the first of several generations. The 1000 series featured up to eight cores and 16 threads, with a 52% instructions per cycle (IPC) increase over their prior CPU products. The second generation of Ryzen processors, the Ryzen 2000 series, released in April 2018, featured the Zen+ microarchitecture, a 12 nm process (GlobalFoundries); the aggregate performance increased 10% (of which approximately 3% was IPC, 6% was frequency); most importantly, Zen+ fixed ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

X86-64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit version of the x86 instruction set, first released in 1999. It introduced two new modes of operation, 64-bit mode and compatibility mode, along with a new 4-level paging mode. With 64-bit mode and the new paging mode, it supports vastly larger amounts of virtual memory and physical memory than was possible on its 32-bit predecessors, allowing programs to store larger amounts of data in memory. x86-64 also expands general-purpose registers to 64-bit, and expands the number of them from 8 (some of which had limited or fixed functionality, e.g. for stack management) to 16 (fully general), and provides numerous other enhancements. Floating-point arithmetic is supported via mandatory SSE2-like instructions, and x87/ MMX style registers are generally not used (but still available even in 64-bit mode); instead, a set of 16 vector registers, 128 bits each, is used. (Each register can store one or two double-preci ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AVX-512

AVX-512 are 512-bit extensions to the 256-bit Advanced Vector Extensions SIMD instructions for x86 instruction set architecture (ISA) proposed by Intel in July 2013, and implemented in Intel's Xeon Phi x200 (Knights Landing) and Skylake-X CPUs; this includes the Core-X series (excluding the Core i5-7640X and Core i7-7740X), as well as the new Xeon Scalable Processor Family and Xeon D-2100 Embedded Series. AVX-512 consists of multiple extensions that may be implemented independently. This policy is a departure from the historical requirement of implementing the entire instruction block. Only the core extension AVX-512F (AVX-512 Foundation) is required by all AVX-512 implementations. Besides widening most 256-bit instructions, the extensions introduce various new operations, such as new data conversions, scatter operations, and permutations. The number of AVX registers is increased from 16 to 32, and eight new "mask registers" are added, which allow for variable selection and blendi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD-V

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel (VT-x) and AMD ( AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited ac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD-Vi

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel ( VT-x) and AMD ( AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel SHA Extensions

Intel SHA Extensions are a set of extensions to the x86 instruction set architecture which support hardware acceleration of Secure Hash Algorithm (SHA) family. It was introduced in 2013. There are seven new SSE-based instructions, four supporting SHA-1 and three for SHA-256: * SHA1RNDS4, SHA1NEXTE, SHA1MSG1, SHA1MSG2 * SHA256RNDS2, SHA256MSG1, SHA256MSG2 x86 architecture processors Intel The following Intel processors support SHA instruction set: * Intel Goldmont (and later Atom microarchitectures) processors. * Intel Ice Lake (and later) processors. * Intel Rocket Lake (and later) processors. AMD Several AMD processors support SHA instruction set: * AMD Zen Zen ( zh, t=禪, p=Chán; ja, text= 禅, translit=zen; ko, text=선, translit=Seon; vi, text=Thiền) is a school of Mahayana Buddhism that originated in China during the Tang dynasty, known as the Chan School (''Chánzong'' 禪宗), and ... (and later) processors. References External links New Instr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |