|

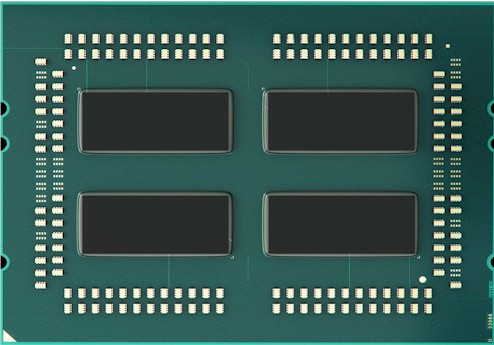

Epyc Genoa

Epyc is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets. Epyc processors share the same microarchitecture as their regular desktop-grade counterparts, but have enterprise-grade features such as higher core counts, more PCI Express lanes, support for larger amounts of RAM, and larger cache memory. They also support multi-chip and dual-socket system configurations by using the Infinity Fabric interconnect. History In March 2017, AMD announced plans to re-enter the server market with a platform based on the Zen microarchitecture, codenamed Naples, and officially revealed it under the brand name Epyc in May. That June, AMD officially launched Epyc 7001 series processors, offering up to 32 cores per socket, and enabling performance that allowed Epyc to be competitive with the competing Intel Xeon product line. Two years ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

14 Nm Process

The 14 nm process refers to the MOSFET technology node that is the successor to the 22nm (or 20nm) node. The 14nm was so named by the International Technology Roadmap for Semiconductors (ITRS). Until about 2011, the node following 22nm was expected to be 16nm. All 14nm nodes use FinFET (fin field-effect transistor) technology, a type of multi-gate MOSFET technology that is a non-planar evolution of planar silicon CMOS technology. Samsung Electronics taped out a 14 nm chip in 2014, before manufacturing 10 nm class NAND flash chips in 2013. The same year, SK Hynix began mass-production of 16nm NAND flash, and TSMC began 16nm FinFET production. The following year, Intel began shipping 14nm scale devices to consumers. History Background The basis for sub-20nm fabrication is the FinFET (Fin field-effect transistor), an evolution of the MOSFET transistor. FinFET technology was pioneered by Digh Hisamoto and his team of researchers at Hitachi Central Research Laboratory in 198 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Advanced Vector Extensions

Advanced Vector Extensions (AVX) are extensions to the x86 instruction set architecture for microprocessors from Intel and Advanced Micro Devices (AMD). They were proposed by Intel in March 2008 and first supported by Intel with the Sandy Bridge processor shipping in Q1 2011 and later by AMD with the Bulldozer processor shipping in Q3 2011. AVX provides new features, new instructions and a new coding scheme. AVX2 (also known as Haswell New Instructions) expands most integer commands to 256 bits and introduces new instructions. They were first supported by Intel with the Haswell processor, which shipped in 2013. AVX-512 expands AVX to 512-bit support using a new EVEX prefix encoding proposed by Intel in July 2013 and first supported by Intel with the Knights Landing co-processor, which shipped in 2016. In conventional processors, AVX-512 was introduced with Skylake server and HEDT processors in 2017. Advanced Vector Extensions AVX uses sixteen YMM registers to perform a sin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen (first Generation Microarchitecture)

Zen is the codename for the first iteration in a family of computer processor microarchitectures of the same name from AMD. It was first used with their Ryzen series of CPUs in February 2017. The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017 and Zen-based APUs arrived in November 2017. Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer architecture. Zen-based processors use a 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. SMT has been introduced, allowing each core to run two threads. The cache system has also been redesigned, making the L1 cache write-back. Zen processors use three different sockets: desktop and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD-Vi

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel ( VT-x) and AMD ( AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD-V

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel (VT-x) and AMD ( AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited ac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Secure Memory Encryption

Zen is the codename for the first iteration in a family of computer processor microarchitectures of the same name from AMD. It was first used with their Ryzen series of CPUs in February 2017. The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017 and Zen-based APUs arrived in November 2017. Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer architecture. Zen-based processors use a 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. SMT has been introduced, allowing each core to run two threads. The cache system has also been redesigned, making the L1 cache write-back. Zen processors use three different sockets: desktop and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel SHA Extensions

Intel SHA Extensions are a set of extensions to the x86 instruction set architecture which support hardware acceleration of Secure Hash Algorithm (SHA) family. It was introduced in 2013. There are seven new SSE-based instructions, four supporting SHA-1 and three for SHA-256: * SHA1RNDS4, SHA1NEXTE, SHA1MSG1, SHA1MSG2 * SHA256RNDS2, SHA256MSG1, SHA256MSG2 x86 architecture processors Intel The following Intel processors support SHA instruction set: * Intel Goldmont (and later Atom microarchitectures) processors. * Intel Ice Lake (and later) processors. * Intel Rocket Lake (and later) processors. AMD Several AMD processors support SHA instruction set: * AMD Zen Zen ( zh, t=禪, p=Chán; ja, text= 禅, translit=zen; ko, text=선, translit=Seon; vi, text=Thiền) is a school of Mahayana Buddhism that originated in China during the Tang dynasty, known as the Chan School (''Chánzong'' 禪宗), and ... (and later) processors. References External links New Instr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

RDRAND

RDRAND (for "read random"; known as Intel Secure Key Technology, previously known as Bull Mountain) is an instruction for returning random numbers from an Intel on-chip hardware random number generator which has been seeded by an on-chip entropy source. Intel introduced the feature around 2012, and AMD added support for the instruction in June 2015. (RDRAND is available in Ivy Bridge processors and is part of the Intel 64 and IA-32 instruction set architectures.) The random number generator is compliant with security and cryptographic standards such as NIST SP 800-90A, FIPS 140-2, and ANSI X9.82. Intel also requested Cryptography Research Inc. to review the random number generator in 2012, which resulted in the paper ''Analysis of Intel's Ivy Bridge Digital Random Number Generator''. RDSEED is similar to RDRAND and provides lower-level access to the entropy-generating hardware. The RDSEED generator and processor instruction rdseed are available with Intel Broadwell CPUs and A ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CLMUL Instruction Set

Carry-less Multiplication (CLMUL) is an extension to the x86 instruction set used by microprocessors from Intel and AMD which was proposed by Intel in March 2008 and made available in the Intel Westmere processors announced in early 2010. Mathematically, the instruction implements multiplication of polynomials over the finite field GF(2) where the bitstring a_0a_1\ldots a_ represents the polynomial a_0 + a_1X + a_2X^2 + \cdots + a_X^. The CLMUL instruction also allows a more efficient implementation of the closely related multiplication of larger finite fields GF(2''k'') than the traditional instruction set. One use of these instructions is to improve the speed of applications doing block cipher encryption in Galois/Counter Mode, which depends on finite field GF(2''k'') multiplication. Another application is the fast calculation of CRC values, including those used to implement the LZ77 sliding window DEFLATE algorithm in zlib and pngcrush. ARMv8 also has a version of CLMUL. SP ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AES Instruction Set

An Advanced Encryption Standard instruction set is now integrated into many processors. The purpose of the instruction set is to improve the speed and security of applications performing encryption and decryption using Advanced Encryption Standard (AES). They are often implemented as instructions implementing a single round of AES along with a special version for the last round which has a slightly different method. The side channel attack surface of AES is reduced when implemented in an instruction set, compared to when AES is implemented in software only. x86 architecture processors AES-NI (or the Intel Advanced Encryption Standard New Instructions; AES-NI) was the first major implementation. AES-NI is an extension to the x86 instruction set architecture for microprocessors from Intel and AMD proposed by Intel in March 2008. Instructions Intel The following Intel processors support the AES-NI instruction set: * Westmere based processors, specifically: ** Westmere ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bit Manipulation Instruction Sets

Bit manipulation instructions sets (BMI sets) are extensions to the x86 instruction set architecture for microprocessors from Intel and AMD. The purpose of these instruction sets is to improve the speed of bit manipulation. All the instructions in these sets are non-SIMD and operate only on general-purpose registers. There are two sets published by Intel: BMI (now referred to as BMI1) and BMI2; they were both introduced with the Haswell microarchitecture with BMI1 matching features offered by AMD's ABM instruction set and BMI2 extending them. Another two sets were published by AMD: ABM (''Advanced Bit Manipulation'', which is also a subset of SSE4a implemented by Intel as part of SSE4.2 and BMI1), and TBM (''Trailing Bit Manipulation'', an extension introduced with Piledriver-based processors as an extension to BMI1, but dropped again in Zen-based processors). ABM (Advanced Bit Manipulation) AMD was the first to introduce the instructions that now form Intel's BMI1 as part o ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CVT16 Instruction Set

The F16C (previously/informally known as CVT16) instruction set is an x86 instruction set architecture extension which provides support for converting between half-precision and standard IEEE single-precision floating-point formats. History The CVT16 instruction set, announced by AMD on May 1, 2009, is an extension to the 128-bit SSE core instructions in the x86 and AMD64 instruction set. CVT16 is a revision of part of the SSE5 instruction set proposal announced on August 30, 2007, which is supplemented by the XOP and FMA4 instruction sets. This revision makes the binary coding of the proposed new instructions more compatible with Intel's AVX instruction extensions, while the functionality of the instructions is unchanged. In recent documents, the name F16C is formally used in both Intel and AMD x86-64 architecture specifications. Technical information There are variants that convert four floating-point values in an XMM register or 8 floating-point values in a YMM registe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |