|

Arrandale (microprocessor)

Arrandale is the code name for a family of mobile Intel processors, sold as mobile Intel Core i3, i5 and i7 as well as Celeron and Pentium. It is closely related to the desktop Clarkdale processor; both use dual-core dies based on the '' Westmere'' 32 nm die shrink of the Nehalem microarchitecture, and have integrated Graphics as well as PCI Express and DMI links. Arrandale is the successor of the 45 nm Core-microarchitecture-based Penryn processor that is used in many of the mobile Intel Core 2, Celeron and Pentium Dual-Core processors. While Penryn typically used both a north bridge and a south bridge, Arrandale already contains the major northbridge components, which are the memory controller, PCI Express bus for external graphics, integrated graphics, and the DMI interface, making it possible to build more compact systems. The Arrandale processor package contains two dies: the 32 nm processor die with the I/O connections, and the 45 nm Intel HD G ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

32 Nm

The 32 nm node is the step following the 45 nm process in CMOS (MOSFET) semiconductor device fabrication. "32-nanometre" refers to the average half-pitch (i.e., half the distance between identical features) of a memory cell at this technology level. Toshiba produced commercial 32 GiB NAND flash memory chips with the 32nm process in 2009. Intel and AMD produced commercial microchips using the 32-nanometre process in the early 2010s. IBM and the Common Platform also developed a 32 nm high-κ metal gate process. Intel began selling its first 32 nm processors using the Westmere architecture on 7 January 2010. The 28-nanometre node was an intermediate half-node die shrink based on the 32-nanometre process. The 32 nm process was superseded by commercial 22 nm technology in 2012. [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Westmere (microarchitecture)

Westmere (formerly Nehalem-C) is the code name given to the 32 nm die shrink of '' Nehalem''. While sharing the same CPU sockets, Westmere included Intel HD Graphics, while Nehalem did not. The first ''Westmere''-based processors were launched on January 7, 2010, by Intel Corporation. The Westmere architecture has been available under the Intel brands of Core i3, Core i5, Core i7, Pentium, Celeron and Xeon. Technology Westmere's feature improvements from Nehalem, as reported: * Native six-core ( Gulftown) and ten-core ( Westmere-EX) processors. * A new set of instructions that gives over 3x the encryption and decryption rate of Advanced Encryption Standard (AES) processes compared to before. ** Delivers seven new instructions ( AES instruction set or AES-NI), out of which six implement the AES algorithm, and PCLMULQDQ (see CLMUL instruction set) implements carry-less multiplication for use in cryptography and data compression. * Integrated graphics, added into the pro ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Celeron

Celeron is Intel's brand name for low-end IA-32 and x86-64 computer microprocessor models targeted at low-cost personal computers. Celeron processors are compatible with IA-32 software. They typically offer less performance per clock speed compared to flagship Intel CPU lines, such as the Pentium or Core brands. Celeron branded processors often have less cache or intentionally disabled advanced features, with variable impact on performance. While some Celeron designs have achieved strong performance for their segment, most of the Celeron line has exhibited noticeably degraded performance. This has been the primary justification for the higher cost of other Intel CPU brands versus the Celeron range. Introduced in April 1998, the first Celeron-branded CPU was based on the Pentium II. Subsequent Celeron-branded CPUs were based on the Pentium III, Pentium 4, Pentium M, and Intel Core. In September 2022, Intel announced that the Celeron brand, along with Pentium, will be replaced w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Core 2

Intel Core 2 is the processor family encompassing a range of Intel's consumer 64-bit x86-64 single-, dual-, and quad-core microprocessors based on the Core microarchitecture. The single- and dual-core models are single- die, whereas the quad-core models comprise two dies, each containing two cores, packaged in a multi-chip module. The Core 2 range was the last flagship range of Intel desktop processors to use a front-side bus. The introduction of Core 2 relegated the Pentium brand to the mid-range market, and reunified laptop and desktop CPU lines for marketing purposes under the same product name, which were formerly divided into the Pentium 4, Pentium D, and Pentium M brands. The ''Core 2'' processor line was introduced on July 27, 2006, comprising the ''Duo'' (dual-core) and ''Extreme'' (dual- or quad-core CPUs for enthusiasts), and in 2007, the ''Quad'' (quad-core) and ''Solo'' ( single-core) sub-brands. Intel Core 2 processors with vPro technology (designed for businesses ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Penryn (microprocessor)

Penryn is the code name of a processor from Intel that is sold in varying configurations as Core 2 Solo, Core 2 Duo, Core 2 Quad, Pentium and Celeron. During development, Penryn was the Intel code name for the 2007/2008 "Tick" of Intel's Tick-Tock cycle which shrunk Merom to 45 nanometers as CPUID model 23. The term "Penryn" is sometimes used to refer to all 45 nm chips with the Core architecture. Chips with Penryn architecture come in two sizes, with 6 MB and 3 MB L2 cache. Low power versions of Penryn are known as the Penryn-L; these are single-core processors. The Penryn-QC quad-cores are made from two chips with two cores and 6 MB of cache per chip. The desktop version of Penryn is Wolfdale and the dual-socket server version is Wolfdale-DP. Penryn-QC is related to Yorkfield on the desktop and Harpertown in servers. The MP server Dunnington chip is a more distant relative based on a different chip but using the same 45 nm Core microarchitecture. Penryn w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Core (microarchitecture)

The Intel Core microarchitecture (provisionally referred to as Next Generation Micro-architecture, and developed as Merom) is a multi-core processor microarchitecture launched by Intel in mid-2006. It is a major evolution over the Yonah, the previous iteration of the P6 microarchitecture series which started in 1995 with Pentium Pro. It also replaced the NetBurst microarchitecture, which suffered from high power consumption and heat intensity due to an inefficient pipeline designed for high clock rate. In early 2004 the new version of NetBurst (Prescott) needed very high power to reach the clocks it needed for competitive performance, making it unsuitable for the shift to dual/multi-core CPUs. On May 7, 2004 Intel confirmed the cancellation of the next NetBurst. Intel had been developing Merom, the 64-bit evolution of the Pentium M, since 2001, and decided to expand it to all market segments, replacing NetBurst in desktop computers and servers. It inherited from Pentium ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Direct Media Interface

In computing, Direct Media Interface (DMI) is Intel's proprietary link between the northbridge and southbridge on a computer motherboard. It was first used between the 9xx chipsets and the ICH6, released in 2004. Previous Intel chipsets had used the Intel Hub Architecture to perform the same function, and server chipsets use a similar interface called ''Enterprise Southbridge Interface'' (ESI). While the "DMI" name dates back to ICH6, Intel mandates specific combinations of compatible devices, so the presence of a DMI interface does not guarantee by itself that a particular northbridge–southbridge combination is allowed. DMI shares many characteristics with PCI Express, using multiple lanes and differential signaling to form a point-to-point link. Most implementations use a ×4 link, while some mobile systems (e.g. 915GMS, 945GMS/GSE/GU and the Atom N450) use a ×2 link, halving the bandwidth. The original implementation provides 10 Gbit/s (1 GB/s) in eac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PCI Express

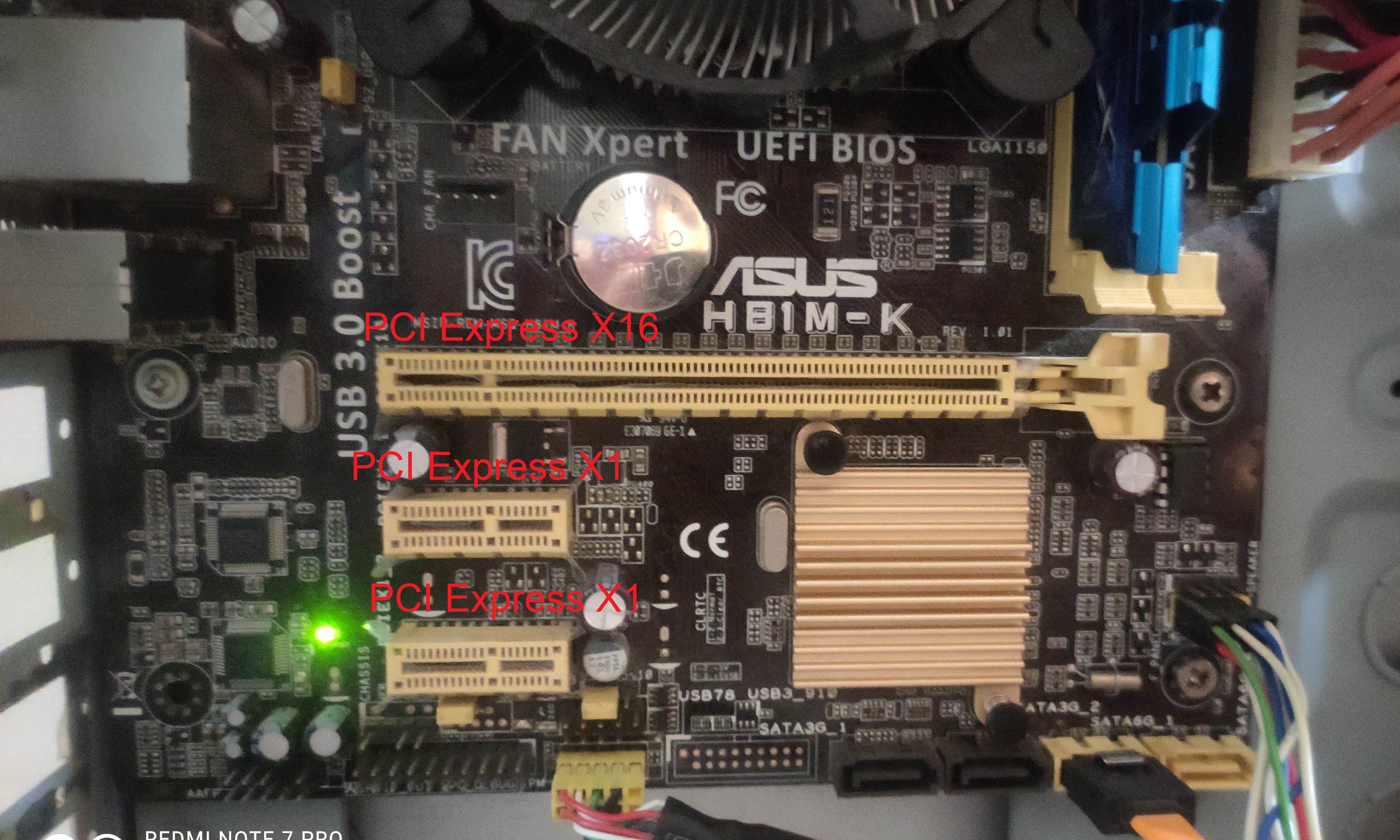

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both direc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nehalem (microarchitecture)

Nehalem is the codename for Intel's 45 nm microarchitecture released in November 2008. It was used in the first-generation of the Intel Core i5 and i7 processors, and succeeds the older Core microarchitecture used on Core 2 processors. The term "Nehalem" comes from the Nehalem River. Nehalem is built on the 45 nm process, is able to run at higher clock speeds, and is more energy-efficient than Penryn microprocessors. Hyper-threading is reintroduced, along with a reduction in L2 cache size, as well as an enlarged L3 cache that is shared among all cores. Nehalem is an architecture that differs radically from Netburst, while retaining some of the latter's minor features. Nehalem later received a die-shrink to 32 nm with Westmere, and was fully succeeded by "second-generation" Sandy Bridge in January 2011. Technology * Cache line block on L2/L3 cache was reduced from 128 bytes in Netburst & Conroe/Penryn to 64 bytes per line in this generation (same size as Yonah a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Die Shrink

The term die shrink (sometimes optical shrink or process shrink) refers to the scaling of metal-oxide-semiconductor (MOS) devices. The act of shrinking a die is to create a somewhat identical circuit using a more advanced fabrication process, usually involving an advance of lithographic nodes. This reduces overall costs for a chip company, as the absence of major architectural changes to the processor lowers research and development costs while at the same time allowing more processor dies to be manufactured on the same piece of silicon wafer, resulting in less cost per product sold. Details Die shrinks are the key to improving price/performance at semiconductor companies such as Samsung, Intel, TSMC, and SK Hynix, and fabless manufacturers such as AMD (including the former ATI), NVIDIA and MediaTek. Examples in the 2000s include the downscaling of the PlayStation 2's Emotion Engine processor from Sony and Toshiba (from 180 nm The 180 nm process r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

32 nm

The 32 nm node is the step following the 45 nm process in CMOS (MOSFET) semiconductor device fabrication. "32-nanometre" refers to the average half-pitch (i.e., half the distance between identical features) of a memory cell at this technology level. Toshiba produced commercial 32 GiB NAND flash memory chips with the 32nm process in 2009. Intel and AMD produced commercial microchips using the 32-nanometre process in the early 2010s. IBM and the Common Platform also developed a 32 nm high-κ metal gate process. Intel began selling its first 32 nm processors using the Westmere architecture on 7 January 2010. The 28-nanometre node was an intermediate half-node die shrink based on the 32-nanometre process. The 32 nm process was superseded by commercial 22 nm technology in 2012. [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Clarkdale (microprocessor)

Clarkdale is the codename for Intel's first-generation Core i5, i3 and Pentium dual-core desktop processors. It is closely related to the mobile Arrandale processor; both use dual-core dies based on the 32 nm Westmere microarchitecture and have integrated Graphics, PCI Express and DMI links built-in. Clarkdale is the successor of the Wolfdale used in desktop Intel Core 2, Celeron and Pentium Dual-Core processors. Unlike its predecessor, Clarkdale already contains the major north bridge components, such as memory controller, PCI Express for external graphics, integrated graphics and the DMI connector, making it possible to build more compact systems without a separate north bridge or discrete graphics like Lynnfield. The Clarkdale processor package contains two dies: the 32 nm processor die with the I/O connections, and the 45 nm graphics and integrated memory controller die. Physical separation of the processor die and memory controller die resulted in increase ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

_(JPG).jpg)