|

AES Instruction Set

An Advanced Encryption Standard instruction set (AES instruction set) is a set of instructions that are specifically designed to perform AES encryption and decryption operations efficiently. These instructions are typically found in modern processors and can greatly accelerate AES operations compared to software implementations. An AES instruction set includes instructions for key expansion, encryption, and decryption using various key sizes (128-bit, 192-bit, and 256-bit). The instruction set is often implemented as a set of instructions that can perform a single round of AES along with a special version for the last round which has a slightly different method. When AES is implemented as an instruction set instead of as software, it can have improved security, as its side channel attack surface is reduced. x86 architecture processors AES-NI (or the Intel Advanced Encryption Standard New Instructions; AES-NI) was the first major implementation. AES-NI is an extension to the x8 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AES Encryption

The Advanced Encryption Standard (AES), also known by its original name Rijndael (), is a specification for the encryption of electronic data established by the U.S. National Institute of Standards and Technology (NIST) in 2001. AES is a variant of the Rijndael block cipher developed by two Belgium, Belgian cryptographers, Joan Daemen and Vincent Rijmen, who submitted a proposal to NIST during the Advanced Encryption Standard process, AES selection process. Rijndael is a family of ciphers with different key size, key and Block size (cryptography), block sizes. For AES, NIST selected three members of the Rijndael family, each with a block size of 128 bits, but three different key lengths: 128, 192 and 256 bits. AES has been adopted by the Federal government of the United States, U.S. government. It supersedes the Data Encryption Standard (DES), which was published in 1977. The algorithm described by AES is a symmetric-key algorithm, meaning the same key is used for both encrypting ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ivy Bridge (computer Processor)

Ivy Bridge is the codename for Intel's 22 nm microarchitecture used in the third generation of the Intel Core processors (Core i7, i5, i3). Ivy Bridge is a die shrink to 22 nm process based on FinFET ("3D") Tri-Gate transistors, from the former generation's 32 nm Sandy Bridge microarchitecture—also known as tick–tock model. The name is also applied more broadly to the Xeon and Core i7 Extreme Ivy Bridge-E series of processors released in 2013. Ivy Bridge processors are backward compatible with the Sandy Bridge platform, but such systems might require a firmware update (vendor specific). In 2011, Intel released the 7-series Panther Point chipsets with integrated USB 3.0 and SATA 3.0 to complement Ivy Bridge. Volume production of Ivy Bridge chips began in the third quarter of 2011. Quad-core and dual-core-mobile models launched on April 29, 2012 and May 31, 2012 respectively. Core i3 desktop processors, as well as the first 22 nm ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen (microarchitecture)

Zen is a family of computer processor microarchitectures from AMD, first launched in February 2017 with the first generation of Ryzen CPUs. It is used in Ryzen (desktop and mobile), Ryzen Threadripper (workstation and high-end desktop), and Epyc (server). Zen 5 is the latest iteration of the architecture. Comparison History First generation The first-generation Zen was launched with the Ryzen 1000 series of CPUs (codenamed Summit Ridge) in February 2017. The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs reached the market in early March 2017, and Zen-derived Epyc server processors (codenamed "Naples") launched in June 2017 and Zen-based APUs (codenamed "Raven Ridge") arrived in November 2017. This first iteration of Zen utilized GlobalFoundries' 14 nm manufacturing process. Modified Zen-based processors for the Chinese mar ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Puma (microarchitecture)

The Puma Family 16h is a low-power microarchitecture by AMD for its APUs. It succeeds the Jaguar as a second-generation version, targets the same market, and belongs to the same AMD architecture Family 16h. The ''Beema'' line of processors are aimed at low-power notebooks, and ''Mullins'' are targeting the tablet sector. Design The Puma cores use the same microarchitecture as Jaguar, and inherits the design: * Out-of-order execution and Speculative execution, up to 4 CPU cores * Two-way integer execution * Two-way 128-bit wide floating-point and packed integer execution * Integer hardware divider * Puma does not feature clustered multi-thread (CMT), meaning that there are no "modules" * Puma does not feature Heterogeneous System Architecture or zero-copy * 32 KiB instruction + 32 KiB data L1 cache per core * 1–2 MiB unified L2 cache shared by two or four cores * Integrated single channel memory controller supporting 64bit DDR3L * 3.1 mm2 area per core ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Jaguar (microarchitecture)

The AMD Jaguar Family 16h is a low-power microarchitecture designed by AMD. It is used in APUs succeeding the Bobcat Family microarchitecture in 2013 and being succeeded by AMD's Puma architecture in 2014. It is two-way superscalar and capable of out-of-order execution. It is used in AMD's Semi-Custom Business Unit as a design for custom processors and is used by AMD in four product families: ''Kabini'' aimed at notebooks and mini PCs, ''Temash'' aimed at tablets, ''Kyoto'' aimed at micro-servers, and the ''G-Series'' aimed at embedded applications. Both the PlayStation 4 and the Xbox One use SoCs based on the Jaguar microarchitecture, with more powerful GPUs than AMD sells in its own commercially available Jaguar APUs. Design * 32 KiB instruction + 32 KiB data L1 cache per core, L1 cache includes parity error detection * 16-way, 1–2 MiB unified L2 cache shared by two or four cores, L2 cache is protected from errors by the use of error correcting code * Out- ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Excavator (microarchitecture)

AMD Excavator Family 15h is a microarchitecture developed by AMD to succeed Steamroller Family 15h for use in AMD APU processors and normal CPUs. On October 12, 2011, AMD revealed Excavator to be the code name for the fourth-generation Bulldozer-derived core. The Excavator-based APU for mainstream applications is called ''Carrizo'' and was released in 2015. The ''Carrizo'' APU is designed to be HSA 1.0 compliant. An Excavator-based APU and CPU variant named ''Toronto'' for server and enterprise markets was also produced. Excavator was the final revision of the "Bulldozer" family, with two new microarchitectures replacing Excavator a year later. Excavator was succeeded by the x86-64 Zen architecture in early 2017. Architecture Excavator added hardware support for new instructions such as AVX2, BMI2 and RDRAND. Excavator is designed using High Density (aka "Thin") Libraries normally used for GPUs to reduce electric energy consumption and die size, delivering a 30 percent inc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Steamroller (microarchitecture)

AMD Steamroller Family 15h is a microarchitecture developed by AMD for AMD APUs, which succeeded Piledriver in the beginning of 2014 as the third-generation Bulldozer-based microarchitecture. Steamroller APUs continue to use two-core modules as their predecessors, while aiming at achieving greater levels of parallelism. Microarchitecture ''Steamroller'' still features two-core modules found in ''Bulldozer'' and ''Piledriver'' designs called clustered multi-thread (CMT), meaning that one module is marketed as a dual-core processor. The focus of ''Steamroller'' is for greater parallelism. Improvements center on independent instruction decoders for each core within a module, 25% more of the maximum width dispatches per thread, better instruction schedulers, improved perceptron branch predictor, larger and smarter caches, up to 30% fewer instruction cache misses, branch misprediction rate reduced by 20%, dynamically resizable L2 cache, micro-operations queue, more internal regi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Piledriver (microarchitecture)

AMD Piledriver Family 15h is a microarchitecture developed by AMD as the second-generation successor to Bulldozer. It targets desktop, mobile and server markets. It is used for the AMD Accelerated Processing Unit (formerly Fusion), AMD FX, and the Opteron line of processors. The changes over Bulldozer are incremental. Piledriver uses the same "module" design. Its main improvements are to branch prediction and FPU/integer scheduling, along with a switch to hard-edge flip-flops to improve power consumption. This resulted in clock speed gains of 8–10% and a performance increase of around 15% with similar power characteristics. FX-9590 is around 40% faster than Bulldozer-based FX-8150, mostly because of higher clock speed. Products based on Piledriver were first released on 15 May 2012 with the AMD Accelerated Processing Unit (APU), code-named Trinity, series of mobile products. APUs aimed at desktops followed in early October 2012 with Piledriver-based FX-series CPUs released ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

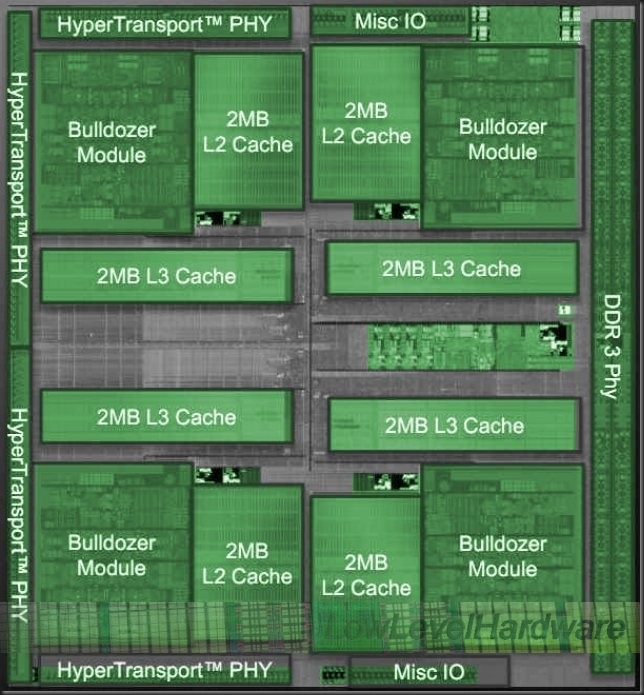

Bulldozer (microarchitecture)

The AMD Bulldozer Family 15h is a microprocessor microarchitecture for the FX and Opteron line of processors, developed by AMD for the desktop and server markets. Bulldozer is the codename for this family of microarchitectures. It was released on October 12, 2011, as the successor to the K10 microarchitecture. Bulldozer is designed from scratch, not a development of earlier processors. The core is specifically aimed at computing products with TDPs of 10 to 125 watts. AMD claims dramatic performance-per-watt efficiency improvements in high-performance computing (HPC) applications with Bulldozer cores. The ''Bulldozer'' cores support most of the instruction sets implemented by Intel processors ( Sandy Bridge) available at its introduction (including SSSE3, SSE4.1, SSE4.2, AES, CLMUL, and AVX) as well as new instruction sets proposed by AMD; ABM, XOP, FMA4 and F16C. Only Bulldozer GEN4 (Excavator) supports AVX2 instruction sets. Overview According to AMD, Bul ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Skylake (microarchitecture)

Skylake is Intel's codename for its sixth generation Core microprocessor family that was launched on August 5, 2015, succeeding the Broadwell microarchitecture. Skylake is a microarchitecture redesign using the same 14 nm manufacturing process technology as its predecessor, serving as a tock in Intel's tick–tock manufacturing and design model. According to Intel, the redesign brings greater CPU and GPU performance and reduced power consumption. Skylake CPUs share their microarchitecture with Kaby Lake, Coffee Lake, Whiskey Lake, and Comet Lake CPUs. Skylake is the last Intel platform on which Windows earlier than Windows 10 are officially supported by Microsoft, although enthusiast-created modifications are available that disabled the Windows Update check and allowed Windows 8.1 and earlier to continue to receive Windows Updates on this and later platforms. Some of the processors based on the Skylake microarchitecture are marketed as sixth-generation Core. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Goldmont

Goldmont is a microarchitecture for low-power Atom, Celeron and Pentium branded processors used in systems on a chip (SoCs) made by Intel. They allow only one thread per core. The ''Apollo Lake'' platform with 14 nm Goldmont core was unveiled at the Intel Developer Forum (IDF) in Shenzhen, China, April 2016. The Goldmont architecture borrows heavily from the Skylake Core processors, so it offers a more than 30 percent performance boost compared to the previous Braswell platform, and it can be used to implement power-efficient low-end devices including Cloudbooks, 2-in-1 netbooks, small PCs, IP cameras, and in-car entertainment systems. Design Goldmont is the 2nd generation out-of-order low-power Atom microarchitecture designed for the entry level desktop and notebook computers. Goldmont is built on the 14 nm manufacturing process and supports up to four cores for the consumer devices. It includes the Intel Gen9 graphics architecture introduced with the Skylake. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |