|

Socket FP3

The Socket FP3 or μBGA906 is a CPU socket for laptops that was released in June 2014 by AMD with its mobility APU products codenamed ''Kaveri''. ''"Kaveri"''-branded products combine Steamroller with Crystal Series (GCN), UVD 4.2 and VCE 2 video acceleration, AMD TrueAudio audio acceleration and AMD Eyefinity-based multi-monitor support of up to two non-DisplayPort- or up to four DisplayPort monitors. * ECC DIMMs are supported on Socket FP3, mixing of ECC and non-ECC DIMMs within a system is not supported. * There are 3 PCI Express cores: one 2 x16 core and two 5 x8 cores, for a total of 64 lanes. There are 8 configurable ports, which can be divided into 2 groups: ** Gfx-group: contains 2 x8 ports. Each port can be limited to lower link widths for applications that require fewer lanes. Additionally, the two ports can be combined to create a single x16 link. ** GPP-group: contains 1 x4 UMI and 5 General Purpose Ports (GPP). All PCIe links are capable of supporting PCIe 2 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Micro Ball Grid Array

A ball grid array (BGA) is a type of surface-mount packaging (a chip carrier) used for integrated circuits. BGA packages are used to permanently mount devices such as microprocessors. A BGA can provide more interconnection pins than can be put on a dual in-line or flat package. The whole bottom surface of the device can be used, instead of just the perimeter. The traces connecting the package's leads to the wires or balls which connect the die to package are also on average shorter than with a perimeter-only type, leading to better performance at high speeds. Soldering of BGA devices requires precise control and is usually done by automated processes such as in computer-controlled automatic reflow ovens. Description The BGA is descended from the pin grid array (PGA), which is a package with one face covered (or partly covered) with pins in a grid pattern which, in operation, conduct electrical signals between the integrated circuit and the printed circuit board (PCB) on wh ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DisplayPort

DisplayPort (DP) is a digital interface used to connect a video source, such as a Personal computer, computer, to a display device like a Computer monitor, monitor. Developed by the Video Electronics Standards Association (VESA), it can also carry digital audio, USB, and other types of data over a single cable. Introduced in the 2000s, DisplayPort was designed to replace older standards like VGA connector, VGA, DVI, and FPD-Link. While not directly compatible with these formats, Adapter, adapters are available for connecting to HDMI, DVI, VGA, and other interfaces. Unlike older interfaces, DisplayPort uses Data packet, packet-based transmission, similar to how data is sent over USB or Ethernet. The design enables support for high resolutions and adding new features without changing the connector. DisplayPort includes an auxiliary data channel used for device control and automatic configuration between source and display devices. It supports standards such as Display Data Channe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of AMD Processors With 3D Graphics

This is a list of microprocessors designed by AMD containing a 3D integrated graphics processing unit (iGPU), including those under the AMD APU (Accelerated Processing Unit) product series. Features overview Graphics API overview Desktop processors with 3D graphics APU or Radeon Graphics branded Lynx: "Llano" (2011) * Socket Socket FM1, FM1 * CPU: AMD 10h, K10 (also ''Husky'' or ''K10.5'') cores with an upgraded ''Stars'' architecture, no L3 cache ** L1 cache: 64 KB Data per core and 64 KB Instruction cache per core ** L2 cache: 512 KB on dual-core, 1 MB on tri- and quad-core models ** ''MMX (instruction set), MMX, 3DNow!, Enhanced 3DNow!, Streaming SIMD Extensions, SSE, SSE2, SSE3, SSE4a, Bit Manipulation Instruction Sets#ABM (Advanced Bit Manipulation), ABM, NX bit, Amd64, AMD64, Cool'n'Quiet'', ''AMD-V'' * GPU: TeraScale 2, TeraScale 2 (Evergreen); all A and E series models feature ''Redwood''-class integrated graphics on die (''BeaverCreek'' for the dual-core varia ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Socket FM2+

Socket FM2+ (FM2b, FM2r2) is a zero insertion force CPU socket designed by AMD for their desktop "Kaveri" APUs (Steamroller-based) and Godavari APUs (Steamroller-based) to connect to the motherboard. The FM2+ has a slightly different pin configuration to Socket FM2 with two additional pin sockets. Socket FM2+ APUs are not compatible with Socket FM2 motherboards due to the aforementioned additional pins. However, socket FM2 APUs such as "Richland" and "Trinity" are compatible with the FM2+ socket. * ECC DIMMs are supported on Socket FP3 but ''not'' supported on the Socket FM2+ package. * There are 3 PCI Express cores: one 2 ×16 core and two 5 ×8 cores. There are 8 configurable ports, which can be divided into 2 groups: ** Gfx-group: contains 2 ×8 ports. Each port can be limited to lower link widths for applications that require fewer lanes. Additionally, the two ports can be combined to create a single ×16 link. ** GPP-group: contains 1 ×4 UMI and 5 General Purpose Ports (GPP ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR3 SDRAM

Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth (" double data rate") interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors. DDR3 is a DRAM interface specification. The actual DRAM arrays that store the data are similar to earlier types, with similar performance. The primary benefit of DDR3 SDRAM over its immediate predecessor DDR2 SDRAM, is its ability to transfer data at twice the rate (eight times the speed of its internal memory arrays), enabling higher bandwidth or peak data rates. The DDR3 standard permits DRAM chip capacities of up to 8 gigabits (Gbit) (so 1 gigabyte by ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Volt

The volt (symbol: V) is the unit of electric potential, Voltage#Galvani potential vs. electrochemical potential, electric potential difference (voltage), and electromotive force in the International System of Units, International System of Units (SI). Definition One volt is defined as the electric potential between two points of a electrical conductor, conducting wire when an electric current of one ampere dissipates one watt of power (physics), power between those points. It can be expressed in terms of SI base units (metre, m, kilogram, kg, second, s, and ampere, A) as : \text = \frac = \frac = \frac = \text\text^2\text^. Equivalently, it is the potential difference between two points that will impart one joule of energy per coulomb of charge that passes through it. It can be expressed in terms of SI base units (metre, m, kilogram, kg, second, s, and ampere, A) as : \text = \frac = \frac = \frac = \text\text^2\text^. It can also be expressed as amperes times ohms (curre ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

UMI AMD

The Unified Media Interface (UMI) interconnect is the link between an AMD Accelerated Processing Unit (APU) and the FCH (Fusion Controller Hub). It is similar to Intel's DMI, and is based on PCI Express PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe, is a high-speed standard used to connect hardware components inside computers. It is designed to replace older expansion bus standards such as Peripher .... The Fusion Controller Hub is similar to the southbridge of earlier chipsets. References AMD technologies Computer buses {{computer-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

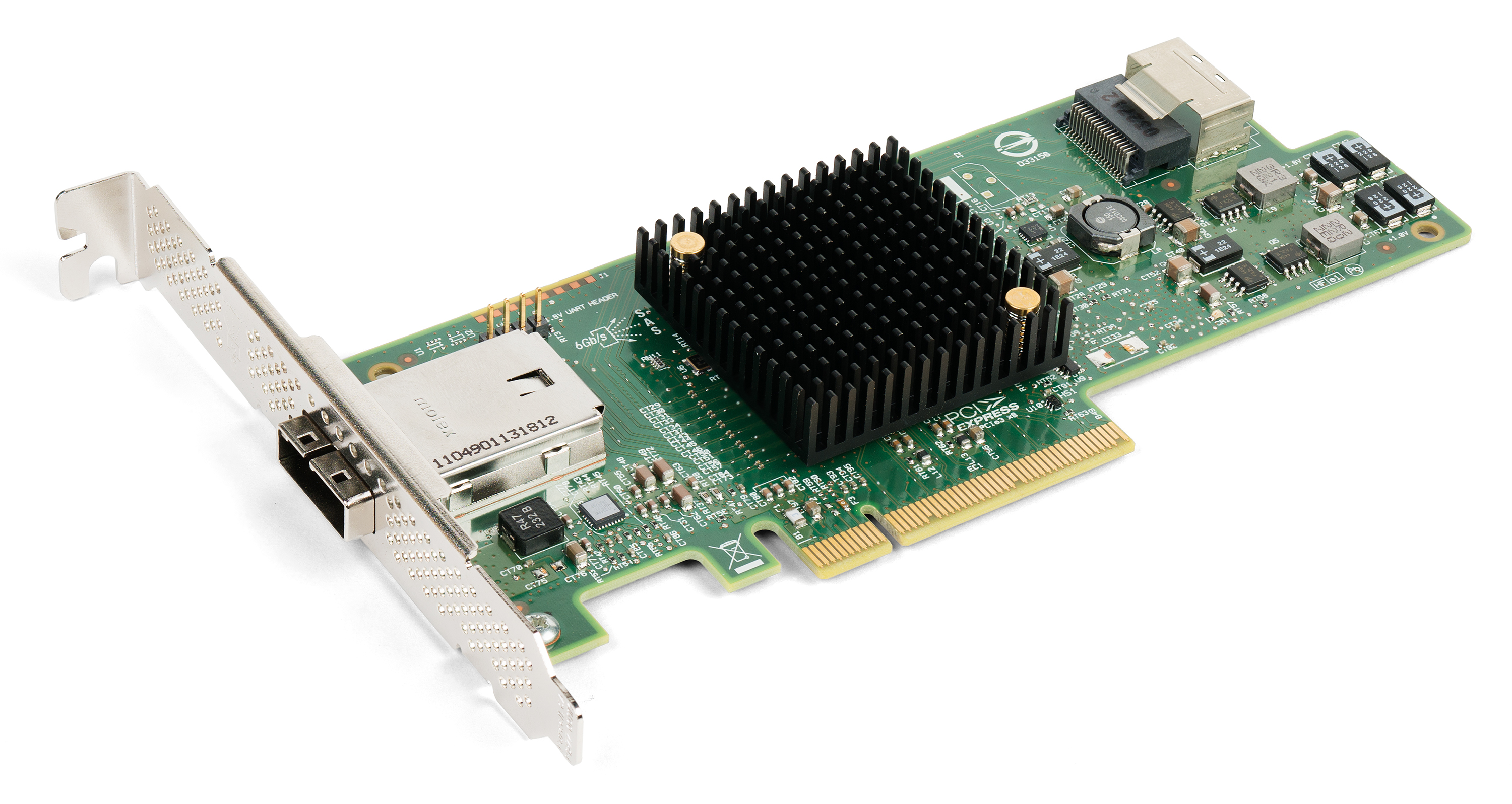

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe, is a high-speed standard used to connect hardware components inside computers. It is designed to replace older expansion bus standards such as Peripheral Component Interconnect, PCI, PCI-X and Accelerated Graphics Port, AGP. Developed and maintained by the PCI-SIG (PCI Special Interest Group), PCIe is commonly used to connect graphics cards, sound cards, Wi-Fi and Ethernet adapters, and storage devices such as solid-state drives and hard disk drives. Compared to earlier standards, PCIe supports faster data transfer, uses fewer pins, takes up less space, and allows devices to be added or removed while the computer is running (hot swapping). It also includes better error detection and supports newer features like I/O virtualization for advanced computing needs. PCIe connections are made through "lanes," which are pairs of wires that send and receive data. Devices can use one or more lanes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ECC Memory

Error correction code memory (ECC memory) is a type of computer data storage that uses an error correction code (ECC) to detect and correct ''n''-bit data corruption which occurs in memory. Typically, ECC memory maintains a memory system immune to single-bit errors: the data that is read from each word is always the same as the data that had been written to it, even if one of the bits actually stored has been flipped to the wrong state. Most non-ECC memory cannot detect errors, although some non-ECC memory with parity support allows detection but not correction. ECC memory is used in most computers where data corruption cannot be tolerated, like industrial control applications, critical databases, and infrastructural memory caches. Concept Error correction codes protect against undetected data corruption and are used in computers where such corruption is unacceptable, examples being scientific and financial computing applications, or in database and file servers. ECC can a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-monitor

Multi-monitor, also called multi-display and multi-head, is the use of multiple physical display devices, such as Computer monitor, monitors, Television set, televisions, and Video projector, projectors, in order to increase the area available for computer programs running on a single computer system. Research studies show that, depending on the type of work, multi-head may increase the productivity by between 50 and 70 percent. Implementation Multiple computers can be connected to provide a single display, e.g. over Gigabit Ethernet/Ethernet to drive a large video wall. Studies and safety Measurements of the Institute for Occupational Safety and Health of the German Social Accident Insurance showed that the quality and quantity of worker performance varies according to the screen setup and type of task. Overall, the results of physiological studies and the preferences of the test persons favour a dual-monitor rather than single-monitor setup. Physiologically limiting f ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD Accelerated Processing Unit

AMD Accelerated Processing Unit (APU), formerly known as Fusion, is a series of 64-bit microprocessors from Advanced Micro Devices (AMD), combining a general-purpose AMD64 central processing unit ( CPU) and 3D integrated graphics processing unit (IGPU) on a single die. AMD announced the first generation APUs, ''Llano'' for high-performance and ''Brazos'' for low-power devices, in January 2011 and launched the first units on June 14. The second generation ''Trinity'' for high-performance and ''Brazos-2'' for low-power devices were announced in June 2012. The third generation ''Kaveri'' for high performance devices were launched in January 2014, while ''Kabini'' and ''Temash'' for low-power devices were announced in the summer of 2013. Since the launch of the Zen microarchitecture, Ryzen and Athlon APUs have released to the global market as Raven Ridge on the DDR4 platform, after Bristol Ridge a year prior. AMD has also supplied semi-custom APUs for consoles starting with the r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD Eyefinity

AMD Eyefinity is a brand name for AMD video card products that support multi-monitor setups by integrating multiple (up to six) display controllers on one GPU. AMD Eyefinity was introduced with the Radeon HD 5000 series "Evergreen" in September 2009 and has been available on APUs and professional-grade graphics cards branded AMD FirePro as well. AMD Eyefinity supports a maximum of 2 non-DisplayPort displays (e.g., HDMI, DVI, VGA, DMS-59, VHDCI) (which AMD calls "legacy output") and up to 6 DisplayPort displays simultaneously using a single graphics card or APU. To feed more than two displays, the additional panels must have native DisplayPort support. Alternatively active DisplayPort-to-DVI/HDMI/VGA adapters can be employed. The setup of large video walls by connecting multiple computers over Gigabit Ethernet or Ethernet is also supported. The version of AMD Eyefinity (aka DCE, display controller engine) introduced with Excavator-based Carrizo APUs features a Video underl ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |