Fin field-effect transistor on:

[Wikipedia]

[Google]

[Amazon]

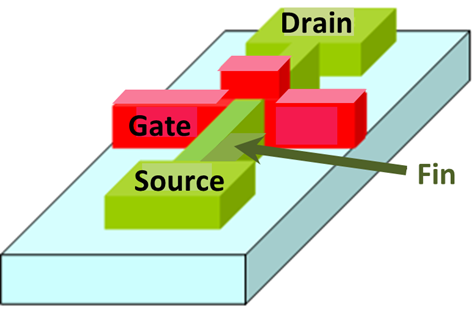

A fin field-effect transistor (FinFET) is a multigate device, a

A fin field-effect transistor (FinFET) is a multigate device, a

"The Silicon Age: Trends in Semiconductor Devices Industry

, 2022

MOSFET

The metal–oxide–semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET) is a type of field-effect transistor (FET), most commonly fabricated by the controlled oxidation of silicon. It has an insulated gate, the voltage of which d ...

(metal-oxide-semiconductor field-effect transistor

The field-effect transistor (FET) is a type of transistor that uses an electric field to control the flow of current in a semiconductor. FETs (JFETs or MOSFETs) are devices with three terminals: ''source'', ''gate'', and ''drain''. FETs contro ...

) built on a substrate

Substrate may refer to:

Physical layers

*Substrate (biology), the natural environment in which an organism lives, or the surface or medium on which an organism grows or is attached

** Substrate (locomotion), the surface over which an organism lo ...

where the gate is placed on two, three, or four sides of the channel or wrapped around the channel, forming a double or even multi gate structure. These devices have been given the generic name "FinFETs" because the source/drain region forms fins on the silicon surface. The FinFET devices have significantly faster switching time For a frequency synthesizer, the switching time or more colloquially the switching speed is the amount of time from when the command for the next frequency is requested until the time that the synthesizer's output becomes usable and meets the speci ...

s and higher current density

In electromagnetism, current density is the amount of charge per unit time that flows through a unit area of a chosen cross section. The current density vector is defined as a vector whose magnitude is the electric current per cross-sectional ar ...

than planar CMOS

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss", ) is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFE ...

(complementary metal-oxide-semiconductor) technology.

FinFET is a type of non-planar transistor

upright=1.4, gate (G), body (B), source (S) and drain (D) terminals. The gate is separated from the body by an insulating layer (pink).

A transistor is a semiconductor device used to Electronic amplifier, amplify or electronic switch, switch e ...

, or "3D" transistor. It is the basis for modern nanoelectronic semiconductor device fabrication

Semiconductor device fabrication is the process used to manufacture semiconductor devices, typically integrated circuit (IC) chips such as modern computer processors, microcontrollers, and memory chips such as NAND flash and DRAM that are pres ...

. Microchips utilizing FinFET gates first became commercialized in the first half of the 2010s, and became the dominant gate design at 14 nm

The 14 nm process refers to the MOSFET technology node that is the successor to the 22nm (or 20nm) node. The 14nm was so named by the International Technology Roadmap for Semiconductors (ITRS). Until about 2011, the node following 22nm was expe ...

, 10 nm

The following are examples of orders of magnitude for different lengths.

__TOC__

Overview

Detailed list

To help compare different orders of magnitude, the following list describes various lengths between 1.6 \times 10^ metres and 10^ ...

and 7 nm process nodes

In general, a node is a localized swelling (a "knot") or a point of intersection (a Vertex (graph theory), vertex).

Node may refer to:

In mathematics

*Vertex (graph theory), a vertex in a mathematical graph

*Vertex (geometry), a point where two ...

.

It is common for a single FinFET transistor to contain several fins, arranged side by side and all covered by the same gate, that act electrically as one, to increase drive strength and performance.

History

After the MOSFET was first demonstrated byMohamed Atalla

Mohamed M. Atalla ( ar, محمد عطاالله; August 4, 1924 – December 30, 2009) was an Egyptian-American engineer, physicist, cryptographer, inventor and entrepreneur. He was a semiconductor pioneer who made important contributions to ...

and Dawon Kahng of Bell Labs

Nokia Bell Labs, originally named Bell Telephone Laboratories (1925–1984),

then AT&T Bell Laboratories (1984–1996)

and Bell Labs Innovations (1996–2007),

is an American industrial research and scientific development company owned by mult ...

in 1960, the concept of a double-gate thin-film transistor (TFT) was proposed by H.R. Farrah (Bendix Corporation

Bendix Corporation is an American manufacturing and engineering company which, during various times in its existence, made automotive brake shoes and systems, vacuum tubes, aircraft brakes, aeronautical hydraulics and electric power systems, av ...

) and R.F. Steinberg in 1967. A double-gate MOSFET was later proposed by Toshihiro Sekigawa of the Electrotechnical Laboratory

The , or AIST, is a Japanese research facility headquartered in Tokyo, and most of the workforce is located in Tsukuba Science City, Ibaraki, and in several cities throughout Japan. The institute is managed to integrate scientific and engineeri ...

(ETL) in a 1980 patent

A patent is a type of intellectual property that gives its owner the legal right to exclude others from making, using, or selling an invention for a limited period of time in exchange for publishing an enabling disclosure of the invention."A p ...

describing the planar XMOS transistor. Sekigawa fabricated the XMOS transistor with Yutaka Hayashi at the ETL in 1984. They demonstrated that short-channel effect In electronics, short-channel effects occur in MOSFETs in which the channel length is comparable to the depletion layer widths of the source and drain junctions. These effects include, in particular, drain-induced barrier lowering, velocity saturati ...

s can be significantly reduced by sandwiching a fully depleted silicon-on-insulator

In semiconductor manufacturing, silicon on insulator (SOI) technology is fabrication of silicon semiconductor devices in a layered silicon–insulator–silicon substrate, to reduce parasitic capacitance within the device, thereby improving perfo ...

(SOI) device between two gate electrodes connected together.

The first FinFET transistor type was called a "Depleted Lean-channel Transistor" or "DELTA" transistor, which was first fabricated in Japan by Hitachi Central Research Laboratory's Digh Hisamoto, Toru Kaga, Yoshifumi Kawamoto and Eiji Takeda in 1989. The gate of the transistor can cover and electrically contact the semiconductor channel fin on both the top and the sides or only on the sides. The former is called a ''tri-gate transistor'' and the latter a ''double-gate transistor''. A double-gate transistor optionally can have each side connected to two different terminal or contacts. This variant is called ''split transistor''. This enables more refined control of the operation of the transistor.

Indonesian engineer Effendi Leobandung, while working at the University of Minnesota

The University of Minnesota, formally the University of Minnesota, Twin Cities, (UMN Twin Cities, the U of M, or Minnesota) is a public university, public Land-grant university, land-grant research university in the Minneapolis–Saint Paul, Tw ...

, published a paper with Stephen Y. Chou at the 54th Device Research Conference in 1996 outlining the benefit of cutting a wide CMOS

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss", ) is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFE ...

transistor into many channels with narrow width to improve device scaling and increase device current by increasing the effective device width. This structure is what a modern FinFET looks like. Although some device width is sacrificed by cutting it into narrow widths, the conduction of the side wall of narrow fins more than make up for the loss, for tall fins. The device had a 35 nm channel width and 70 nm channel length.

The potential of Digh Hisamoto's research on DELTA transistors drew the attention of the Defense Advanced Research Projects Agency

The Defense Advanced Research Projects Agency (DARPA) is a research and development agency of the United States Department of Defense responsible for the development of emerging technologies for use by the military.

Originally known as the Adv ...

(DARPA), which in 1997 awarded a contract to a research group at UC Berkeley

The University of California, Berkeley (UC Berkeley, Berkeley, Cal, or California) is a public university, public land-grant university, land-grant research university in Berkeley, California. Established in 1868 as the University of Californi ...

to develop a deep sub-micron transistor based on DELTA technology. The group was led by Hisamoto along with TSMC

Taiwan Semiconductor Manufacturing Company Limited (TSMC; also called Taiwan Semiconductor) is a Taiwanese multinational corporation, multinational semiconductor contract manufacturing and design company. It is the world's most valuable semicon ...

's Chenming Hu. The team made the following breakthroughs between 1998 and 2004.

*1998 N-channel

The field-effect transistor (FET) is a type of transistor that uses an electric field to control the flow of current in a semiconductor. FETs (JFETs or MOSFETs) are devices with three terminals: ''source'', ''gate'', and ''drain''. FETs control ...

FinFET ( 17 nm) Digh Hisamoto, Chenming Hu, Tsu-Jae King Liu, Jeffrey Bokor, Wen-Chin Lee, Jakub Kedzierski, Erik Anderson, Hideki Takeuchi, Kazuya Asano

*1999 P-channel

The field-effect transistor (FET) is a type of transistor that uses an electric field to control the flow of Electric current, current in a semiconductor. FETs (JFETs or MOSFETs) are devices with three terminals: ''source'', ''gate'', and ''dra ...

FinFET ( sub-50 nm) Digh Hisamoto, Chenming Hu, Xuejue Huang, Wen-Chin Lee, Charles Kuo, Leland Chang, Jakub Kedzierski, Erik Anderson, Hideki Takeuchi

*2001 15 nm FinFET Chenming Hu, Yang-Kyu Choi, Nick Lindert, P. Xuan, S. Tang, D. Ha, Erik Anderson, Tsu-Jae King Liu, Jeffrey Bokor

*2002 10 nm

The following are examples of orders of magnitude for different lengths.

__TOC__

Overview

Detailed list

To help compare different orders of magnitude, the following list describes various lengths between 1.6 \times 10^ metres and 10^ ...

FinFET Shibly Ahmed, Scott Bell, Cyrus Tabery, Jeffrey Bokor, David Kyser, Chenming Hu, Tsu-Jae King Liu, Bin Yu, Leland Chang

*2004 High-κ/ metal gate FinFET D. Ha, Hideki Takeuchi, Yang-Kyu Choi, Tsu-Jae King Liu, W. Bai, D.-L. Kwong, A. Agarwal, M. Ameen

They coined the term "FinFET" (fin field-effect transistor) in a December 2000 paper, used to describe a non-planar, double-gate transistor built on an SOI substrate.

In 2006, a team of Korean researchers from the Korea Advanced Institute of Science and Technology

The Korea Advanced Institute of Science and Technology (KAIST) is a national research university located in Daedeok Innopolis, Daejeon, South Korea. KAIST was established by the Korean government in 1971 as the nation's first public, research ...

(KAIST) and the National Nano Fab Center developed a 3 nm transistor, the world's smallest nanoelectronic device, based on gate-all-around

A multigate device, multi-gate MOSFET or multi-gate field-effect transistor (MuGFET) refers to a metal–oxide–semiconductor field-effect transistor (MOSFET) that has more than one gate on a single transistor. The multiple gates may be control ...

(GAA) FinFET technology. In 2011, Rice University

William Marsh Rice University (Rice University) is a Private university, private research university in Houston, Houston, Texas. It is on a 300-acre campus near the Houston Museum District and adjacent to the Texas Medical Center. Rice is ranke ...

researchers Masoud Rostami and Kartik Mohanram demonstrated that FinFETs can have two electrically independent gates, which gives circuit designers more flexibility to design with efficient, low-power gates.

In 2020, Chenming Hu received the IEEE Medal of Honor

The IEEE Medal of Honor is the highest recognition of the Institute of Electrical and Electronics Engineers (IEEE). It has been awarded since 1917, when its first recipient was Major Edwin H. Armstrong. It is given for an exceptional contribution ...

award for his development of the FinFET, which the Institute of Electrical and Electronics Engineers

The Institute of Electrical and Electronics Engineers (IEEE) is a 501(c)(3) professional association for electronic engineering and electrical engineering (and associated disciplines) with its corporate office in New York City and its operation ...

(IEEE) credited with taking transistors to the third dimension and extending Moore's law

Moore's law is the observation that the number of transistors in a dense integrated circuit (IC) doubles about every two years. Moore's law is an observation and projection of a historical trend. Rather than a law of physics, it is an empir ...

.

Commercialization

The industry's first 25 nanometer transistor operating on just 0.7volt

The volt (symbol: V) is the unit of electric potential, electric potential difference (voltage), and electromotive force in the International System of Units (SI). It is named after the Italian physicist Alessandro Volta (1745–1827).

Defi ...

s was demonstrated in December 2002 by TSMC

Taiwan Semiconductor Manufacturing Company Limited (TSMC; also called Taiwan Semiconductor) is a Taiwanese multinational corporation, multinational semiconductor contract manufacturing and design company. It is the world's most valuable semicon ...

. The "Omega FinFET" design, named after the similarity between the Greek letter "Omega

Omega (; capital: Ω, lowercase: ω; Ancient Greek ὦ, later ὦ μέγα, Modern Greek ωμέγα) is the twenty-fourth and final letter in the Greek alphabet. In the Greek numeric system/isopsephy (gematria), it has a value of 800. The wo ...

" and the shape in which the gate wraps around the source/drain structure, has a gate delay

Propagation delay is the time duration taken for a signal to reach its destination. It can relate to networking, electronics or physics. ''Hold time'' is the minimum interval required for the logic level to remain on the input after triggering ed ...

of just 0.39 picosecond

A picosecond (abbreviated as ps) is a unit of time in the International System of Units (SI) equal to 10−12 or (one trillionth) of a second. That is one trillionth, or one millionth of one millionth of a second, or 0.000 000 000 ...

(ps) for the N-type transistor and 0.88 ps for the P-type.

In 2004, Samsung

The Samsung Group (or simply Samsung) ( ko, 삼성 ) is a South Korean multinational manufacturing conglomerate headquartered in Samsung Town, Seoul, South Korea. It comprises numerous affiliated businesses, most of them united under the ...

demonstrated a "Bulk FinFET" design, which made it possible to mass-produce FinFET devices. They demonstrated dynamic random-access memory

Random-access memory (RAM; ) is a form of computer memory that can be read and changed in any order, typically used to store working Data (computing), data and machine code. A Random access, random-access memory device allows data items to b ...

(DRAM

Dynamic random-access memory (dynamic RAM or DRAM) is a type of random-access semiconductor memory that stores each bit of data in a memory cell, usually consisting of a tiny capacitor and a transistor, both typically based on metal-oxid ...

) manufactured with a 90nm

The 90 nm process refers to the level of MOSFET (CMOS) fabrication process technology that was commercialized by the 2003–2005 timeframe, by leading semiconductor companies like Toshiba, Sony, Samsung, IBM, Intel, Fujitsu, TSMC, Elpid ...

Bulk FinFET process.

In 2011, Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 seri ...

demonstrated tri-gate transistor

The 22 nm node is the process step following 32 nm in CMOS MOSFET semiconductor device fabrication. The typical half-pitch (i.e., half the distance between identical features in an array) for a memory cell using the process is around 22 n ...

s, where the gate surrounds the channel on three sides, allowing for increased energy efficiency and lower gate delay—and thus greater performance—over planar transistors.

Commercially produced chips at 22 nm

The 22 nm node is the process step following 32 nm in CMOS MOSFET semiconductor device fabrication. The typical half-pitch (i.e., half the distance between identical features in an array) for a memory cell using the process is around 22 nm. ...

and below have generally utilised FinFET gate designs (but planar processes do exist down to 18 nm, with 12 nm in development). Intel's tri-gate

A multigate device, multi-gate MOSFET or multi-gate field-effect transistor (MuGFET) refers to a metal–oxide–semiconductor field-effect transistor (MOSFET) that has more than one gate on a single transistor. The multiple gates may be contro ...

variant were announced at 22 nm in 2011 for its Ivy Bridge microarchitecture. These devices shipped from 2012 onwards. From 2014 onwards, at 14 nm

The 14 nm process refers to the MOSFET technology node that is the successor to the 22nm (or 20nm) node. The 14nm was so named by the International Technology Roadmap for Semiconductors (ITRS). Until about 2011, the node following 22nm was expe ...

(or 16 nm) major foundries (TSMC, Samsung, GlobalFoundries) utilised FinFET designs.

In 2013, SK Hynix

SK hynix Inc. is a South Korean supplier of dynamic random-access memory (DRAM) chips and flash memory chips. Hynix is the world's second-largest memory chipmaker (after Samsung Electronics) and the world's third-largest semiconductor company ...

began commercial mass-production of a 16nm process, TSMC began production of a 16nm FinFET process, and Samsung Electronics

Samsung Electronics Co., Ltd. (, sometimes shortened to SEC and stylized as SΛMSUNG) is a South Korean multinational corporation, multinational electronics corporation headquartered in Yeongtong-gu, Suwon, South Korea. It is the pinnacle of ...

began production of a 10nm process. TSMC began production of a 7 nm

In semiconductor manufacturing, the International Technology Roadmap for Semiconductors defines the 7 nm process as the MOSFET technology node following the 10 nm node. It is based on FinFET (fin field-effect transistor) technology, a ...

process in 2017, and Samsung began production of a 5 nm

In semiconductor manufacturing, the International Roadmap for Devices and Systems defines the 5 nm process as the MOSFET technology node following the 7 nm node. In 2020, Samsung and TSMC entered volume production of 5 nm chips, ...

process in 2018. In 2019, Samsung announced plans for the commercial production of a 3nm GAAFET process by 2021.

Commercial production of nanoelectronic FinFET semiconductor memory

Semiconductor memory is a digital electronic semiconductor device used for digital data storage, such as computer memory. It typically refers to devices in which data is stored within metal–oxide–semiconductor (MOS) memory cells on a sili ...

began in the 2010s. In 2013, SK Hynix began mass-production of 16nm NAND flash

Flash memory is an Integrated circuit, electronic Non-volatile memory, non-volatile computer memory storage medium that can be electrically erased and reprogrammed. The two main types of flash memory, NOR flash and NAND flash, are named for t ...

memory, and Samsung Electronics began production of 10nm multi-level cell

In electronics, a multi-level cell (MLC) is a memory cell capable of storing more than a single bit of information, compared to a single-level cell (SLC), which can store only one bit per memory cell. A memory cell typically consists of a single ...

(MLC) NAND flash memory. In 2017, TSMC began production of SRAM memory using a 7 nm process.

See also

* Transistor countReferences

{{Electronic components Transistor types Field-effect transistors MOSFETs Semiconductor devices Indonesian inventions Japanese inventions Taiwanese inventionsExternal links

"The Silicon Age: Trends in Semiconductor Devices Industry

, 2022