|

Scratchpad Memory

Scratchpad memory (SPM), also known as scratchpad, scratchpad RAM or local store in computer terminology, is an internal memory, usually high-speed, used for temporary storage of calculations, data, and other work in progress. In reference to a microprocessor (or CPU), scratchpad refers to a special high-speed memory used to hold small items of data for rapid retrieval. It is similar to the usage and size of a scratchpad in life: a pad of paper for preliminary notes or sketches or writings, etc. When the scratchpad is a hidden portion of the main memory then it is sometimes referred to as ''bump storage''. In some systems it can be considered similar to the L1 cache in that it is the next closest memory to the ALU after the processor registers, with explicit instructions to move data to and from main memory, often using DMA-based data transfer. In contrast to a system that uses caches, a system with scratchpads is a system with non-uniform memory access (NUMA) latencies, be ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Computer

A computer is a machine that can be Computer programming, programmed to automatically Execution (computing), carry out sequences of arithmetic or logical operations (''computation''). Modern digital electronic computers can perform generic sets of operations known as Computer program, ''programs'', which enable computers to perform a wide range of tasks. The term computer system may refer to a nominally complete computer that includes the Computer hardware, hardware, operating system, software, and peripheral equipment needed and used for full operation; or to a group of computers that are linked and function together, such as a computer network or computer cluster. A broad range of Programmable logic controller, industrial and Consumer electronics, consumer products use computers as control systems, including simple special-purpose devices like microwave ovens and remote controls, and factory devices like industrial robots. Computers are at the core of general-purpose devices ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

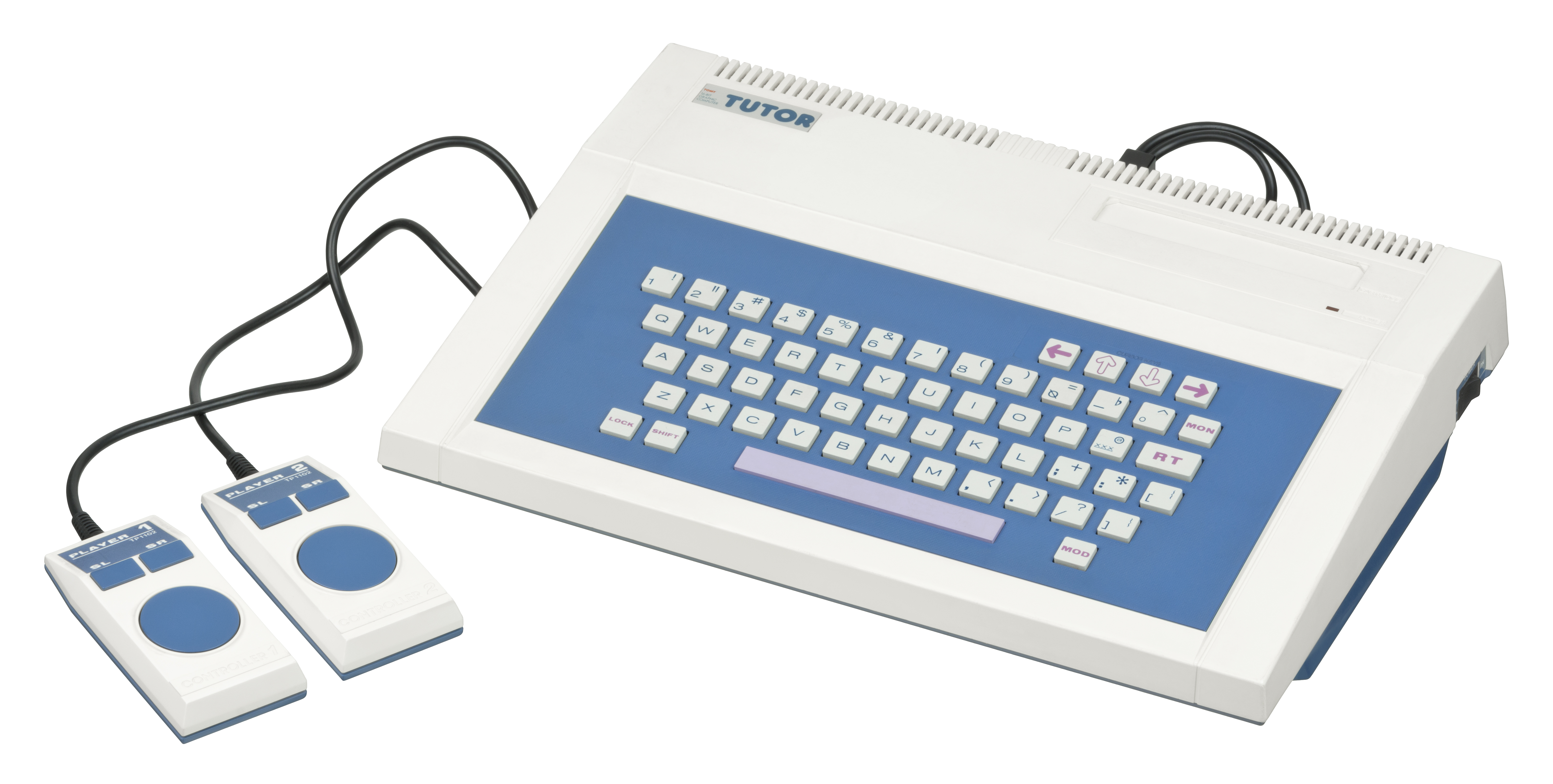

Texas Instruments TMS9900

The TMS9900 was one of the first commercially available single-chip 16-bit microprocessors. Introduced in June 1976, it implemented Texas Instruments's TI-990 minicomputer architecture in a single-chip format, and was initially used for low-end models of that lineup. Its 64-pin dual in-line package, DIP format made it more expensive to implement in smaller machines than the more common 40-pin format, and it saw relatively few design wins outside TI's own use. Among those uses was their TI-99/4A, TI-99/4 and TI-99/4A home computers, which ultimately sold about 2.8 million units. By the mid-1980s, the microcomputer field was moving to 16-bit systems such as the Intel 8086 and newer 16/32-bit designs such as the Motorola 68000. With no obvious future for the chip, TI's Semiconductor division turned its attention to special-purpose 32-bit processors: the Texas Instruments TMS320, introduced in 1983, and the TMS34010, Texas Instruments TMS340 graphics processor. The 9900 architect ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

GeForce 8800

The GeForce 8 series is the eighth generation of Nvidia's GeForce line of graphics processing units. The third major GPU architecture developed by Nvidia, Tesla represents the company's first unified shader architecture.Q3 2007 NVIDIA Corporation Earnings Conference NVIDIA.com. November 9, 2006. Overview All GeForce 8 Series products are based on Tesla. As with many GPUs, it is important to note that the larger numbers these cards carry does not guarantee superior performance over previous generation cards with a lower number. For example, the GeFo ...[...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Vertex Transformation

In linear algebra, linear transformations can be represented by matrices. If T is a linear transformation mapping \mathbb^n to \mathbb^m and \mathbf x is a column vector with n entries, then there exists an m \times n matrix A, called the transformation matrix of T, such that: T( \mathbf x ) = A \mathbf x Note that A has m rows and n columns, whereas the transformation T is from \mathbb^n to \mathbb^m. There are alternative expressions of transformation matrices involving row vectors that are preferred by some authors. Uses Matrices allow arbitrary linear transformations to be displayed in a consistent format, suitable for computation. This also allows transformations to be composed easily (by multiplying their matrices). Linear transformations are not the only ones that can be represented by matrices. Some transformations that are non-linear on an n-dimensional Euclidean space R''n'' can be represented as linear transformations on the ''n''+1-dimensional space R''n''+1. Thes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Digital Signal Processor

A digital signal processor (DSP) is a specialized microprocessor chip, with its architecture optimized for the operational needs of digital signal processing. DSPs are fabricated on metal–oxide–semiconductor (MOS) integrated circuit chips. They are widely used in audio signal processing, telecommunications, digital image processing, radar, sonar and speech recognition systems, and in common consumer electronic devices such as mobile phones, disk drives and high-definition television (HDTV) products. The goal of a DSP is usually to measure, filter or compress continuous real-world analog signals. Most general-purpose microprocessors can also execute digital signal processing algorithms successfully, but may not be able to keep up with such processing continuously in real-time. Also, dedicated DSPs usually have better power efficiency, thus they are more suitable in portable devices such as mobile phones because of power consumption constraints. DSPs often use special m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

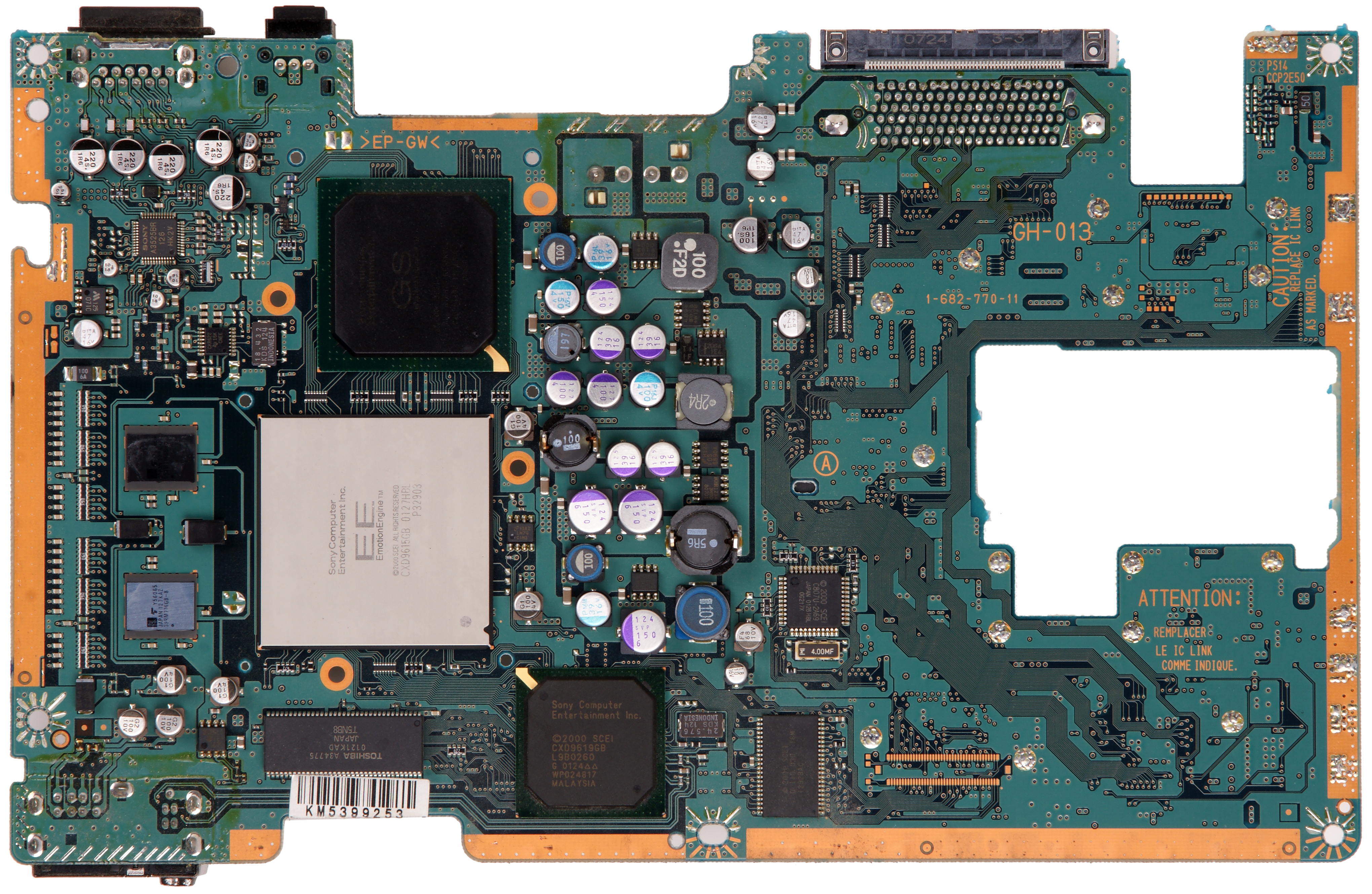

Cell (microprocessor)

The Cell Broadband Engine (Cell/B.E.) is a 64-bit multi-core processor and microarchitecture developed by Sony, Toshiba, and IBM—an alliance known as "STI". It combines a general-purpose PowerPC core, called the Power Processing Element (PPE), with multiple specialized coprocessors, known as Synergistic Processing Elements (SPEs), which accelerate tasks such as multimedia and vector processing. The architecture was developed over a four-year period beginning in March 2001, with Sony reporting a development budget of approximately . Its first major commercial application was in Sony's PlayStation 3 home video game console, released in 2006. In 2008, a modified version of the Cell processor powered IBM's Roadrunner, the first supercomputer to sustain one petaFLOPS. Other applications include high-performance computing systems from Mercury Computer Systems and specialized arcade system boards. Cell emphasizes memory coherence, power efficiency, and peak computational thro ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Kibibyte

The byte is a unit of digital information that most commonly consists of eight bits. Historically, the byte was the number of bits used to encode a single character of text in a computer and for this reason it is the smallest addressable unit of memory in many computer architectures. To disambiguate arbitrarily sized bytes from the common 8-bit definition, network protocol documents such as the Internet Protocol () refer to an 8-bit byte as an octet. Those bits in an octet are usually counted with numbering from 0 to 7 or 7 to 0 depending on the bit endianness. The size of the byte has historically been hardware-dependent and no definitive standards existed that mandated the size. Sizes from 1 to 48 bits have been used. The six-bit character code was an often-used implementation in early encoding systems, and computers using six-bit and nine-bit bytes were common in the 1960s. These systems often had memory words of 12, 18, 24, 30, 36, 48, or 60 bits, corresponding to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Emotion Engine

The Emotion Engine is a central processing unit developed and manufactured by Sony Computer Entertainment and Toshiba for use in the PlayStation 2 video game console. It was also used in early PlayStation 3 models sold in Japan and North America (Model Numbers CECHAxx & CECHBxx) to provide PlayStation 2 game support. Mass production of the Emotion Engine began in 1999 and ended in late 2012 with the discontinuation of the PlayStation 2. Description The Emotion Engine consists of eight separate "units", each performing a specific task, integrated onto the same die. These units are: a CPU core, two Vector Processing Units (VPU), a 10-channel DMA unit, a memory controller, and an Image Processing Unit (IPU). There are three interfaces: an input output interface to the I/O processor, a graphics interface (GIF) to the graphics synthesizer, and a memory interface to the system memory. The CPU core is tightly coupled to the first VPU, VPU0. Together, they are responsible for e ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Network On A Chip

A network on a chip or network-on-chip (NoC or )This article uses the convention that "NoC" is pronounced . Therefore, it uses the convention "a" for the indefinite article corresponding to NoC ("a NoC"). Other sources may pronounce it as and therefore use "an NoC". is a network-based communications subsystem on an integrated circuit ("microchip"), most typically between modules in a system on a chip ( SoC). The modules on the IC are typically semiconductor IP cores schematizing various functions of the computer system, and are designed to be modular in the sense of network science. The network on chip is a router-based packet switching network between SoC modules. NoC technology applies the theory and methods of computer networking to on-chip communication and brings notable improvements over conventional bus and crossbar communication architectures. Networks-on-chip come in many network topologies, many of which are still experimental as of 2018. In 2000s, res ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

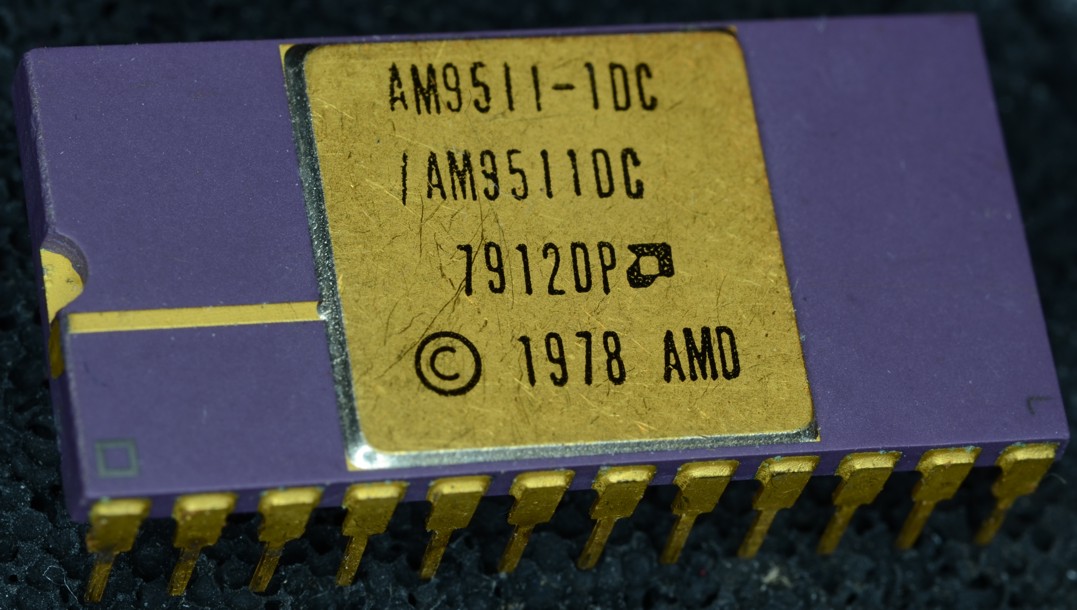

Coprocessor

A coprocessor is a computer processor used to supplement the functions of the primary processor (the CPU). Operations performed by the coprocessor may be floating-point arithmetic, graphics, signal processing, string processing, cryptography or I/O interfacing with peripheral devices. By offloading processor-intensive tasks from the main processor, coprocessors can accelerate system performance. Coprocessors allow a line of computers to be customized, so that customers who do not need the extra performance do not need to pay for it. Functionality Coprocessors vary in their degree of autonomy. Some (such as FPUs) rely on direct control via coprocessor instructions, embedded in the CPU's instruction stream. Others are independent processors in their own right, capable of working asynchronously; they are still not optimized for general-purpose code, or they are incapable of it due to a limited instruction set focused on accelerating specific tasks. It is common for these to b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Adapteva

Zero ASIC Corporation, formerly Adapteva, Inc., is a fabless semiconductor company focusing on low power many core microprocessor design. The company was the second company to announce a design with 1,000 specialized processing cores on a single integrated circuit. Adapteva was founded in 2008 with the goal of bringing a ten times advancement in floating-point performance per watt for the mobile device market. Products are based on its Epiphany multi-core multiple instruction, multiple data (MIMD) architecture and its Parallella Kickstarter project promoting "a supercomputer for everyone" in September 2012. The company name is a combination of "adapt" and the Hebrew word "Teva" meaning nature. History Adapteva was founded in March 2008, by Andreas Olofsson. The company was founded with the goal of bringing a 10× advancement in floating-point processing energy efficiency for the mobile device market. In May 2009, Olofsson had a prototype of a new type of massively parallel m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

R3000

The R3000 is a 32-bit RISC microprocessor chipset developed by MIPS Computer Systems that implemented the MIPS I instruction set architecture (ISA). Introduced in June 1988, it was the second MIPS implementation, succeeding the R2000 microprocessor, R2000 as the flagship MIPS microprocessor. It operated at 20, 25 and 33.33 MHz. The MIPS 1 instruction set is small compared to those of the contemporary 80x86 and 680x0 architectures, encoding only more commonly used operations and supporting few addressing modes. Combined with its fixed instruction length and only three different types of instruction formats, this simplified instruction decoding and processing. It employed a 5-stage instruction pipeline, enabling execution at a rate approaching one instruction per cycle, unusual for its time. This MIPS generation supports up to four co-processors. In addition to the CPU core, the R3000 microprocessor includes a Control Processor (CP), which contains a Translation Lookaside Buffe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |