|

Semiconductor Manufacturing Equipment

Semiconductor device fabrication is the process used to manufacture semiconductor devices, typically integrated circuit (IC) chips such as modern computer processors, microcontrollers, and memory chips such as NAND flash and DRAM that are present in everyday electrical and electronic devices. It is a multiple-step sequence of photolithographic and chemical processing steps (such as surface passivation, thermal oxidation, planar diffusion and junction isolation) during which electronic circuits are gradually created on a wafer made of pure semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications. The entire manufacturing process takes time, from start to packaged chips ready for shipment, at least six to eight weeks (tape-out only, not including the circuit design) and is performed in highly specialized semiconductor fabrication plants, also called foundries or fabs. All fabrication takes place in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Clean Room

A cleanroom or clean room is an engineered space, which maintains a very low concentration of airborne particulates. It is well isolated, well-controlled from contamination, and actively cleansed. Such rooms are commonly needed for scientific research, and in industrial production for all nanoscale processes, such as semiconductor manufacturing. A cleanroom is designed to keep everything from dust, to airborne organisms, or vaporised particles, away from it, and so from whatever material is being handled inside it. The other way around, a cleanroom can also help keep materials escaping from it. This is often the primary aim in hazardous biology and nuclear work, in pharmaceutics and in virology. Cleanrooms typically come with a cleanliness level quantified by the number of particles per cubic meter at a predetermined molecule measure. The ambient outdoor air in a typical urban area contains 35,000,000 particles for each cubic meter in the size range 0.5 μm and bigger, eq ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Semiconductor Fabrication Plant

In the microelectronics industry, a semiconductor fabrication plant (commonly called a fab; sometimes foundry) is a factory where devices such as integrated circuits are manufactured. Fabs require many expensive devices to function. Estimates put the cost of building a new fab over one billion U.S. dollars with values as high as $3–4 billion not being uncommon. TSMC invested $9.3 billion in its ''Fab15'' 300 mm wafer manufacturing facility in Taiwan. The same company estimations suggest that their future fab might cost $20 billion. A foundry model emerged in the 1990s: Foundries that produced their own designs were known as integrated device manufacturers (IDMs). Companies that farmed out manufacturing of their designs to foundries were termed fabless semiconductor companies. Those foundries, which did not create their own designs, were called pure-play semiconductor foundries. The central part of a fab is the clean room, an area where the environment is controlled to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FinFET

A fin field-effect transistor (FinFET) is a multigate device, a MOSFET (metal-oxide-semiconductor field-effect transistor) built on a substrate where the gate is placed on two, three, or four sides of the channel or wrapped around the channel, forming a double or even multi gate structure. These devices have been given the generic name "FinFETs" because the source/drain region forms fins on the silicon surface. The FinFET devices have significantly faster switching times and higher current density than planar CMOS (complementary metal-oxide-semiconductor) technology. FinFET is a type of non-planar transistor, or "3D" transistor. It is the basis for modern nanoelectronic semiconductor device fabrication. Microchips utilizing FinFET gates first became commercialized in the first half of the 2010s, and became the dominant gate design at 14 nm, 10 nm and 7 nm process nodes. It is common for a single FinFET transistor to contain several fins, arranged side by side and all covered ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

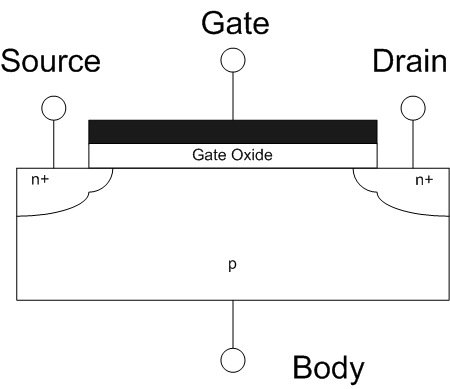

Gate (transistor)

The field-effect transistor (FET) is a type of transistor that uses an electric field to control the flow of current in a semiconductor. FETs (JFETs or MOSFETs) are devices with three terminals: ''source'', ''gate'', and ''drain''. FETs control the flow of current by the application of a voltage to the gate, which in turn alters the conductivity between the drain and source. FETs are also known as unipolar transistors since they involve single-carrier-type operation. That is, FETs use either electrons (n-channel) or holes (p-channel) as charge carriers in their operation, but not both. Many different types of field effect transistors exist. Field effect transistors generally display very high input impedance at low frequencies. The most widely used field-effect transistor is the MOSFET (metal-oxide-semiconductor field-effect transistor). History The concept of a field-effect transistor (FET) was first patented by Austro-Hungarian physicist Julius Edgar Lilienfeld in 1925 a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

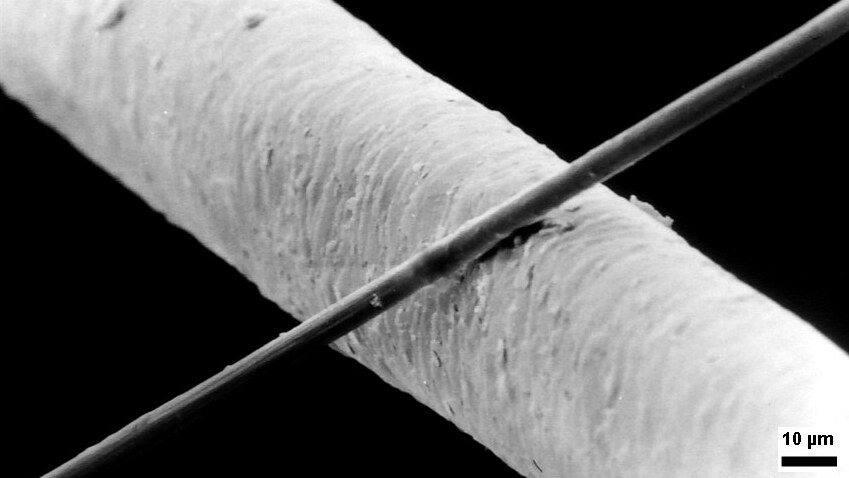

Micrometre

The micrometre ( international spelling as used by the International Bureau of Weights and Measures; SI symbol: μm) or micrometer (American spelling), also commonly known as a micron, is a unit of length in the International System of Units (SI) equalling (SI standard prefix "micro-" = ); that is, one millionth of a metre (or one thousandth of a millimetre, , or about ). The nearest smaller common SI unit is the nanometre, equivalent to one thousandth of a micrometre, one millionth of a millimetre or one billionth of a metre (). The micrometre is a common unit of measurement for wavelengths of infrared radiation as well as sizes of biological cells and bacteria, and for grading wool by the diameter of the fibres. The width of a single human hair ranges from approximately 20 to . The longest human chromosome, chromosome 1, is approximately in length. Examples Between 1 μm and 10 μm: * 1–10 μm – length of a typical bacterium * 3–8 μm – width of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nanometers

330px, Different lengths as in respect to the molecular scale. The nanometre (international spelling as used by the International Bureau of Weights and Measures; SI symbol: nm) or nanometer (American and British English spelling differences#-re, -er, American spelling) is a units of measurement, unit of length in the International System of Units (SI), equal to one billionth (short scale) of a metre () and to 1000 picometres. One nanometre can be expressed in scientific notation as , and as metres. History The nanometre was formerly known as the millimicrometre – or, more commonly, the millimicron for short – since it is of a micron (micrometre), and was often denoted by the symbol mμ or (more rarely and confusingly, since it logically should refer to a ''millionth'' of a micron) as μμ. Etymology The name combines the SI prefix ''nano-'' (from the Ancient Greek , ', "dwarf") with the parent unit name ''metre'' (from Greek , ', "unit of measurement"). ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Semiconductor Industry Association

The Semiconductor Industry Association (SIA) is a trade association and lobbying group founded in 1977 that represents the United States semiconductor industry. It is located in Washington, D.C. One of the main achievements of the SIA was the creation of the first National Technology Roadmap for Semiconductors, in the early 1990s. About The Semiconductor Industry Association (SIA) positions itself as the voice of the U.S. semiconductor industry. This is one of America's top export industries and a driver of American economic strength, national security and global competitiveness. Founded in 1977 by five microelectronics pioneers Wilfred Corrigan of Fairchild Semiconductor, Robert Noyce of Intel Corporation, Jerry Sanders of Advanced Micro Devices, Charles Sporck of National Semiconductor Corporation and John Welty of Motorola, SIA unites companies that account for 80 percent of America’s semiconductor production. Through this coalition, SIA seeks to strengthen US leaders ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

90 Nm Process

The 90 nm process refers to the level of MOSFET (CMOS) fabrication process technology that was commercialized by the 2003–2005 timeframe, by leading semiconductor companies like Toshiba, Sony, Samsung, IBM, Intel, Fujitsu, TSMC, Elpida, AMD, Infineon, Texas Instruments and Micron Technology. The origin of the 90 nm value is historical, it reflects a trend of 70% scaling every 2–3 years. The naming is formally determined by the International Technology Roadmap for Semiconductors (ITRS). The 193 nm wavelength was introduced by many (but not all) companies for lithography of critical layers mainly during the 90 nm node. Yield issues associated with this transition (due to the use of new photoresists) were reflected in the high costs associated with this transition. Even more significantly, the 300 mm wafer size became mainstream at the 90 nm node. The previous wafer size was 200 mm diameter. History A 90nm silicon MOSFET was fabricated ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CHMOS

CHMOS refers to one of a series of Intel CMOS processes developed from their HMOS process. (H stands for high-density). It was first developed in 1981. CHMOS was used in the Intel 80C51BH, a new version of their standard MCS-51 microcontroller. The chip was also used in later versions of Intel 8086, and the 80C88, which were fully static version of the Intel 8088. The Intel 80386 was made in 1.5 µm CHMOS III, and later in 1.0 µm CHMOS IV. CHMOS III used 1.5 micron lithography, p-well processing, n-well processing, and two layers of metal. CHMOS III-E used for the 12.5 MHz Intel 80C186 microprocessor.Ormsby, John, Editor, "New Product Focus: Components: It's Under Control With The 80C186", Intel Corporation, Microcomputer Solutions, November/December 1987, page 13 CHMOS IV (H stands for High Speed) used 1.0 µm lithography. Many versions of the Intel 80486 The Intel 486, officially named i486 and also known as 80486, is a microprocessor. It is a higher-p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

HMOS

In integrated circuits, depletion-load NMOS is a form of digital logic family that uses only a single power supply voltage, unlike earlier NMOS (n-type metal-oxide semiconductor) logic families that needed more than one different power supply voltage. Although manufacturing these integrated circuits required additional processing steps, improved switching speed and the elimination of the extra power supply made this logic family the preferred choice for many microprocessors and other logic elements. Depletion-mode n-type MOSFETs as load transistors allow single voltage operation and achieve greater speed than possible with pure enhancement-load devices. This is partly because the depletion-mode MOSFETs can be a better current source approximation than the simpler enhancement-mode transistor can, especially when no extra voltage is available (one of the reasons early PMOS and NMOS chips demanded several voltages). The inclusion of depletion-mode NMOS transistors in the manuf ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Die Shrink

The term die shrink (sometimes optical shrink or process shrink) refers to the scaling of metal-oxide-semiconductor (MOS) devices. The act of shrinking a die is to create a somewhat identical circuit using a more advanced fabrication process, usually involving an advance of lithographic nodes. This reduces overall costs for a chip company, as the absence of major architectural changes to the processor lowers research and development costs while at the same time allowing more processor dies to be manufactured on the same piece of silicon wafer, resulting in less cost per product sold. Details Die shrinks are the key to improving price/performance at semiconductor companies such as Samsung, Intel, TSMC, and SK Hynix, and fabless manufacturers such as AMD (including the former ATI), NVIDIA and MediaTek. Examples in the 2000s include the downscaling of the PlayStation 2's Emotion Engine processor from Sony and Toshiba (from 180 nm CMOS in 2000 to 90 nm CMOS in 2003), t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FOUP

FOUP is an acronym for Front Opening Unified Pod or Front Opening Universal Pod. It is a specialised plastic enclosure designed to hold silicon wafers securely and safely in a controlled environment, and to allow the wafers to be transferred between machines for processing or measurement. FOUPs began to appear along with the first 300mm wafer processing tools in the mid 1990s. The size of the wafers and their comparative lack of rigidity meant that SMIF was not a viable technology. FOUPs were designed with the constraints of 300mm in mind, with the removable cassette being replaced by fins in the FOUP which hold the wafers in place, and the bottom opening door being replaced by a front opening door to allow robot handling mechanisms to access the wafers directly from the FOUP. The weight of a fully loaded 25 wafer FOUP at around 9 kilograms means that automated material handling systems are essential for all but the smallest of fabrication plants. Pitch for 300mm Foup is 10mm. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)