|

Process Design Kit

A process design kit (PDK) is a set of files used within the semiconductor industry to model a fabrication process for the design tools used to design an integrated circuit. The PDK is created by the foundry defining a certain technology variation for their processes. It is then passed to their customers to use in the design process. The customers may enhance the PDK, tailoring it to their specific design styles and markets. The designers use the PDK to design, simulate, draw and verify the design before handing the design back to the foundry to produce chips. The data in the PDK is specific to the foundry's process variation and is chosen early in the design process, influenced by the market requirements for the chip. An accurate PDK will increase the chances of first-pass successful silicon. Description Different tools in the design flow have different input formats for the PDK data. The PDK engineers have to decide which tools they will support in the design flows and create the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Semiconductor Industry

The semiconductor industry is the aggregate of companies engaged in the design and fabrication of semiconductors and semiconductor devices, such as transistors and integrated circuits. It formed around 1960, once the fabrication of semiconductor devices became a viable business. The industry's annual semiconductor sales revenue has since grown to over , as of 2018. The semiconductor industry is in turn the driving force behind the wider electronics industry, with annual power electronics sales of £135billion () as of 2011, annual consumer electronics sales expected to reach by 2020, tech industry sales expected to reach in 2019, and e-commerce with over in 2017. In 2019, 32.4% of the semiconductor market segment was for networks and communications devices. In 2021, the sales of semiconductors reached a record $555.9 billion, up 26.2 percent with sales in China reaching $192.5 billion, according to the Semiconductor Industry Association. A record 1.15 trillion semiconduct ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PCell

PCell stands for parameterized cell, a concept used widely in the automated design of analog integrated circuits. A PCell represents a part or a component of the circuit whose structure is dependent on one or more parameters. Hence, it is a cell which is automatically generated by electronic design automation (EDA) software based on the values of these parameters. For example, one can create a transistor PCell and then use different instances of the same with different user defined lengths and widths. Vendors of EDA software sometimes use different names for the concept of parameterized cells, e.g. ''T-Cell'' and ''Magic Cell''. Application In electronic circuit designs, cells are basic units of functionality. A given cell may be placed or instantiated many times. A P-Cell is more flexible than a non-parameterized cell because different instances may have different parameter values and, therefore, different structures. For example, rather than having many different cell def ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Design Rule Checking

In electronic design automation, a design rule is a geometric constraint imposed on circuit board, semiconductor device, and integrated circuit (IC) designers to ensure their designs function properly, reliably, and can be produced with acceptable yield. Design rules for production are developed by process engineers based on the capability of their processes to realize design intent. Electronic design automation is used extensively to ensure that designers do not violate design rules; a process called design rule checking (DRC). DRC is a major step during physical verification signoff on the design, which also involves LVS (layout versus schematic) checks, XOR checks, ERC ( electrical rule check), and antenna checks. The importance of design rules and DRC is greatest for ICs, which have micro- or nano-scale geometries; for advanced processes, some fabs also insist upon the use of more restricted rules to improve yield. Design rules Design rules are a series of parameters provi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Layout Versus Schematic

The Layout Versus Schematic (LVS) is the class of electronic design automation (EDA) verification software that determines whether a particular integrated circuit layout corresponds to the original schematic or circuit diagram of the design. Background A successful design rule check (DRC) ensures that the layout conforms to the rules designed/required for faultless fabrication. However, it does not guarantee if it really represents the circuit you desire to fabricate. This is where an LVS check is used. The need for such programs was recognized relatively early in the history of ICs, and programs to perform this comparison were written as early as 1975. These early programs operated mainly on the level of graph isomorphism, checking whether the schematic and layout were indeed identical. With the advent of digital logic, this was too restrictive, since exactly the same function can be implemented in many different (and non-isomorphic) ways. Therefore, LVS has been augmented by ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Physical Verification

Physical verification is a process whereby an integrated circuit layout (IC layout) design is verified via EDA software tools to ensure correct electrical and logical functionality and manufacturability. Verification involves design rule check (DRC), layout versus schematic (LVS), XOR (exclusive OR), antenna checks and electrical rule check (ERC).A. Kahng, et al.: ''VLSI Physical Design: From Graph Partitioning to Timing Closure'', , , p. 10. Design Rule Check (DRC) DRC verifies that the layout meets all technology-imposed constraints. DRC also verifies layer density for chemical-mechanical polishing (CMP). Layout Versus Schematic (LVS) LVS verifies the functionality of the design. From the layout, a netlist is derived and compared with the original netlist produced from logic synthesis or circuit design. XOR check This check is typically run after a metal spin, where the original and modified database are compared. This is done to confirm that the desired modifications have ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Library Exchange Format

Library Exchange Format (LEF) is a specification for representing the physical layout of an integrated circuit in an ASCII format. It includes design rules and abstract information about the standard cells. LEF only has the basic information required at that level to serve the purpose of the concerned CAD tool. It helps in saving valuable resources by providing only an abstract view and thus consuming less memory overhead. LEF is used in conjunction with Design Exchange Format (DEF) to represent the complete physical layout of an integrated circuit while it is being designed. LEF originated by Tangent for their Place and Route (P&R) tools, which were bought by Cadence Design Systems Cadence Design Systems, Inc. (stylized as cādence), headquartered in San Jose, California, is an American multinational corporation, multinational computational software company, founded in 1988 by the merger of SDA Systems and ECAD, Inc. The co ....Smith, Michael J. S., Application-Specific Inte ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

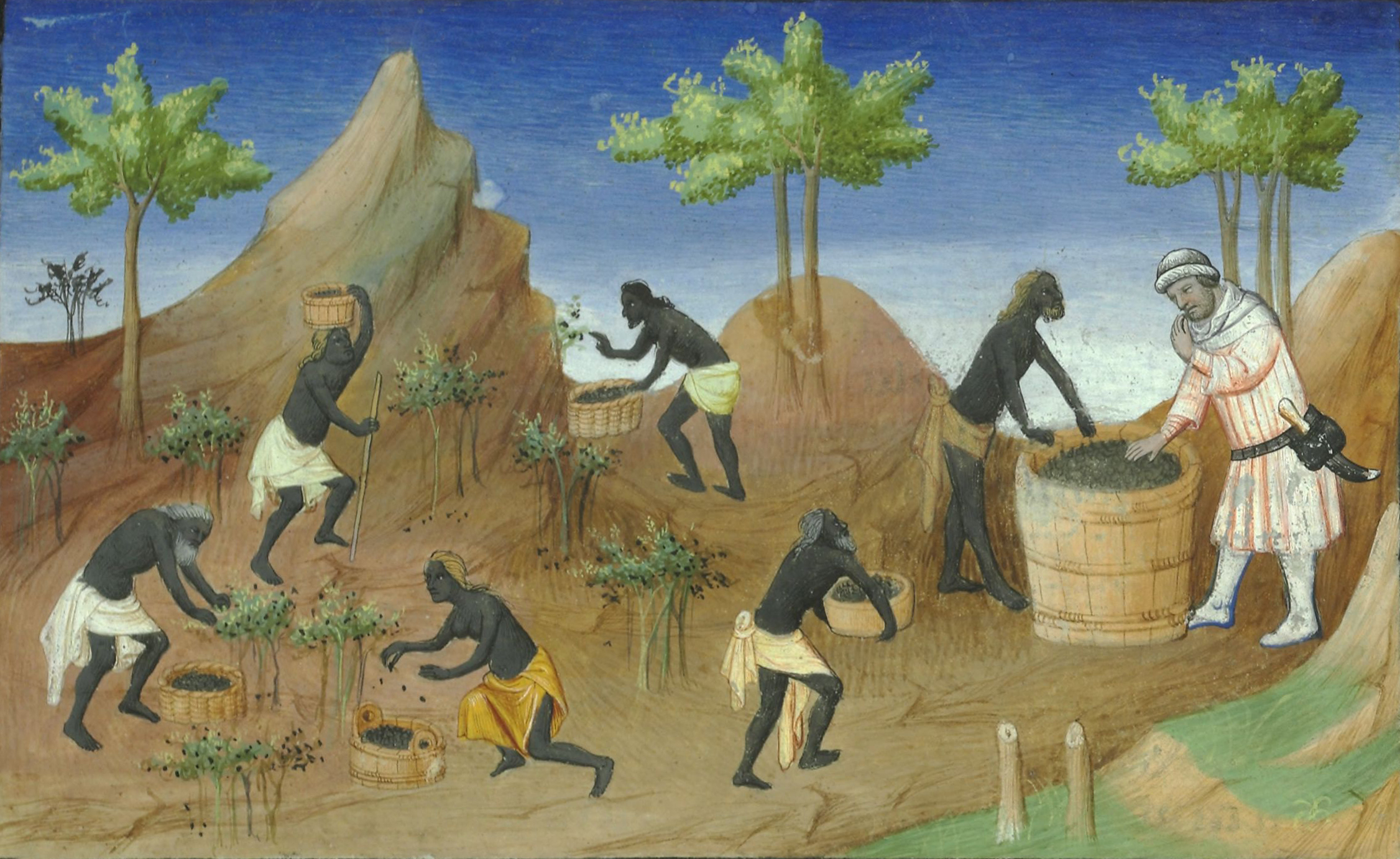

SPICE

A spice is a seed, fruit, root, bark, or other plant substance primarily used for flavoring or coloring food. Spices are distinguished from herbs, which are the leaves, flowers, or stems of plants used for flavoring or as a garnish. Spices are sometimes used in medicine, religious rituals, cosmetics or perfume production. For example, vanilla is commonly used as an ingredient in fragrance manufacturing. A spice may be available in several forms: fresh, whole dried, or pre-ground dried. Generally, spices are dried. Spices may be ground into a powder for convenience. A whole dried spice has the longest shelf life, so it can be purchased and stored in larger amounts, making it cheaper on a per-serving basis. A fresh spice, such as ginger, is usually more flavorful than its dried form, but fresh spices are more expensive and have a much shorter shelf life. Some spices are not always available either fresh or whole, for example turmeric, and often must be purchased in ground form. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDSII

GDSII stream format (GDSII), is a binary database file format which is the de facto industry standard for Electronic Design Automation data exchange of integrated circuit or IC layout artwork. It is a binary file format representing planar geometric shapes, text labels, and other information about the layout in hierarchical form. The data can be used to reconstruct all or part of the artwork to be used in sharing layouts, transferring artwork between different tools, or creating photomasks. History GDS = Graphic Design System (see DS78 Initially, GDSII was designed as a stream format used to control integrated circuit photomask plotting. Despite its limited set of features and low data density, it became the industry conventional stream format for transfer of IC layout data between design tools of different vendors, all of which operated with proprietary data formats. It was originally developed by Calma for its layout design system, "Graphic Design System" ("GDS") and "GDSI ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |