|

Torrenza

Torrenza was an initiative announced by Advanced Micro Devices (AMD) in 2006 to improve support for the integration of specialized coprocessors in systems based on AMD Opteron microprocessors. Torrenza does not refer to a specific product or specific technology, though the primary focus is on the integration of coprocessor devices directly connected to the Opteron processors' HyperTransport links, and other co-processors connected via PCI Express. The initiative's stated goals include improving technical and technology support for third-party developers of coprocessing devices, reducing the cost of implementing HyperTransport interfaces on these devices, and improving the performance of the integrated system. It can be argued, that the original idea behind Torrenza was successfully implemented in form of Heterogeneous System Architecture by AMD and the other members of the HSA Foundation. Goals AMD expected tightly-integrated coprocessor technology to be a proving ground for develo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tarari (company)

Tarari is a company that spun out of Intel in 200It has created a range of re-programmable silicon based on Xilinxbr>Virtex-4 Field-programmable gate array, FPGA (Field Programmable Gate Array) and ASICsbr>that offload and accelerate really complex algorithms such as XML Parsing, scanning for Computer viruses, email spam and intruders in Intrusion-prevention systems and Unified threat management appliances. As well as inspecting content its Content Processors can also transform content and they are used for XML transformation XSLT, compression, encryption as well as HD Video encoding for WMV and VC-1 formats. In June 2006, Tarari announced that its next generation chips that will support the AMD Torrenzabr>initiative - and it will incorporate HyperTransportbr>interfaces. HyperTransport based-systems offer a dramatically reduced latency and increased throughput. This is because a HyperTransport connected system allows a co-processor to have direct access to the system's HyperT ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hypertransport

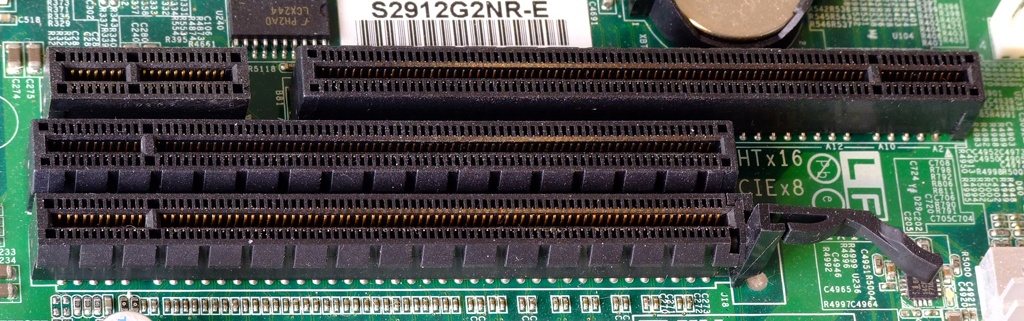

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/parallel high-bandwidth, low- latency point-to-point link that was introduced on April 2, 2001. The HyperTransport Consortium is in charge of promoting and developing HyperTransport technology. HyperTransport is best known as the system bus architecture of AMD central processing units (CPUs) from Athlon 64 through AMD FX and the associated motherboard chipsets. HyperTransport has also been used by IBM and Apple for the Power Mac G5 machines, as well as a number of modern MIPS systems. The current specification HTX 3.1 remained competitive for 2014 high-speed (2666 and 3200 MT/s or about 10.4 GB/s and 12.8 GB/s) DDR4 RAM and slower (around 1 GB/similar to high end Solid-state drive#Standard card form factors, PCIe SSDs ULLtraDIMM flash RAM) technology—a wider range of RAM speeds on a common CPU bus ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD FireStream

AMD FireStream was AMD's brand name for their Radeon-based product line targeting stream processing and/or GPGPU in supercomputers. Originally developed by ATI Technologies around the Radeon X1900 XTX in 2006, the product line was previously branded as both ATI FireSTREAM and AMD Stream Processor. The AMD FireStream can also be used as a floating-point co-processor for offloading CPU calculations, which is part of the Torrenza initiative. The FireStream line has been discontinued since 2012, when GPGPU workloads were entirely folded into the AMD FirePro line. Overview The FireStream line is a series of add-on expansion cards released from 2006 to 2010, based on standard Radeon GPUs but designed to serve as a general-purpose co-processor, rather than rendering and outputting 3D graphics. Like the FireGL/FirePro line, they were given more memory and memory bandwidth, but the FireStream cards do not necessarily have video output ports. All support 32-bit single-precision floating ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Front Side Bus

A front-side bus (FSB) is a computer communication interface (bus) that was often used in Intel-chip-based computers during the 1990s and 2000s. The EV6 bus served the same function for competing AMD CPUs. Both typically carry data between the central processing unit (CPU) and a memory controller hub, known as the northbridge. Depending on the implementation, some computers may also have a back-side bus that connects the CPU to the cache. This bus and the cache connected to it are faster than accessing the system memory (or RAM) via the front-side bus. The speed of the front side bus is often used as an important measure of the performance of a computer. The original front-side bus architecture has been replaced by HyperTransport, Intel QuickPath Interconnect or Direct Media Interface in modern volume CPUs. History The term came into use by Intel Corporation about the time the Pentium Pro and Pentium II products were announced, in the 1990s. "Front side" refers to the extern ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/parallel high-bandwidth, low- latency point-to-point link that was introduced on April 2, 2001. The HyperTransport Consortium is in charge of promoting and developing HyperTransport technology. HyperTransport is best known as the system bus architecture of AMD central processing units (CPUs) from Athlon 64 through AMD FX and the associated motherboard chipsets. HyperTransport has also been used by IBM and Apple for the Power Mac G5 machines, as well as a number of modern MIPS systems. The current specification HTX 3.1 remained competitive for 2014 high-speed (2666 and 3200 MT/s or about 10.4 GB/s and 12.8 GB/s) DDR4 RAM and slower (around 1 GB/similar to high end Solid-state drive#Standard card form factors, PCIe SSDs ULLtraDIMM flash RAM) technology—a wider range of RAM speeds on a common CPU bus ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Coprocessor

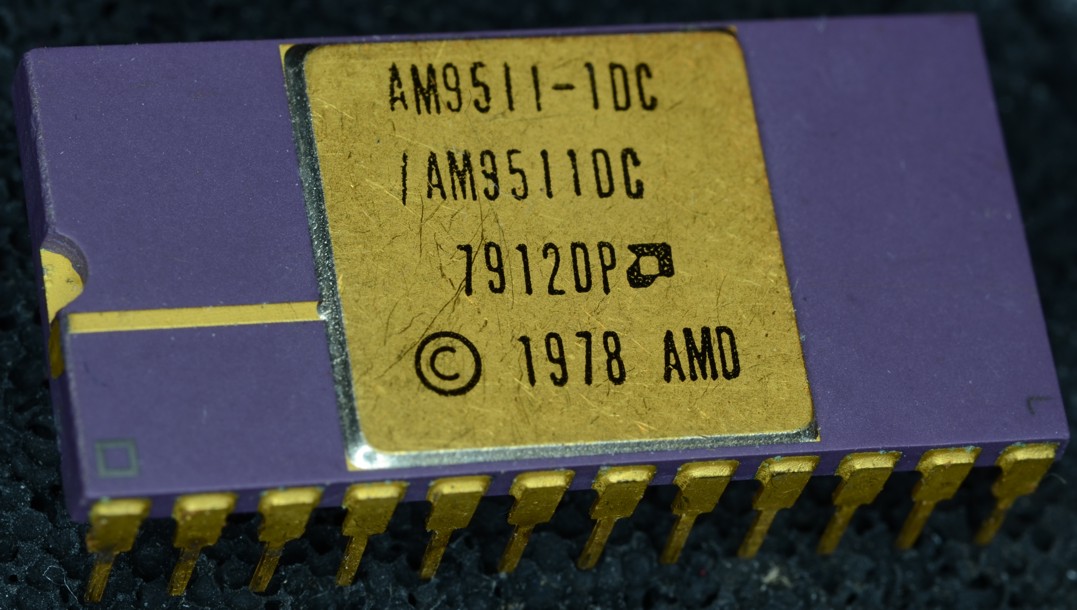

A coprocessor is a computer processor used to supplement the functions of the primary processor (the CPU). Operations performed by the coprocessor may be floating-point arithmetic, graphics, signal processing, string processing, cryptography or I/O interfacing with peripheral devices. By offloading processor-intensive tasks from the main processor, coprocessors can accelerate system performance. Coprocessors allow a line of computers to be customized, so that customers who do not need the extra performance do not need to pay for it. Functionality Coprocessors vary in their degree of autonomy. Some (such as FPUs) rely on direct control via coprocessor instructions, embedded in the CPU's instruction stream. Others are independent processors in their own right, capable of working asynchronously; they are still not optimized for general-purpose code, or they are incapable of it due to a limited instruction set focused on accelerating specific tasks. It is common for these t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Socket 940

Socket 940 is a 940-pin socket for 64-bit AMD Opteron server processors and AMD Athlon 64 FX consumer processors. This socket is entirely square in shape and pins are arranged in a grid with the exception of four key pins used to align the processor and the corners. AMD's Opteron and the older AMD Athlon 64 FX (FX-51) use Socket 940. Technical specifications Microprocessors designed for this socket were intended to be used in a server platform, and as such provide additional features to provide additional robustness. One such feature is the acceptance of only registered memory. While the more recent 940-pin socket AM2 is visually similar to this one, the two are electrically incompatible due to the integrated memory controller. Socket 940 CPUs integrate a DDR controller, whereas AM2 models use a DDR2 controller. See also *List of AMD microprocessors This article gives a list of AMD microprocessors, sorted by generation and release year. If applicable and openly known, the desi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of AMD Opteron Microprocessors

Opteron is the name of a central processing unit (CPU) family within the AMD64 line. Designed by Advanced Micro Devices (AMD) for the server market, Opteron competed with Intel's Xeon. The Opteron family is succeeded by the Zen-based Epyc, and Ryzen Threadripper and Threadripper Pro series. For Socket 940 and Socket 939 Opterons, each chip has a three-digit model number, in the form ''Opteron XYY''. For Socket F and Socket AM2 Opterons, each chip has a four-digit model number, in the form ''Opteron XZYY''. For all Opterons, the first digit (the X) specifies the number of CPUs on the target machine: * 1 – has 1 processor (uniprocessor) * 2 – has 2 processors (dual processor) * 8 – has 4 or 8 processors For Socket F and Socket AM2 Opterons, the second digit (the Z) represents the processor generation. Presently, only 2 (dual-core), DDR2, 3 (quad-core) and 4 (six-core) are used. For all Opterons, the last two digits in the model number (the YY) indicate the clock rate (freque ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Petaflop

In computing, floating point operations per second (FLOPS, flops or flop/s) is a measure of computer performance, useful in fields of scientific computations that require floating-point calculations. For such cases, it is a more accurate measure than measuring instructions per second. Floating-point arithmetic Floating-point arithmetic is needed for very large or very small real numbers, or computations that require a large dynamic range. Floating-point representation is similar to scientific notation, except everything is carried out in base two, rather than base ten. The encoding scheme stores the sign, the exponent (in base two for Cray and VAX, base two or ten for IEEE floating point formats, and base 16 for IBM Floating Point Architecture) and the significand (number after the radix point). While several similar formats are in use, the most common is ANSI/IEEE Std. 754-1985. This standard defines the format for 32-bit numbers called ''single precision'', as well as ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cell Broadband Engine

Cell is a multi-core microprocessor microarchitecture that combines a general-purpose PowerPC core of modest performance with streamlined coprocessing elements which greatly accelerate multimedia and vector processing applications, as well as many other forms of dedicated computation. It was developed by Sony, Toshiba, and IBM, an alliance known as "STI". The architectural design and first implementation were carried out at the STI Design Center in Austin, Texas over a four-year period beginning March 2001 on a budget reported by Sony as approaching US$400 million. Cell is shorthand for Cell Broadband Engine Architecture, commonly abbreviated ''CBEA'' in full or ''Cell BE'' in part. The first major commercial application of Cell was in Sony's PlayStation 3 game console, released in 2006. In May 2008, the Cell-based IBM Roadrunner supercomputer became the first TOP500 LINPACK sustained 1.0 petaflops system. Mercury Computer Systems also developed designs based on the Cell. The ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Roadrunner

Roadrunner was a supercomputer built by IBM for the Los Alamos National Laboratory in New Mexico, USA. The US$100-million Roadrunner was designed for a peak performance of 1.7 petaflops. It achieved 1.026 petaflops on May 25, 2008, to become the world's first TOP500 LINPACK sustained 1.0 petaflops system. In November 2008, it reached a top performance of 1.456 petaFLOPS, retaining its top spot in the TOP500 list. It was also the fourth-most energy-efficient supercomputer in the world on the Supermicro Green500 list, with an operational rate of 444.94 megaflops per watt of power used. The hybrid Roadrunner design was then reused for several other energy efficient supercomputers. Roadrunner was decommissioned by Los Alamos on March 31, 2013. In its place, Los Alamos commissioned a supercomputer called Cielo, which was installed in 2010. Overview IBM built the computer for the U.S. Department of Energy's (DOE) National Nuclear Security Administration (NNSA). It was a hybrid desig ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

POWER7

POWER7 is a family of superscalar multi-core microprocessors based on the Power ISA 2.06 instruction set architecture released in 2010 that succeeded the POWER6 and POWER6+. POWER7 was developed by IBM at several sites including IBM's Rochester, MN; Austin, TX; Essex Junction, VT; T. J. Watson Research Center, NY; Bromont, QC and IBM Deutschland Research & Development GmbH, Böblingen, Germany laboratories. IBM announced servers based on POWER7 on 8 February 2010. History IBM won a $244 million DARPA contract in November 2006 to develop a petascale supercomputer architecture before the end of 2010 in the HPCS project. The contract also states that the architecture shall be available commercially. IBM's proposal, PERCS (Productive, Easy-to-use, Reliable Computer System), which won them the contract, is based on the POWER7 processor, AIX operating system and General Parallel File System. One feature that IBM and DARPA collaborated on is modifying the addressing and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |