|

TILE64

TILE64 is a VLIW ISA multicore processor manufactured by Tilera. It consists of a mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor. The short-pipeline, in-order, three-issue cores implement a MIPS-inspired VLIW instruction set. Each core has a register file and three functional units: two integer arithmetic logic units and a load-store unit. Each of the cores ("tile") has its own L1 and L2 caches plus an overall virtual L3 cache which is an aggregate of all the L2 caches. A core is able to run a full operating system on its own or multiple cores can be used to run a symmetrical multi-processing operating system. TILE64 has four DDR2 controllers, two 10-gigabit Ethernet interfaces, two four-lane PCIe interfaces, and a "flexible" input/output interface, which can be software-configured to handle a number of protocols. The processor is fa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tile64

TILE64 is a VLIW ISA multicore processor manufactured by Tilera. It consists of a mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor. The short-pipeline, in-order, three-issue cores implement a MIPS-inspired VLIW instruction set. Each core has a register file and three functional units: two integer arithmetic logic units and a load-store unit. Each of the cores ("tile") has its own L1 and L2 caches plus an overall virtual L3 cache which is an aggregate of all the L2 caches. A core is able to run a full operating system on its own or multiple cores can be used to run a symmetrical multi-processing operating system. TILE64 has four DDR2 controllers, two 10-gigabit Ethernet interfaces, two four-lane PCIe interfaces, and a "flexible" input/output interface, which can be software-configured to handle a number of protocols. The processor is fa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tilera

Tilera Corporation was a fabless semiconductor company focusing on manycore embedded processor design. The company shipped multiple processors, including the TILE64, TILE''Pro''64, and the TILE''Pro''36, TILE-Gx72, TILE-Gx36, TILE-Gx16 and TILE-Gx9. After a series of company acquisitions. Tilera's intellectual property was eventually acquired by Mellanox, which now ships products that descend from the original Tilera designs. History In 1990, Anant Agarwal led a team of researchers at Massachusetts Institute of Technology to develop scalable multi-processor system built out of large numbers of single chip processors. Alewife machines integrated both shared memory and user-level message passing for inter-node communications. In 1997, Agarwal proposed a follow-on project using a mesh technology to connect multiple cores. The follow-on project, named RAW, commenced in 1997, and was supported by DARPA/NSF's funding of tens of millions, resulting in the first 16-processor tiles m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multicore Processor

A multi-core processor is a microprocessor on a single integrated circuit with two or more separate processing units, called cores, each of which reads and executes program instructions. The instructions are ordinary CPU instructions (such as add, move data, and branch) but the single processor can run instructions on separate cores at the same time, increasing overall speed for programs that support multithreading or other parallel computing techniques. Manufacturers typically integrate the cores onto a single integrated circuit die (known as a chip multiprocessor or CMP) or onto multiple dies in a single chip package. The microprocessors currently used in almost all personal computers are multi-core. A multi-core processor implements multiprocessing in a single physical package. Designers may couple cores in a multi-core device tightly or loosely. For example, cores may or may not share caches, and they may implement message passing or shared-memory inter-core communicat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Manycore Processors

Manycore processors are special kinds of multi-core processors designed for a high degree of parallel processing, containing numerous simpler, independent processor cores (from a few tens of cores to thousands or more). Manycore processors are used extensively in embedded computers and high-performance computing. Contrast with multicore architecture Manycore processors are distinct from multi-core processors in being optimized from the outset for a higher degree of explicit parallelism, and for higher throughput (or lower power consumption) at the expense of latency and lower single-thread performance. The broader category of multi-core processors, by contrast, are usually designed to efficiently run ''both'' parallel ''and'' serial code, and therefore place more emphasis on high single-thread performance (e.g. devoting more silicon to out of order execution, deeper pipelines, more superscalar execution units, and larger, more general caches), and shared memory. These techniqu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Phoronix

Phoronix Test Suite (PTS) is a free and open-source benchmark software for Linux and other operating systems which is developed by Michael Larabel and Matthew Tippett. The Phoronix Test Suite has been endorsed by sites such as Linux.com, LinuxPlanet, and Softpedia. Features * Supports over 220 test profiles and over 60 test suites; * Uses an XML-based testing architecture. Tests include MEncoder, FFmpeg and lm sensors along with OpenGL games such as ''Doom 3'', ''Nexuiz'', and '' Enemy Territory: Quake Wars'', and many more. * Contains a feature called PTS Global where users are able to upload their test results and system information for sharing. Then through executing a single command, other users can compare their test results to a selected system in an easy-comparison mode; * Allows report benchmark results to the Phoronix Global online database; * Allows to compare results side-by-side; * Is extensible and new tests can be added easily * Can do anonymous usage reporting; ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Linux Kernel

The Linux kernel is a free and open-source, monolithic, modular, multitasking, Unix-like operating system kernel. It was originally authored in 1991 by Linus Torvalds for his i386-based PC, and it was soon adopted as the kernel for the GNU operating system, which was written to be a free (libre) replacement for Unix. Linux is provided under the GNU General Public License version 2 only, but it contains files under other compatible licenses. Since the late 1990s, it has been included as part of a large number of operating system distributions, many of which are commonly also called Linux. Linux is deployed on a wide variety of computing systems, such as embedded devices, mobile devices (including its use in the Android operating system), personal computers, servers, mainframes, and supercomputers. It can be tailored for specific architectures and for several usage scenarios using a family of simple commands (that is, without the need of manually editing its source code ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Anant Agarwal

Anant Agarwal is an Indian computer architecture researcher. He is a professor of Electrical Engineering and Computer Science at the Massachusetts Institute of Technology (MIT), where he led the development of Alewife, an early cache coherent multiprocessor, and also has served as director of the MIT Computer Science and Artificial Intelligence Laboratory. He is the founder and CTO of Tilera, a fabless semiconductor company focusing on scalable multicore embedded processor design. He also serves as the CEO of edX, a joint partnership between MIT and Harvard University that offers free online learning. Education Agarwal was born in Mangalore and did his schooling in St. Aloysius Mangalore. He holds a bachelor's degree (1982) in electrical engineering from Indian Institute of Technology Madras. For postgraduate study, he attended Stanford University, where he received an MS (1984) and a PhD (1987), both in electrical engineering. His PhD thesis, ''Analysis of Cache Performan ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

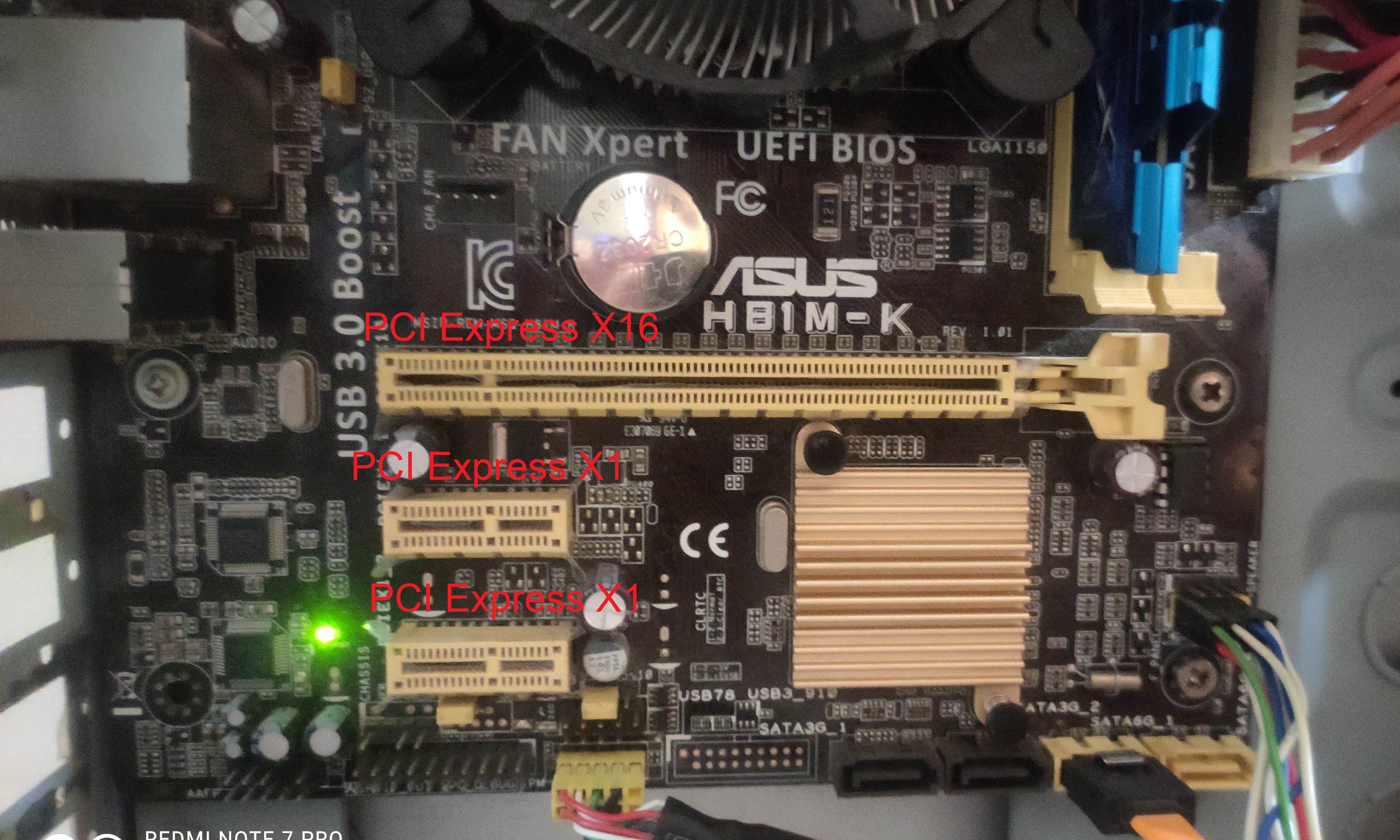

PCIe

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directions.) T ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ethernet

Ethernet () is a family of wired computer networking technologies commonly used in local area networks (LAN), metropolitan area networks (MAN) and wide area networks (WAN). It was commercially introduced in 1980 and first standardized in 1983 as IEEE 802.3. Ethernet has since been refined to support higher bit rates, a greater number of nodes, and longer link distances, but retains much backward compatibility. Over time, Ethernet has largely replaced competing wired LAN technologies such as Token Ring, FDDI and ARCNET. The original 10BASE5 Ethernet uses coaxial cable as a shared medium, while the newer Ethernet variants use twisted pair and fiber optic links in conjunction with switches. Over the course of its history, Ethernet data transfer rates have been increased from the original to the latest , with rates up to under development. The Ethernet standards include several wiring and signaling variants of the OSI physical layer. Systems communicating over Ethernet ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |