|

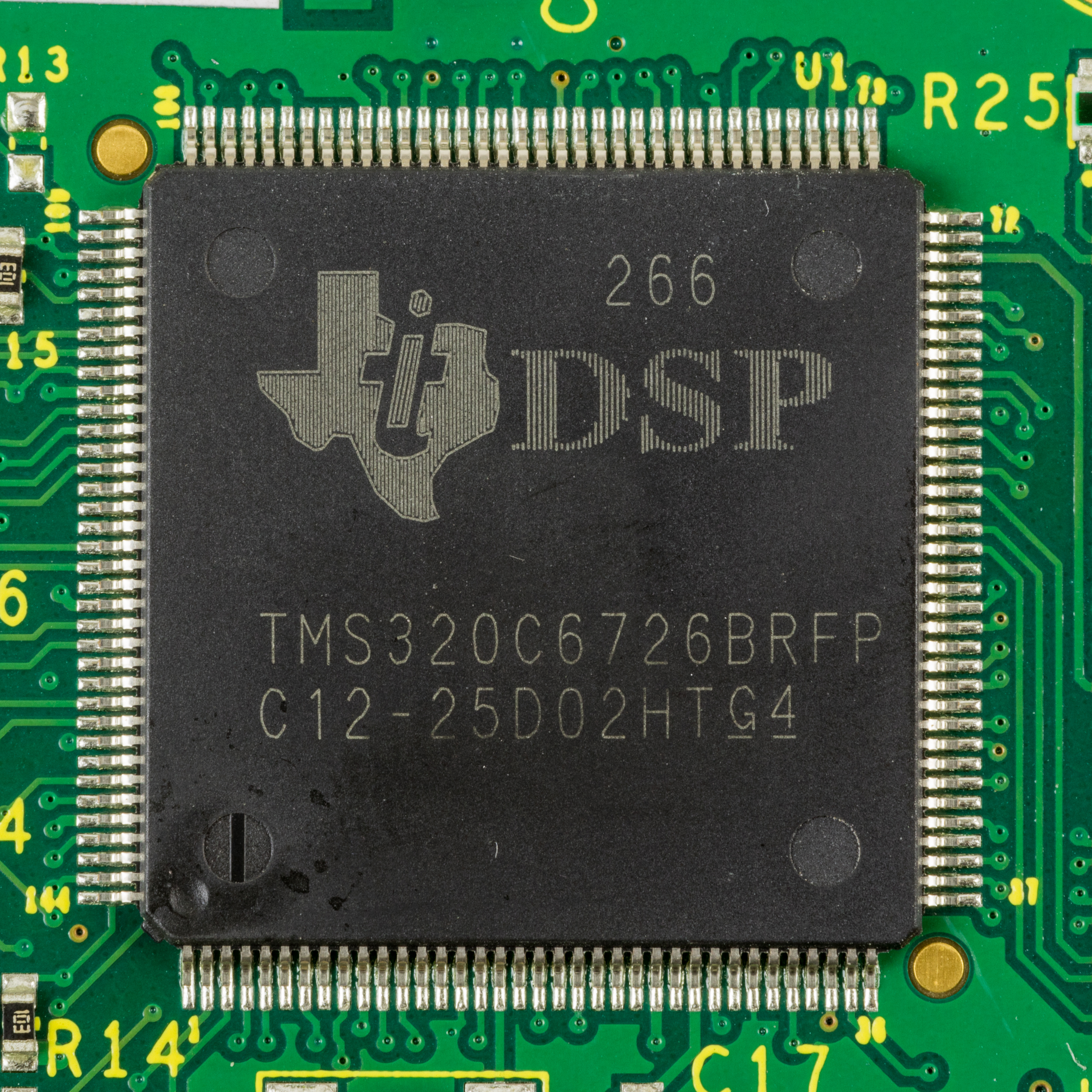

TMS320

Texas Instruments TMS320 is a blanket name for a series of digital signal processors (DSPs) from Texas Instruments. It was introduced on April 8, 1983 through the TMS32010 processor, which was then the fastest DSP on the market. The processor is available in many different variants, some with fixed-point arithmetic and some with floating point arithmetic. The TMS320 processors were fabricated on MOS integrated circuit chips, including both NMOS and CMOS variants. The floating point DSP TMS320C3x, which exploits delayed branch logic, has as many as three delay slots. The flexibility of this line of processors has led to it being used not merely as a co-processor for digital signal processing but also as a main CPU. Newer implementations support standard IEEE JTAG control for boundary scan and/or in-circuit debugging. The original TMS32010 and its subsequent variants is an example of a CPU with a modified Harvard architecture, which features separate address spaces for instr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Digital Signal Processor

A digital signal processor (DSP) is a specialized microprocessor chip, with its architecture optimized for the operational needs of digital signal processing. DSPs are fabricated on MOS integrated circuit chips. They are widely used in audio signal processing, telecommunications, digital image processing, radar, sonar and speech recognition systems, and in common consumer electronic devices such as mobile phones, disk drives and high-definition television (HDTV) products. The goal of a DSP is usually to measure, filter or compress continuous real-world analog signals. Most general-purpose microprocessors can also execute digital signal processing algorithms successfully, but may not be able to keep up with such processing continuously in real-time. Also, dedicated DSPs usually have better power efficiency, thus they are more suitable in portable devices such as mobile phones because of power consumption constraints. DSPs often use special memory architectures that ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Delayed Branch Logic

In computer architecture, a delay slot is an instruction slot being executed without the effects of a preceding instruction. The most common form is a single arbitrary instruction located immediately after a branch instruction on a RISC or DSP architecture; this instruction will execute even if the preceding branch is taken. Thus, by design, the instructions appear to execute in an illogical or incorrect order. It is typical for assemblers to automatically reorder instructions by default, hiding the awkwardness from assembly developers and compilers. Branch delay slots When a branch instruction is involved, the location of the following delay slot instruction in the pipeline may be called a branch delay slot. Branch delay slots are found mainly in DSP architectures and older RISC architectures. MIPS, PA-RISC, ETRAX CRIS, SuperH, and SPARC are RISC architectures that each have a single branch delay slot; PowerPC, ARM, Alpha, and RISC-V do not have any. DSP architectur ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Branch Delay Slot

In computer architecture, a delay slot is an instruction slot being executed without the effects of a preceding instruction. The most common form is a single arbitrary instruction located immediately after a branch instruction on a RISC or DSP architecture; this instruction will execute even if the preceding branch is taken. Thus, by design, the instructions appear to execute in an illogical or incorrect order. It is typical for assemblers to automatically reorder instructions by default, hiding the awkwardness from assembly developers and compilers. Branch delay slots When a branch instruction is involved, the location of the following delay slot instruction in the pipeline may be called a branch delay slot. Branch delay slots are found mainly in DSP architectures and older RISC architectures. MIPS, PA-RISC, ETRAX CRIS, SuperH, and SPARC are RISC architectures that each have a single branch delay slot; PowerPC, ARM, Alpha, and RISC-V do not have any. DSP architectu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

JTAG

JTAG (named after the Joint Test Action Group which codified it) is an industry standard for verifying designs and testing printed circuit boards after manufacture. JTAG implements standards for on-chip instrumentation in electronic design automation (EDA) as a complementary tool to digital simulation. It specifies the use of a dedicated debug port implementing a serial communications interface for low-overhead access without requiring direct external access to the system address and data buses. The interface connects to an on-chip Test Access Port (TAP) that implements a stateful protocol to access a set of test registers that present chip logic levels and device capabilities of various parts. The Joint Test Action Group formed in 1985 to develop a method of verifying designs and testing printed circuit boards after manufacture. In 1990 the Institute of Electrical and Electronics Engineers codified the results of the effort in IEEE Standard 1149.1-1990, entitled ''Standard Test ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Fixed-point Arithmetic

In computing, fixed-point is a method of representing fractional (non-integer) numbers by storing a fixed number of digits of their fractional part. Dollar amounts, for example, are often stored with exactly two fractional digits, representing the cents (1/100 of dollar). More generally, the term may refer to representing fractional values as integer multiples of some fixed small unit, e.g. a fractional amount of hours as an integer multiple of ten-minute intervals. Fixed-point number representation is often contrasted to the more complicated and computationally demanding floating-point representation. In the fixed-point representation, the fraction is often expressed in the same number base as the integer part, but using negative powers of the base ''b''. The most common variants are decimal (base 10) and binary (base 2). The latter is commonly known also as binary scaling. Thus, if ''n'' fraction digits are stored, the value will always be an integer multiple of ''b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Modified Harvard Architecture

The modified Harvard architecture is a variation of the Harvard computer architecture that, unlike the pure Harvard architecture, allows the contents of the instruction memory to be accessed as data. Most modern computers that are documented as Harvard architecture are, in fact, modified Harvard architecture. Harvard architecture The original Harvard architecture computer, the Harvard Mark I, employed entirely separate memory systems to store instructions and data. The CPU fetched the next instruction and loaded or stored data simultaneously and independently. This is in contrast to a von Neumann architecture computer, in which both instructions and data are stored in the same memory system and (without the complexity of a CPU cache) must be accessed in turn. The physical separation of instruction and data memory is sometimes held to be the distinguishing feature of modern Harvard architecture computers. With microcontrollers (entire computer systems integrated onto single ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Quadrature Encoder

An incremental encoder is a linear or rotary electromechanical device that has two output signals, ''A'' and ''B'', which issue pulses when the device is moved. Together, the ''A'' and ''B'' signals indicate both the occurrence of and direction of movement. Many incremental encoders have an additional output signal, typically designated ''index'' or ''Z'', which indicates the encoder is located at a particular reference position. Also, some encoders provide a status output (typically designated ''alarm'') that indicates internal fault conditions such as a bearing failure or sensor malfunction. Unlike an absolute encoder, an incremental encoder does not indicate absolute position; it only reports changes in position and, for each reported position change, the direction of movement. Consequently, to determine absolute position at any particular moment, it is necessary to send the encoder signals to an ''incremental encoder interface'', which in turn will "track" and report the enco ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

I²C

I2C (Inter-Integrated Circuit, ), alternatively known as I2C or IIC, is a synchronous, multi-controller/multi-target (master/slave), packet switched, single-ended, serial communication bus invented in 1982 by Philips Semiconductors. It is widely used for attaching lower-speed peripheral ICs to processors and microcontrollers in short-distance, intra-board communication. Several competitors, such as Siemens, NEC, Texas Instruments, STMicroelectronics, Motorola, Nordic Semiconductor and Intersil, have introduced compatible I2C products to the market since the mid-1990s. System Management Bus (SMBus), defined by Intel in 1995, is a subset of I2C, defining a stricter usage. One purpose of SMBus is to promote robustness and interoperability. Accordingly, modern I2C systems incorporate some policies and rules from SMBus, sometimes supporting both I2C and SMBus, requiring only minimal reconfiguration either by commanding or output pin use. Applications I2C is appropriate f ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Serial Peripheral Interface Bus

The Serial Peripheral Interface (SPI) is a synchronous serial communication interface specification used for short-distance communication, primarily in embedded systems. The interface was developed by Motorola in the mid-1980s and has become a ''de facto'' standard. Typical applications include Secure Digital cards and liquid crystal displays. SPI devices communicate in full duplex mode using a master-slave architecture usually with a single master (though some Atmel and Silabs devices support changing roles on the fly depending on an external (SS) pin). The master (controller) device originates the frame for reading and writing. Multiple slave-devices may be supported through selection with individual chip select (CS), sometimes called slave select (SS) lines. Sometimes SPI is called a ''four-wire'' serial bus, contrasting with three-, two-, and one-wire serial buses. The SPI may be accurately described as a synchronous serial interface, but it is different from the S ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

KL TI TMS32020

KL, kL, kl, or kl. may refer to: Businesses and organizations * KLM, a Dutch airline (IATA airline designator KL) * Koninklijke Landmacht, the Royal Netherlands Army * Kvenna Listin ("Women's List"), a political party in Iceland * KL FM, a Malay language radio station Places * Kaiserslautern, Germany (license plate code KL) * Kerala, India (ISO 3166-2:IN subcode KL) * Kirkland Lake, Ontario, Canada * Kowloon, Hong Kong * Kuala Lumpur, Malaysia Science, technology, and mathematics * KL engine, version of the Mazda K engine * Klepton (kl.), a type of species in zoology * Kiloliter (kL), a unit of volume * Kullback–Leibler divergence in mathematics * KL (gene), a gene which encodes the klotho enzyme in humans Other uses * Jeep Cherokee (KL) * Kalaallisut language (ISO 639 alpha-2 language code "kl") * Kl (digraph), used in the Zulu language to write /kʟ̥ʼ/ or /kxʼ/ * Konzentrationslager, or concentration camp, abbreviated KZ or KL * ''KL – A History of the Nazi Concentra ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

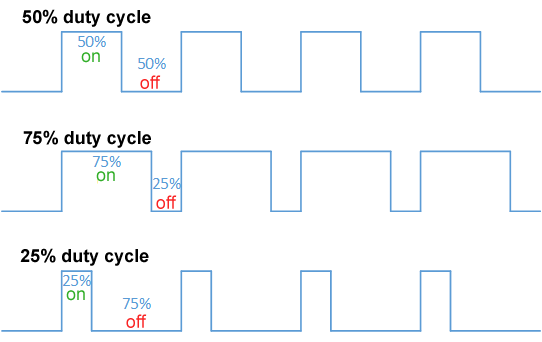

Pulse-width Modulation

Pulse-width modulation (PWM), or pulse-duration modulation (PDM), is a method of reducing the average power delivered by an electrical signal, by effectively chopping it up into discrete parts. The average value of voltage (and current) fed to the load is controlled by turning the switch between supply and load on and off at a fast rate. The longer the switch is on compared to the off periods, the higher the total power supplied to the load. Along with maximum power point tracking (MPPT), it is one of the primary methods of reducing the output of solar panels to that which can be utilized by a battery. PWM is particularly suited for running inertial loads such as motors, which are not as easily affected by this discrete switching, because their inertia causes them to react slowly. The PWM switching frequency has to be high enough not to affect the load, which is to say that the resultant waveform perceived by the load must be as smooth as possible. The rate (or frequency) ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)