|

SPARC T3

The SPARC T3 microprocessor (previously known as UltraSPARC T3, codenamed ''Rainbow Falls'', and also known as UltraSPARC KT or ''Niagara-3'' during development) is a multithreading, multi-core CPU produced by Oracle Corporation (previously Sun Microsystems). Officially launched on 20 September 2010, it is a member of the SPARC family, and the successor to the UltraSPARC T2. Performance Overall single socket and multi-socket throughput increased with the T3 processor in systems, providing superior throughput with half the CPU socket requirements to its predecessor. The throughput (SPEC CINT2006 rate) increased in single a socket T3-1 platform in comparison to its predecessor T2+ processor in a dual-socket T5240 platform. Under simulated web serving workloads, dual-socket based SPARC T3 systems benchmarked better performance than quad-socket (previous generation) UltraSPARC T2+ systems (as well as competing dual and quad socket contemporary systems). History Online IT public ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Oracle Corporation

Oracle Corporation is an American multinational computer technology corporation headquartered in Austin, Texas. In 2020, Oracle was the third-largest software company in the world by revenue and market capitalization. The company sells database software and technology (particularly its own brands), cloud engineered systems, and enterprise software products, such as enterprise resource planning (ERP) software, human capital management (HCM) software, customer relationship management (CRM) software (also known as customer experience), enterprise performance management (EPM) software, and supply chain management (SCM) software. History Larry Ellison co-founded Oracle Corporation in 1977 with Bob Miner and Ed Oates under the name Software Development Laboratories (SDL). Ellison took inspiration from the 1970 paper written by Edgar F. Codd on relational database management systems ( RDBMS) named "A Relational Model of Data for Large Shared Data Banks." He heard about the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CPU Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Advanced Encryption Standard

The Advanced Encryption Standard (AES), also known by its original name Rijndael (), is a specification for the encryption of electronic data established by the U.S. National Institute of Standards and Technology (NIST) in 2001. AES is a variant of the Rijndael block cipher developed by two Belgian cryptographers, Joan Daemen and Vincent Rijmen, who submitted a proposal to NIST during the AES selection process. Rijndael is a family of ciphers with different key and block sizes. For AES, NIST selected three members of the Rijndael family, each with a block size of 128 bits, but three different key lengths: 128, 192 and 256 bits. AES has been adopted by the U.S. government. It supersedes the Data Encryption Standard (DES), which was published in 1977. The algorithm described by AES is a symmetric-key algorithm, meaning the same key is used for both encrypting and decrypting the data. In the United States, AES was announced by the NIST as U.S. FIPS PUB 197 (FIPS 197) on Novemb ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Triple DES

In cryptography, Triple DES (3DES or TDES), officially the Triple Data Encryption Algorithm (TDEA or Triple DEA), is a symmetric-key block cipher, which applies the DES cipher algorithm three times to each data block. The Data Encryption Standard's (DES) 56-bit key is no longer considered adequate in the face of modern cryptanalytic techniques and supercomputing power. A CVE released in 2016, CVE-2016-2183' disclosed a major security vulnerability in DES and 3DES encryption algorithms. This CVE, combined with the inadequate key size of DES and 3DES, NIST has deprecated DES and 3DES for ''new'' applications in 2017, and for ''all'' applications by the end of 2023. It has been replaced with the more secure, more robust AES. While the government and industry standards abbreviate the algorithm's name as TDES (Triple DES) and TDEA (Triple Data Encryption Algorithm), RFC 1851 referred to it as 3DES from the time it first promulgated the idea, and this namesake has since come into wi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Data Encryption Standard

The Data Encryption Standard (DES ) is a symmetric-key algorithm for the encryption of digital data. Although its short key length of 56 bits makes it too insecure for modern applications, it has been highly influential in the advancement of cryptography. Developed in the early 1970s at IBM and based on an earlier design by Horst Feistel, the algorithm was submitted to the National Bureau of Standards (NBS) following the agency's invitation to propose a candidate for the protection of sensitive, unclassified electronic government data. In 1976, after consultation with the National Security Agency (NSA), the NBS selected a slightly modified version (strengthened against differential cryptanalysis, but weakened against brute-force attacks), which was published as an official Federal Information Processing Standard (FIPS) for the United States in 1977. The publication of an NSA-approved encryption standard led to its quick international adoption and widespread academic scrutiny. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Oracle VM Server For SPARC

An oracle is a person or agency considered to provide wise and insightful counsel or prophetic predictions, most notably including precognition of the future, inspired by deities. As such, it is a form of divination. Description The word ''oracle'' comes from the Latin verb ''ōrāre'', "to speak" and properly refers to the priest or priestess uttering the prediction. In extended use, ''oracle'' may also refer to the ''site of the oracle'', and to the oracular utterances themselves, called ''khrēsmē'' 'tresme' (χρησμοί) in Greek. Oracles were thought to be portals through which the gods spoke directly to people. In this sense, they were different from seers (''manteis'', μάντεις) who interpreted signs sent by the gods through bird signs, animal entrails, and other various methods.Flower, Michael Attyah. ''The Seer in Ancient Greece.'' Berkeley: University of California Press, 2008. The most important oracles of Greek antiquity were Pythia (priestess to Apollo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SPARC Enterprise

The SPARC Enterprise series is a range of UNIX server computers based on the SPARC V9 architecture. It was co-developed by Sun Microsystems and Fujitsu, announced on June 1st, 2004 and introduced in 2007. They were marketed and sold by Sun Microsystems (later Oracle Corporation, after their Oracle acquisition of Sun, acquisition of Sun), Fujitsu, and Fujitsu Siemens Computers under the common brand of "SPARC Enterprise", superseding Sun's Sun Fire and Fujitsu's PRIMEPOWER server product lines. Codename is APL (Advanced Product Line). Since 2010, servers based on new SPARC CMT processors (SPARC T3 and later) have been branded as Oracle's SPARC T-Series servers, the "SPARC Enterprise" brand being dropped. Fujitsu continued to sell SPARC T-Series as their SPARC Enterprise product line until December 2015. Fujitsu rebranded the product line to "SPARC Servers" since SPARC M10 released in 2013 and continued to sell SPARC M-Series and T-Series with their new brand. Model range SPARC6 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Oracle SPARC T-series Servers

The SPARC T-series family of RISC processors and server computers, based on the SPARC V9 architecture, was originally developed by Sun Microsystems, and later by Oracle Corporation after its acquisition of Sun. Its distinguishing feature from earlier SPARC iterations is the introduction of chip multithreading (CMT) technology, a multithreading, multicore design intended to drive greater processor utilization at lower power consumption. The first generation T-series processor, the UltraSPARC T1, and servers based on it, were announced in December 2005. As later generations were introduced, the term "T series" was used to refer to the entire family of processors. Pre-Oracle era Sun Microsystems' Sun Fire and SPARC Enterprise product lines were based on early generations of CMT technology. The UltraSPARC T1 based Sun Fire T2000 and T1000 servers were launched in December 2005 and early 2006, respectively. They were later rebranded to match the name of the UltraSPARC T2 and T2 Plu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

10 Gigabit Ethernet

10 Gigabit Ethernet (10GE, 10GbE, or 10 GigE) is a group of computer networking technologies for transmitting Ethernet frames at a rate of 10 gigabits per second. It was first defined by the IEEE 802.3ae-2002 standard. Unlike previous Ethernet standards, 10 Gigabit Ethernet defines only full-duplex point-to-point links which are generally connected by network switches; shared-medium CSMA/CD operation has not been carried over from the previous generations Ethernet standards so half-duplex operation and repeater hubs do not exist in 10GbE. The 10 Gigabit Ethernet standard encompasses a number of different physical layer (PHY) standards. A networking device, such as a switch or a network interface controller may have different PHY types through pluggable PHY modules, such as those based on SFP+. Like previous versions of Ethernet, 10GbE can use either copper or fiber cabling. Maximum distance over copper cable is 100 meters but because of its bandwidth requirements, higher ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Gigabit Ethernet

In computer networking, Gigabit Ethernet (GbE or 1 GigE) is the term applied to transmitting Ethernet frames at a rate of a gigabit per second. The most popular variant, 1000BASE-T, is defined by the IEEE 802.3ab standard. It came into use in 1999, and has replaced Fast Ethernet in wired local networks due to its considerable speed improvement over Fast Ethernet, as well as its use of cables and equipment that are widely available, economical, and similar to previous standards. History Ethernet was the result of research conducted at Xerox PARC in the early 1970s, and later evolved into a widely implemented physical and link layer protocol. Fast Ethernet increased the speed from 10 to 100 megabits per second (Mbit/s). Gigabit Ethernet was the next iteration, increasing the speed to 1000 Mbit/s. * The initial standard for Gigabit Ethernet was produced by the IEEE in June 1998 as IEEE 802.3z, and required optical fiber. 802.3z is commonly referred to as 1000BASE-X, whe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hardware Acceleration

Hardware acceleration is the use of computer hardware designed to perform specific functions more efficiently when compared to software running on a general-purpose central processing unit (CPU). Any transformation of data that can be calculated in software running on a generic CPU can also be calculated in custom-made hardware, or in some mix of both. To perform computing tasks more quickly (or better in some other way), generally one can invest time and money in improving the software, improving the hardware, or both. There are various approaches with advantages and disadvantages in terms of decreased latency, increased throughput and reduced energy consumption. Typical advantages of focusing on software may include more rapid development, lower non-recurring engineering costs, heightened portability, and ease of updating features or patching bugs, at the cost of overhead to compute general operations. Advantages of focusing on hardware may include speedup, reduced pow ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

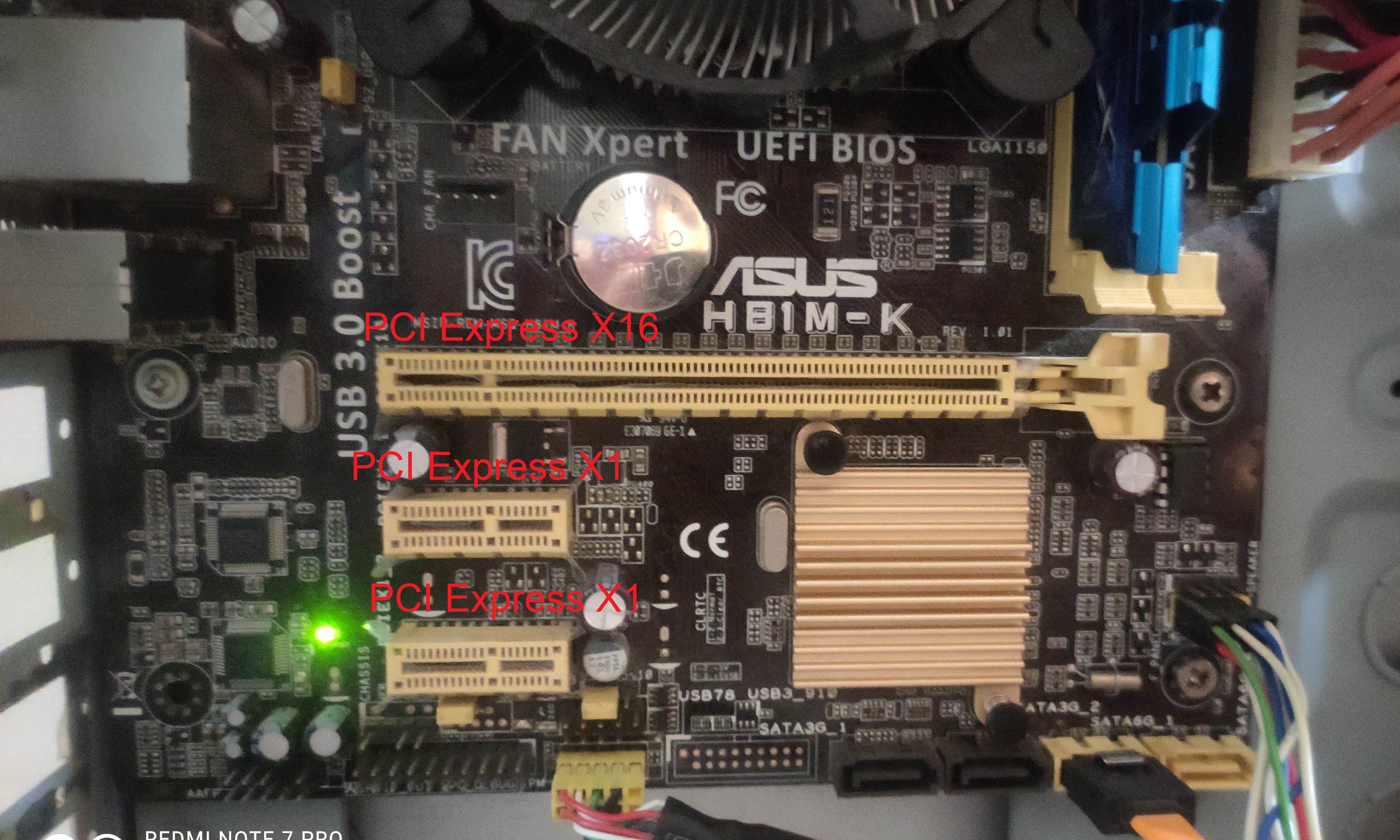

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directions. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

_Round_Function.png)