|

Superscalar Microprocessors

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a superscalar processor can execute more than one instruction during a clock cycle by simultaneously dispatching multiple instructions to different execution units on the processor. It therefore allows more throughput (the number of instructions that can be executed in a unit of time) than would otherwise be possible at a given clock rate. Each execution unit is not a separate processor (or a core if the processor is a multi-core processor), but an execution resource within a single CPU such as an arithmetic logic unit. In Flynn's taxonomy, a single-core superscalar processor is classified as an SISD processor (single instruction stream, single data stream), though a single-core superscalar processor that supports short vector operations co ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Data Dependencies

A data dependency in computer science is a situation in which a program statement (instruction) refers to the data of a preceding statement. In compiler theory, the technique used to discover data dependencies among statements (or instructions) is called dependence analysis. There are three types of dependencies: data, name, and control. Data dependencies Assuming statement S_1 and S_2, S_2 depends on S_1 if: :\left (S_1) \cap O(S_2)\right\cup \left (S_1) \cap I(S_2)\right\cup \left (S_1) \cap O(S_2)\right\neq \varnothing where: * I(S_i) is the set of memory locations read by * O(S_j) is the set of memory locations written by and * there is a feasible run-time execution path from S_1 to This Condition is called Bernstein Condition, named by A. J. Bernstein. Three cases exist: * Anti-dependence: I(S_1) \cap O(S_2) \neq \varnothing, S_1 \rightarrow S_2 and S_1 reads something before S_2 overwrites it * Flow (data) dependence: O(S_1) \cap I(S_2) \neq \varnothing, S_1 \righ ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

P5 (microarchitecture)

The Pentium (also referred to as P5, its microarchitecture, or i586) is a fifth generation, 32-bit x86 microprocessor that was introduced by Intel on March 22, 1993, as the very first CPU in the Pentium brand. It was instruction set compatible with the 80486 but was a new and very different microarchitecture design from previous iterations. The P5 Pentium was the first superscalar x86 microarchitecture and the world's first superscalar microprocessor to be in mass productionmeaning it generally executes at least 2 instructions per clock mainly because of a design-first dual integer pipeline design previously thought impossible to implement on a CISC microarchitecture. Additional features include a faster floating-point unit, wider data bus, separate code and data caches, and many other techniques and features to enhance performance and support security, encryption, and multiprocessing, for workstations and servers when compared to the next best previous industry standard p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Battery (electricity)

An electric battery is a source of electric power consisting of one or more electrochemical cells with external connections for powering electrical devices. When a battery is supplying power, its positive terminal is the cathode and its negative terminal is the anode. The terminal marked negative is the source of electrons that will flow through an external electric circuit to the positive terminal. When a battery is connected to an external electric load, a redox reaction converts high-energy reactants to lower-energy products, and the free-energy difference is delivered to the external circuit as electrical energy. Historically the term "battery" specifically referred to a device composed of multiple cells; however, the usage has evolved to include devices composed of a single cell. Primary (single-use or "disposable") batteries are used once and discarded, as the electrode materials are irreversibly changed during discharge; a common example is the alkaline battery us ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Embedded System

An embedded system is a computer system—a combination of a computer processor, computer memory, and input/output peripheral devices—that has a dedicated function within a larger mechanical or electronic system. It is ''embedded'' as part of a complete device often including electrical or electronic hardware and mechanical parts. Because an embedded system typically controls physical operations of the machine that it is embedded within, it often has real-time computing constraints. Embedded systems control many devices in common use today. , it was estimated that ninety-eight percent of all microprocessors manufactured were used in embedded systems. Modern embedded systems are often based on microcontrollers (i.e. microprocessors with integrated memory and peripheral interfaces), but ordinary microprocessors (using external chips for memory and peripheral interface circuits) are also common, especially in more complex systems. In either case, the processor(s) u ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Low-power Electronics

Low-power electronics are electronics, such as notebook processors, that have been designed to use less electric power than usual, often at some expense. In the case of notebook processors, this expense is processing power; notebook processors usually consume less power than their desktop counterparts, at the expense of lower processing power. History Watches The earliest attempts to reduce the amount of power required by an electronic device were related to the development of the wristwatch. Electronic watches require electricity as a power source, and some mechanical movements and hybrid electromechanical movements also require electricity. Usually, the electricity is provided by a replaceable battery. The first use of electrical power in watches was as a substitute for the mainspring, to remove the need for winding. The first electrically powered watch, the Hamilton Electric 500, was released in 1957 by the Hamilton Watch Company of Lancaster, Pennsylvania. The first quartz ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Complex Instruction Set Computer

A complex instruction set computer (CISC ) is a computer architecture in which single instructions can execute several low-level operations (such as a load from memory, an arithmetic operation, and a memory store) or are capable of multi-step operations or addressing modes within single instructions. The term was retroactively coined in contrast to reduced instruction set computer (RISC) and has therefore become something of an umbrella term for everything that is not RISC, where the typical differentiating characteristic is that most RISC designs use uniform instruction length for almost all instructions, and employ strictly separate load and store instructions. Examples of CISC architectures include complex mainframe computers to simplistic microcontrollers where memory load and store operations are not separated from arithmetic instructions. Specific instruction set architectures that have been retroactively labeled CISC are System/360 through z/Architecture, the PDP-11 and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

RISC

In computer engineering, a reduced instruction set computer (RISC) is a computer designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set computer (CISC), a RISC computer might require more instructions (more code) in order to accomplish a task because the individual instructions are written in simpler code. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in particular by implementing an instruction pipeline, which may be simpler given simpler instructions. The key operational concept of the RISC computer is that each instruction performs only one function (e.g. copy a value from memory to a register). The RISC computer usually has many (16 or 32) high-speed, general-purpose registers with a load/store architecture in which the code for the register-register instructions (for performing arithmetic and tests) are separate f ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD 29000

The AMD Am29000, commonly shortened to 29k, is a family of 32-bit RISC microprocessors and microcontrollers developed and fabricated by Advanced Micro Devices (AMD). Based on the seminal Berkeley RISC, the 29k added a number of significant improvements. They were, for a time, the most popular RISC chips on the market, widely used in laser printers from a variety of manufacturers. Developed since 1984-1985, announced in March 1987 and released in May 1988, the initial Am29000 was followed by several versions, ending with the Am29040 in 1995. The 29050 was notable for being early to feature a floating point unit capable of executing one multiply–add operation per cycle. AMD was designing a superscalar version until late 1995, when AMD dropped the development of the 29k because the design team was transferred to support the PC ( x86) side of the business. What remained of AMD's embedded business was realigned towards the embedded 186 family of 80186 derivatives. By then the majo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

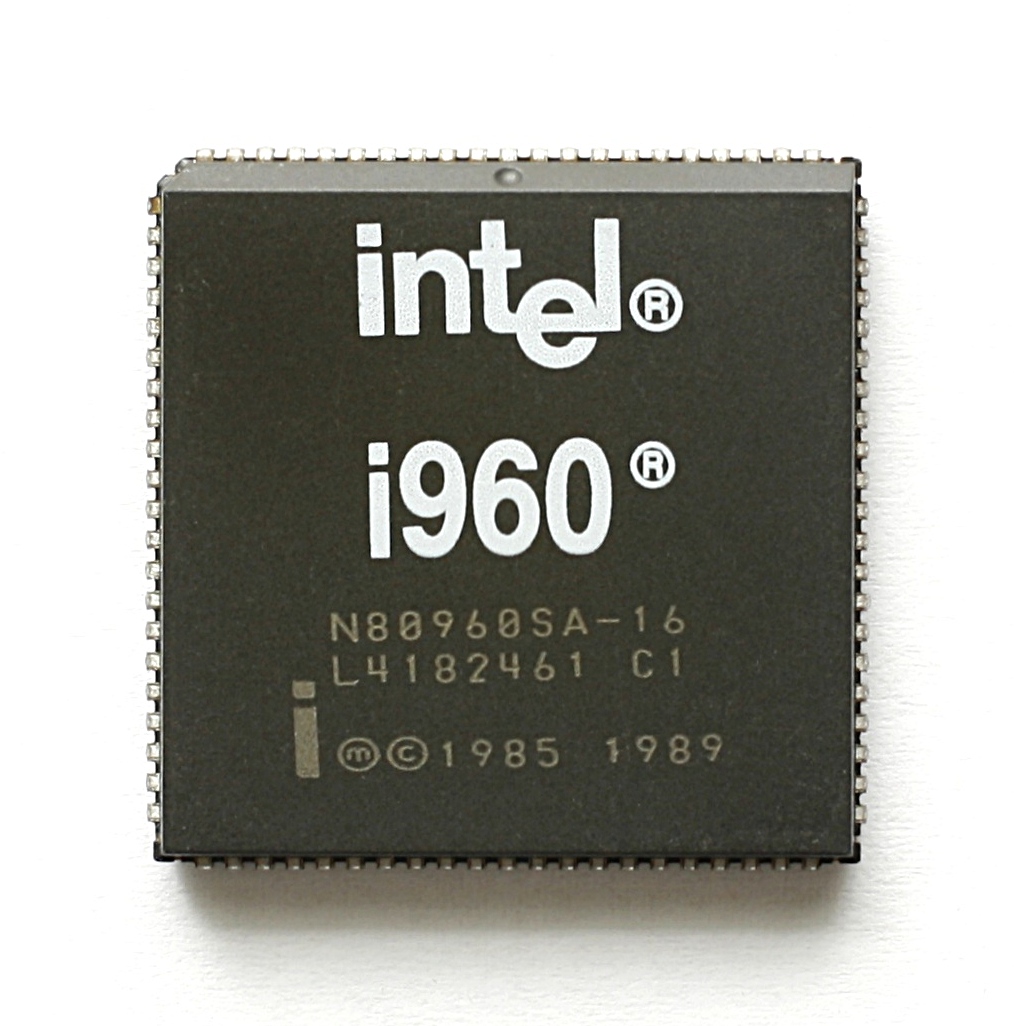

Intel I960

Intel's i960 (or 80960) was a RISC-based microprocessor design that became popular during the early 1990s as an embedded microcontroller. It became a best-selling CPU in that segment, along with the competing AMD 29000. In spite of its success, Intel stopped marketing the i960 in the late 1990s, as a result of a settlement with DEC whereby Intel received the rights to produce the StrongARM CPU. The processor continues to be used for a few military applications. Origin The i960 design was begun in response to the failure of Intel's iAPX 432 design of the early 1980s. The iAPX 432 was intended to directly support high-level languages that supported tagged, protected, garbage-collected memory—such as Ada and Lisp—in hardware. Because of its instruction-set complexity, its multi-chip implementation, and design flaws, the iAPX 432 was very slow in comparison to other processors of its time. In 1984, Intel and Siemens started a joint project, ultimately called Bii ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MC88100

The MC88100 is a microprocessor developed by Motorola that implemented 88000 RISC instruction set architecture. Announced in 1988, the MC88100 was the first 88000 implementation. It was succeeded by the MC88110 in the early 1990s. The microprocessor has separate pipelined integer, floating-point add, floating-point multiply, and load/store execution units and dispatches a single instruction (at most) per clock cycle. The separate MC88200 integrated circuit optionally add level 1 cache and a paged memory management unit. An MC88100 system typically used two of these devices for instructions and data; additional MC88200s could be added to increase the size of the caches. This partitioned scheme was chosen to provide system flexibility, the amount of cache could be varied depending on the price point. In practice, these additional chips required more space on the circuit board and the buses between the MC88200s and MC88100 added complexity and cost. The MC88100 contained 165,000 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

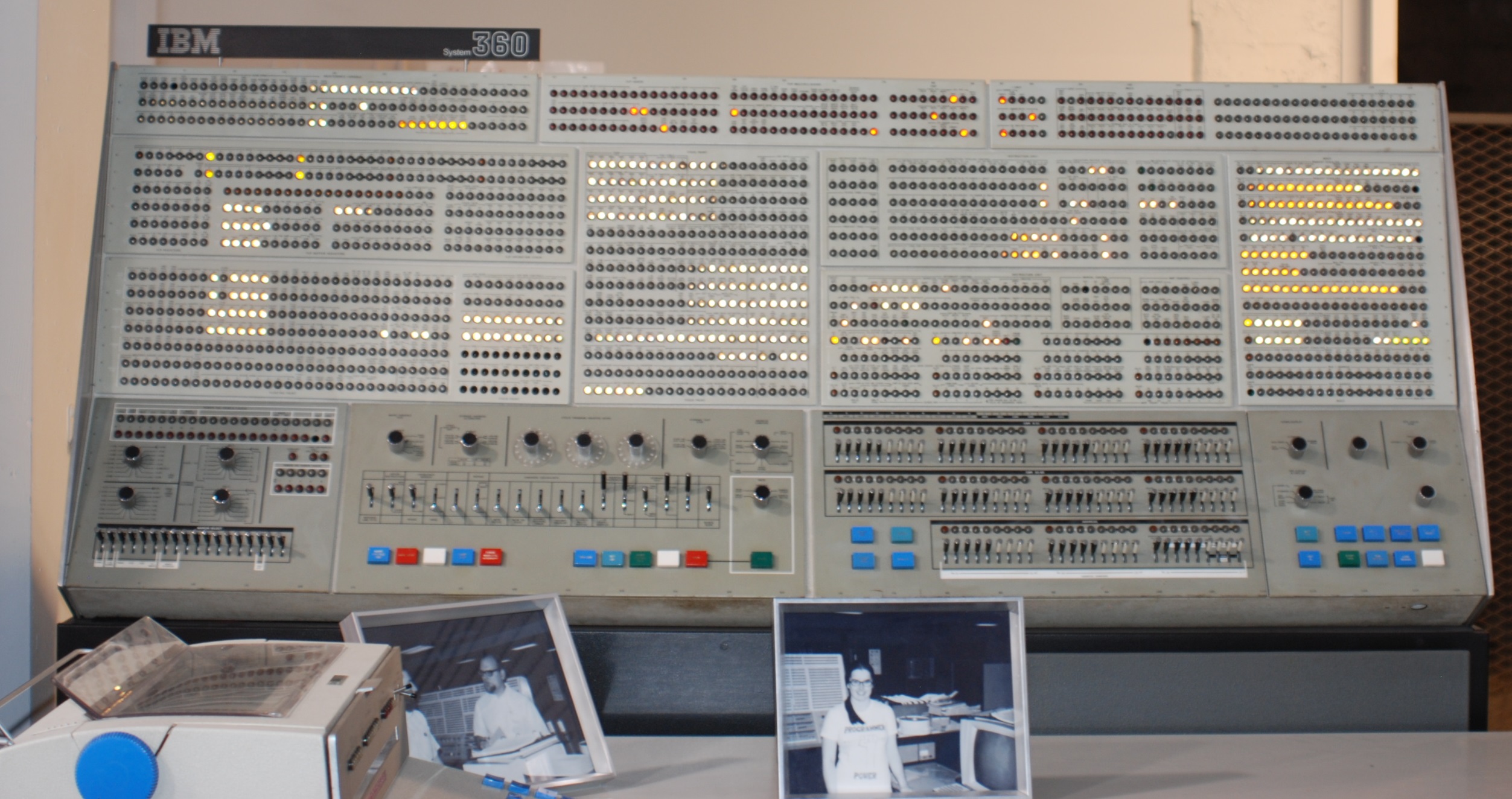

IBM System/360 Model 91

The IBM System/360 Model 91 was announced in 1964 as a competitor to the CDC 6600. Functionally, the Model 91 ran like any other large-scale System/360, but the internal organization was the most advanced of the System/360 line, and it was the first IBM computer to support out-of-order instruction execution. It ran OS/360 as its operating system. It was designed to handle high-speed data processing for scientific applications. This included space exploration, theoretical astronomy, sub-atomic physics and global weather forecasting. The first Model 91 was used at the NASA Goddard Space Flight Center in 1968 and at the time was the most powerful computer in user operation. It was capable of executing up to 16.6 million instructions per second, making it roughly equivalent to an intel 80486SX-20 MHz CPU or AMD 80386DX-40 MHz CPU in MIPS performance. The CPU consisted of five autonomous units: instruction, floating-point, fixed-point, and two storage controllers for the overlap ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |