|

Skylake (microarchitecture)

Skylake is Intel's codename for its sixth generation Core microprocessor family that was launched on August 5, 2015, succeeding the Broadwell microarchitecture. Skylake is a microarchitecture redesign using the same 14 nm manufacturing process technology as its predecessor, serving as a tock in Intel's tick–tock manufacturing and design model. According to Intel, the redesign brings greater CPU and GPU performance and reduced power consumption. Skylake CPUs share their microarchitecture with Kaby Lake, Coffee Lake, Whiskey Lake, and Comet Lake CPUs. Skylake is the last Intel platform on which Windows earlier than Windows 10 are officially supported by Microsoft, although enthusiast-created modifications are available that disabled the Windows Update check and allowed Windows 8.1 and earlier to continue to receive Windows Updates on this and later platforms. Some of the processors based on the Skylake microarchitecture are marketed as sixth-generation Core. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California, and Delaware General Corporation Law, incorporated in Delaware. Intel designs, manufactures, and sells computer components such as central processing units (CPUs) and related products for business and consumer markets. It is one of the world's List of largest semiconductor chip manufacturers, largest semiconductor chip manufacturers by revenue, and ranked in the Fortune 500, ''Fortune'' 500 list of the List of largest companies in the United States by revenue, largest United States corporations by revenue for nearly a decade, from 2007 to 2016 Fiscal year, fiscal years, until it was removed from the ranking in 2018. In 2020, it was reinstated and ranked 45th, being the List of Fortune 500 computer software and information companies, 7th-largest technology company in the ranking. It was one of the first companies listed on Nasdaq. Intel supplies List of I ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSSE3

Supplemental Streaming SIMD Extensions 3 (SSSE3 or SSE3S) is a SIMD instruction set created by Intel and is the fourth iteration of the SSE technology. History SSSE3 was first introduced with Intel processors based on the Core microarchitecture on June 26, 2006 with the "Woodcrest" Xeons. SSSE3 has been referred to by the codenames Tejas New Instructions (TNI) or Merom New Instructions (MNI) for the first processor designs intended to support it. SSSE3 has enhanced for HD audio/video decoding/encoding, for example AAC. Functionality SSSE3 contains 16 new discrete instructions. Each instruction can act on 64-bit MMX or 128-bit XMM registers. Therefore, Intel's materials refer to 32 new instructions. They include: * Twelve instructions that perform horizontal addition or subtraction operations. * Six instructions that evaluate absolute values. * Two instructions that perform multiply-and-add operations and speed up the evaluation of dot products. * Two instructions tha ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Broadwell (microarchitecture)

Broadwell (previously Rockwell) is the fifth generation of the Intel Core processor. It is Intel's codename for the 14 nanometer die shrink of its Haswell microarchitecture. It is a "tick" in Intel's tick–tock principle as the next step in semiconductor fabrication. Like some of the previous tick-tock iterations, Broadwell did not completely replace the full range of CPUs from the previous microarchitecture ( Haswell), as there were no low-end desktop CPUs based on Broadwell. Some of the processors based on the Broadwell microarchitecture are marketed as "5th-generation Core" i3, i5 and i7 processors. This moniker is however not used for marketing of the Broadwell-based Celeron, Pentium or Xeon chips. This microarchitecture also introduced the Core M processor branding. Broadwell's H and C variants are used in conjunction with Intel 9 Series chipsets ( Z97, H97 and HM97), in addition to retaining backward compatibility with some of the Intel 8 Series chipse ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LGA 3647

LGA 3647 is an Intel microprocessor compatible socket Socket may refer to: Mechanics * Socket wrench, a type of wrench that uses separate, removable sockets to fit different sizes of nuts and bolts * Socket head screw, a screw (or bolt) with a cylindrical head containing a socket into which the hexag ... used by Xeon Phi x200 ("Knights Landing"), Xeon Phi 72x5 ("Knights Mill"), Skylake-SP, Cascade Lake-SP, and Cascade Lake-W microprocessors. The socket supports a 6-channel memory controller, non-volatile 3D XPoint memory DIMMs, Intel Ultra Path Interconnect (UPI), as a replacement for Quick Path Interconnect (QPI), and 100G Omni-Path interconnect and also has a new mounting mechanism which does not use a lever to secure it in place but the CPU cooler's pressure and its screws to secure it in place. Variants There are two sub-versions of this socket with differences also in the ILM ( Independent Loading Mechanism, pitch of center screws changed slightly and a more vi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LGA 2066

LGA 2066, also called ''Socket R4'', is a CPU socket by Intel that debuted with Skylake-X and Kaby Lake-X processors in June 2017. It replaces Intel's LGA 2011-3 (R3) in the performance, high-end desktop and Workstation platforms (based on the X299 "Basin Falls" and C422 chipsets), while LGA 3647 (Socket P) replaces LGA 2011-3 (R3) in the server platforms based on Skylake-SP (Xeon "Purley"). Compatible processors High-End Desktop (HEDT) All of these CPUs require the Intel X299 chipset to work. So, the C422 chipset is strictly limited to work with workstation processors only. Kaby Lake-X Kaby Lake-X processors were discontinued in May 2018. Starting October 2019, BIOS In computing, BIOS (, ; Basic Input/Output System, also known as the System BIOS, ROM BIOS, BIOS ROM or PC BIOS) is a type of firmware used to provide runtime services for operating systems and programs and to perform hardware initialization d ... updates for most of the X299-based motherboards removed s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

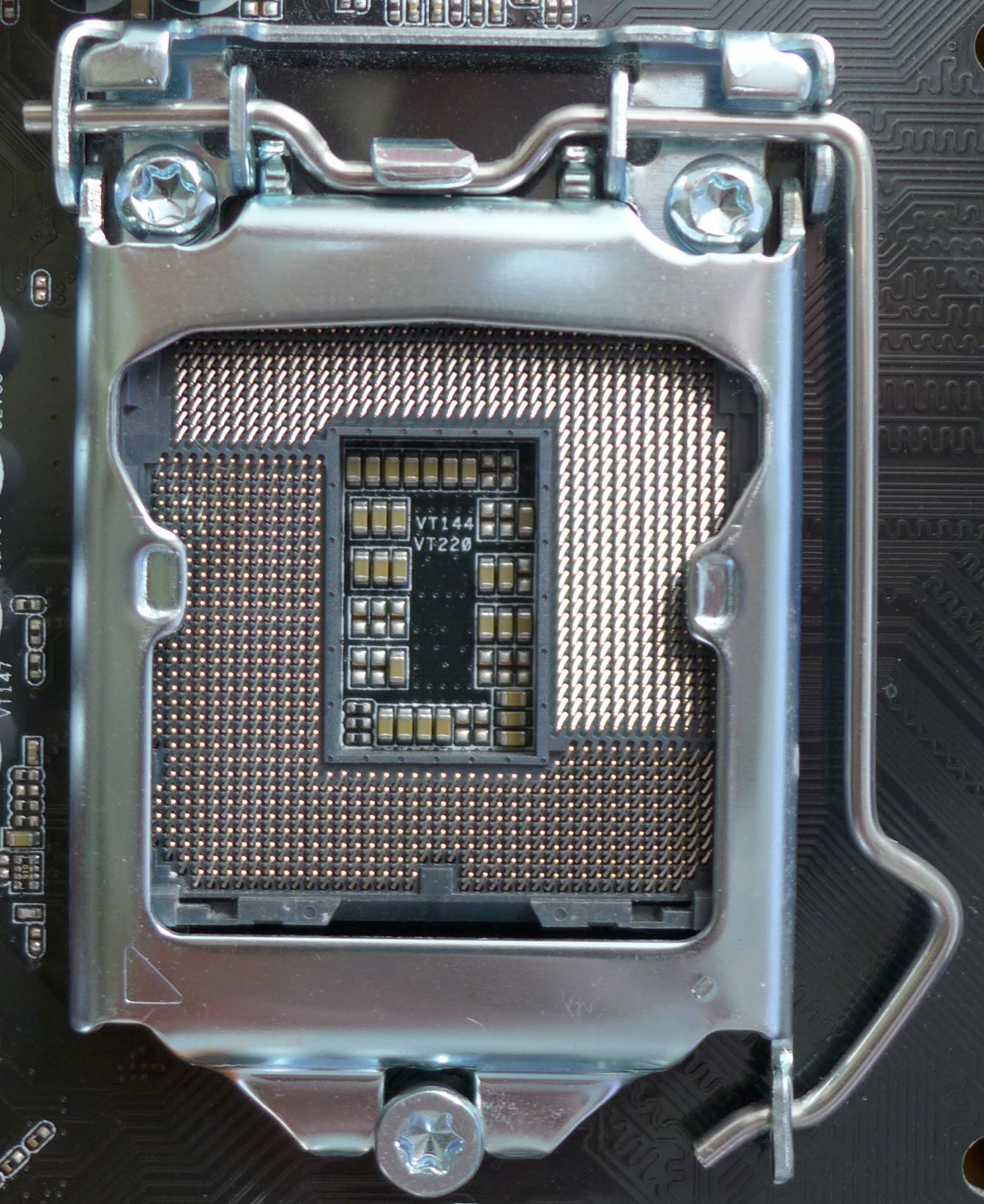

LGA 1151

LGA 1151, also known as Socket H4, is a type of zero insertion force flip-chip land grid array (LGA) socket for Intel desktop processors which comes in two distinct versions: the first revision which supports both Intel's Skylake and Kaby Lake CPUs, and the second revision which supports Coffee Lake CPUs exclusively. LGA 1151 is designed as a replacement for the LGA 1150 (known as ''Socket H3''). LGA 1151 has 1151 protruding pins to make contact with the pads on the processor. The Fully Integrated Voltage Regulator, i.e. a voltage regulator which integrated on the CPU's die, introduced with Haswell and Broadwell, has again been moved to the motherboard. Most motherboards for the first revision of the socket support solely DDR4 memory, a lesser number support DDR3(L) memory, and the least number have slots for both DDR4 or DDR3(L) but only one memory type can be installed. Some have UniDIMM support, enabling either type of memory to be placed in the same DIMM, rather than ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

VT-d

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel ( VT-x) and AMD (AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FMA Instruction Set

The FMA instruction set is an extension to the 128- and 256-bit Streaming SIMD Extensions instructions in the x86 microprocessor instruction set to perform fused multiply–add (FMA) operations. There are two variants: * FMA4 is supported in AMD processors starting with the Bulldozer architecture. FMA4 was performed in hardware before FMA3 was. Support for FMA4 has been removed since Zen 1. * FMA3 is supported in AMD processors starting with the Piledriver architecture and Intel starting with Haswell processors and Broadwell processors since 2014. Instructions FMA3 and FMA4 instructions have almost identical functionality, but are not compatible. Both contain fused multiply–add (FMA) instructions for floating-point scalar and SIMD operations, but FMA3 instructions have three operands, while FMA4 ones have four. The FMA operation has the form ''d'' = round(''a'' · ''b'' + ''c''), where the round function performs a rounding to allow the result to fit within the dest ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Transactional Synchronization Extensions

Transactional Synchronization Extensions (TSX), also called Transactional Synchronization Extensions New Instructions (TSX-NI), is an extension to the x86 instruction set architecture (ISA) that adds hardware transactional memory support, speeding up execution of multi-threaded software through lock elision. According to different benchmarks, TSX/TSX-NI can provide around 40% faster applications execution in specific workloads, and 4–5 times more database transactions per second (TPS). TSX/TSX-NI was documented by Intel in February 2012, and debuted in June 2013 on selected Intel microprocessors based on the Haswell microarchitecture. Haswell processors below 45xx as well as R-series and K-series (with unlocked multiplier) SKUs do not support TSX/TSX-NI. In August 2014, Intel announced a bug in the TSX/TSX-NI implementation on current steppings of Haswell, Haswell-E, Haswell-EP and early Broadwell CPUs, which resulted in disabling the TSX/TSX-NI feature on affected CPUs ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AVX-512

AVX-512 are 512-bit extensions to the 256-bit Advanced Vector Extensions SIMD instructions for x86 instruction set architecture (ISA) proposed by Intel in July 2013, and first implemented in the 2016 Intel Xeon Phi x200 (Knights Landing), and then later in a number of AMD and other Intel CPUs ( see list below). AVX-512 consists of multiple extensions that may be implemented independently. This policy is a departure from the historical requirement of implementing the entire instruction block. Only the core extension AVX-512F (AVX-512 Foundation) is required by all AVX-512 implementations. Besides widening most 256-bit instructions, the extensions introduce various new operations, such as new data conversions, scatter operations, and permutations. The number of AVX registers is increased from 16 to 32, and eight new "mask registers" are added, which allow for variable selection and blending of the results of instructions. In CPUs with the vector length (VL) extension—included in m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Advanced Vector Extensions 2

Advanced Vector Extensions (AVX, also known as Gesher New Instructions and then Sandy Bridge New Instructions) are SIMD extensions to the x86 instruction set architecture for microprocessors from Intel and Advanced Micro Devices (AMD). They were proposed by Intel in March 2008 and first supported by Intel with the Sandy Bridge microarchitecture shipping in Q1 2011 and later by AMD with the Bulldozer microarchitecture shipping in Q4 2011. AVX provides new features, new instructions, and a new coding scheme. AVX2 (also known as Haswell New Instructions) expands most integer commands to 256 bits and introduces new instructions. They were first supported by Intel with the Haswell microarchitecture, which shipped in 2013. AVX-512 expands AVX to 512-bit support using a new EVEX prefix encoding proposed by Intel in July 2013 and first supported by Intel with the Knights Landing co-processor, which shipped in 2016. In conventional processors, AVX-512 was introduced with Skylake serve ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |