|

Single Cycle Processor

A single cycle processor is a processor that carries out one instruction in a single clock cycle. See also * Complex instruction set computer, a processor executing one instruction in multiple clock cycles * DLX, a very similar architecture designed by John L. Hennessy (creator of MIPS) for teaching purposes * MIPS architecture, MIPS-32 architecture * MIPS-X, developed as a follow-on project to the MIPS architecture * Reduced instruction set computer In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a com ..., a processor executing one instruction in minimal clock cycles References External links Microprocessors {{Comp-eng-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Clock Cycle

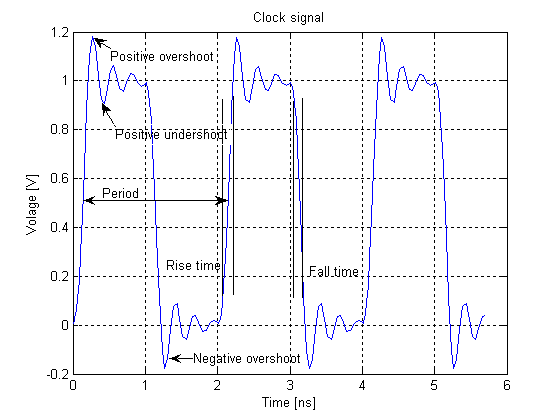

In electronics and especially synchronous digital circuits, a clock signal (historically also known as ''logic beat'') is an electronic logic signal (voltage or current) which oscillates between a high and a low state at a constant frequency and is used like a metronome to synchronize actions of digital circuits. In a synchronous logic circuit, the most common type of digital circuit, the clock signal is applied to all storage devices, flip-flops and latches, and causes them all to change state simultaneously, preventing race conditions. A clock signal is produced by an electronic oscillator called a clock generator. The most common clock signal is in the form of a square wave with a 50% duty cycle. Circuits using the clock signal for synchronization may become active at either the rising edge, falling edge, or, in the case of double data rate, both in the rising and in the falling edges of the clock cycle. Digital circuits Most integrated circuits (ICs) of suffi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Complex Instruction Set Computer

A complex instruction set computer (CISC ) is a computer architecture in which single instructions can execute several low-level operations (such as a load from memory, an arithmetic operation, and a memory store) or are capable of multi-step operations or addressing modes within single instructions. The term was retroactively coined in contrast to reduced instruction set computer (RISC) and has therefore become something of an umbrella term for everything that is not RISC, where the typical differentiating characteristic is that most RISC designs use uniform instruction length for almost all instructions, and employ strictly separate load and store instructions. Examples of CISC architectures include complex mainframe computers to simplistic microcontrollers where memory load and store operations are not separated from arithmetic instructions. Specific instruction set architectures that have been retroactively labeled CISC are System/360 through z/Architecture, the PDP-1 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

John L

"John L" is a song by English rock band Black Midi, released in 2021 as the lead single from their second studio album, ''Cavalcade (Black Midi album), Cavalcade''. The song describes the story of a powerful leader, the titular John L, who is eventually betrayed and killed by his followers. It was released on March 23, with the B-side Despair and a music video directed by Nina McNeely. A 12-inch release for the single was made available for pre-order on the same day and released on April 9. The song is one of few on ''Cavalcade'' to have writing credits for guitarist Matt Kwasniewski-Kelvin, written before his departure from the band but recorded after. Composition and recording "John L" is an Avant-garde music, avant-garde progressive rock song described by ''Guitar World'' as "[featuring] dissonant piano chimes, weaving hypnotic vocals, a cacophony of string sounds, and an edge-of-the-seat dynamic range, spanning from complete silence to raucous, high-energy midsections." ''Mi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MIPS Architecture

MIPS (Microprocessor without Interlocked Pipelined Stages) is a family of reduced instruction set computer (RISC) instruction set architectures (ISA)Price, Charles (September 1995). ''MIPS IV Instruction Set'' (Revision 3.2), MIPS Technologies, Inc. developed by MIPS Computer Systems, now MIPS Technologies, based in the United States. There are multiple versions of MIPS, including MIPS I, II, III, IV, and V, as well as five releases of MIPS32/64 (for 32- and 64-bit implementations, respectively). The early MIPS architectures were 32-bit; 64-bit versions were developed later. As of April 2017, the current version of MIPS is MIPS32/64 Release 6. MIPS32/64 primarily differs from MIPS I–V by defining the privileged kernel mode System Control Coprocessor in addition to the user mode architecture. The MIPS architecture has several optional extensions: MIPS-3D, a simple set of floating-point SIMD instructions dedicated to 3D computer graphics; MDMX (MaDMaX), a more extensive i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MIPS-X

MIPS-X is a reduced instruction set computer (RISC) microprocessor and instruction set architecture (ISA) developed as a follow-on project to the Stanford MIPS, MIPS project at Stanford University by the same team that developed MIPS. The project was supported by the Defense Advanced Research Projects Agency (DARPA) and began in 1984. Its final form was described in a set of papers released in 1986–87. Unlike its older cousin, MIPS-X was never commercialized as a workstation central processing unit (CPU), and has mainly been seen in embedded system designs based on chips designed by 8x8 Inc, Integrated Information Technology (IIT) for use in digital video applications. MIPS-X, while designed by the same team and architecturally very similar, is instruction-set incompatible with the mainline MIPS architecture R-series processors. The MIPS-X processor introduced the concept of a delayed branch, which includes two delay slots. An MIPS-X processor also includes a Processor Status Wo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Reduced Instruction Set Computer

In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set computer (CISC), a RISC computer might require more instructions (more code) in order to accomplish a task because the individual instructions perform simpler operations. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in particular by implementing an instruction pipeline, which may be simpler to achieve given simpler instructions. The key operational concept of the RISC computer is that each instruction performs only one function (e.g. copy a value from memory to a register). The RISC computer usually has many (16 or 32) high-speed, general-purpose registers with a load–store architecture in which the code for the register-register instructions (for performin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |