|

Secure Encrypted Virtualization

Zen is the first iteration in the Zen (microarchitecture), Zen family of computer processor microarchitectures from AMD. It was first used with their Ryzen series of CPUs in February 2017. The first Zen-based preview system was demonstrated at Electronic Entertainment Expo 2016, E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017 and Zen-based AMD Accelerated Processing Unit, APUs arrived in November 2017. Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer (microarchitecture), Bulldozer architecture. Zen-based processors use a 14 nanometer, 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. Simultaneous multithreading, SMT has been introduced, allowing each core to run two thr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD ZEN

Advanced Micro Devices, Inc. (AMD) is an American multinational corporation and technology company headquartered in Santa Clara, California and maintains significant operations in Austin, Texas. AMD is a Information technology, hardware and Fabless manufacturing, fabless company that designs and develops List of AMD processors, central processing units (CPUs), List of AMD graphics processing units, graphics processing units (GPUs), field-programmable gate arrays (FPGAs), System on a chip, system-on-chip (SoC), and high-performance computing, high-performance computer solutions. AMD serves a wide range of business and consumer markets, including gaming, data centers, artificial intelligence (AI), and embedded systems. AMD's main products include List of AMD microprocessors, microprocessors, motherboard chipsets, embedded processors, and List of AMD graphics processing units, graphics processors for Server (computing), servers, workstations, personal computers, and embedded syst ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Microarchitecture

In electronics, computer science and computer engineering, microarchitecture, also called computer organization and sometimes abbreviated as μarch or uarch, is the way a given instruction set architecture (ISA) is implemented in a particular processor. A given ISA may be implemented with different microarchitectures; implementations may vary due to different goals of a given design or due to shifts in technology. Computer architecture is the combination of microarchitecture and instruction set architecture. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the instructions, execution model, processor registers, address and data formats among other things. The microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen Microarchitecture

Zen is a family of computer processor microarchitectures from AMD, first launched in February 2017 with the first generation of Ryzen CPUs. It is used in Ryzen (desktop and mobile), Ryzen Threadripper (workstation and high-end desktop), and Epyc (server). Zen 5 is the latest iteration of the architecture. Comparison History First generation The first-generation Zen was launched with the Ryzen 1000 series of CPUs (codenamed Summit Ridge) in February 2017. The first Zen-based preview system was demonstrated at Electronic Entertainment Expo 2016, E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs reached the market in early March 2017, and Zen-derived Epyc server processors (codenamed "Naples") launched in June 2017 and Zen-based AMD Accelerated Processing Unit, APUs (codenamed "Raven Ridge") arrived in November 2017. This first iteration of Zen utilized GlobalFoundries' 14 nm manufac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Integrated Circuit

An integrated circuit (IC), also known as a microchip or simply chip, is a set of electronic circuits, consisting of various electronic components (such as transistors, resistors, and capacitors) and their interconnections. These components are etched onto a small, flat piece ("chip") of semiconductor material, usually silicon. Integrated circuits are used in a wide range of electronic devices, including computers, smartphones, and televisions, to perform various functions such as processing and storing information. They have greatly impacted the field of electronics by enabling device miniaturization and enhanced functionality. Integrated circuits are orders of magnitude smaller, faster, and less expensive than those constructed of discrete components, allowing a large transistor count. The IC's mass production capability, reliability, and building-block approach to integrated circuit design have ensured the rapid adoption of standardized ICs in place of designs using discre ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

System On A Chip

A system on a chip (SoC) is an integrated circuit that combines most or all key components of a computer or Electronics, electronic system onto a single microchip. Typically, an SoC includes a central processing unit (CPU) with computer memory, memory, input/output, and computer data storage#Secondary storage, data storage control functions, along with optional features like a graphics processing unit (GPU), Wi-Fi connectivity, and radio frequency processing. This high level of integration minimizes the need for separate, discrete components, thereby enhancing Performance per watt, power efficiency and simplifying device design. High-performance SoCs are often paired with dedicated memory, such as LPDDR, and flash storage chips, such as Universal Flash Storage, eUFS or eMMC, which may be stacked directly on top of the SoC in a Package on a package, package-on-package (PoP) configuration or placed nearby on the motherboard. Some SoCs also operate alongside specialized chips, such ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR4 SDRAM

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth (" double data rate") interface. Released to the market in 2014, it is a variant of dynamic random-access memory (DRAM), some of which have been in use since the early 1970s, and a higher-speed successor to the DDR2 and DDR3 technologies. DDR4 is not compatible with any earlier type of random-access memory (RAM) due to different signaling voltage and physical interface, besides other factors. DDR4 SDRAM was released to the public market in Q2 2014, focusing on ECC memory, while the non-ECC DDR4 modules became available in Q3 2014, accompanying the launch of Haswell-E processors that require DDR4 memory. Features The primary advantages of DDR4 over its predecessor, DDR3, include higher module density and lower voltage requirements, coupled with higher data rate transfer speeds. The DDR4 standard allows for DIMMs of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Write-back Cache

In computing, a cache ( ) is a hardware or software component that stores data so that future requests for that data can be served faster; the data stored in a cache might be the result of an earlier computation or a copy of data stored elsewhere. A cache hit occurs when the requested data can be found in a cache, while a cache miss occurs when it cannot. Cache hits are served by reading data from the cache, which is faster than recomputing a result or reading from a slower data store; thus, the more requests that can be served from the cache, the faster the system performs. To be cost-effective, caches must be relatively small. Nevertheless, caches are effective in many areas of computing because typical computer applications access data with a high degree of locality of reference. Such access patterns exhibit temporal locality, where data is requested that has been recently requested, and spatial locality, where data is requested that is stored near data that has already bee ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Simultaneous Multithreading

Simultaneous multithreading (SMT) is a technique for improving the overall efficiency of superscalar CPUs with hardware multithreading. SMT permits multiple independent threads of execution to better use the resources provided by modern processor architectures. Details The term ''multithreading'' is ambiguous, because not only can multiple threads be executed simultaneously on one CPU core, but also multiple tasks (with different page tables, different task state segments, different protection rings, different I/O permissions, etc.). Although running on the same core, they are completely separated from each other. Multithreading is similar in concept to preemptive multitasking but is implemented at the thread level of execution in modern superscalar processors. Simultaneous multithreading (SMT) is one of the two main implementations of multithreading, the other form being temporal multithreading (also known as super-threading). In temporal multithreading, only one thre ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instructions Per Cycle

In computer architecture, instructions per cycle (IPC), commonly called instructions per clock, is one aspect of a processor's performance: the average number of instructions executed for each clock cycle. It is the multiplicative inverse of cycles per instruction. Explanation While early generations of CPUs carried out all the steps to execute an instruction sequentially, modern CPUs can do many things in parallel. As it is impossible to just keep doubling the speed of the clock, instruction pipelining and superscalar processor design have evolved so CPUs can use a variety of execution units in parallel - looking ahead through the incoming instructions in order to optimise them. This leads to the ''instructions per cycle completed'' being much higher than 1 and is responsible for much of the speed improvements in subsequent CPU generations. Calculation of IPC The calculation of IPC is done through running a set piece of code, calculating the number of machine-level inst ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

14 Nanometer

The "14 nanometer process" refers to a marketing term for the MOSFET technology node that is the successor to the "22nm" (or "20nm") node. The "14nm" was so named by the International Technology Roadmap for Semiconductors (ITRS). Until about 2011, the node following "22nm" was expected to be "16nm". All "14nm" nodes use FinFET (fin field-effect transistor) technology, a type of multi-gate MOSFET technology that is a non-planar evolution of planar silicon CMOS technology. Since at least 1997, "process nodes" have been named purely on a marketing basis, and have no relation to the dimensions on the integrated circuit; neither gate length, metal pitch or gate pitch on a "14nm" device is fourteen nanometers. For example, TSMC and Samsung's "10 nm" processes are somewhere between Intel's "14 nm" and "10 nm" processes in transistor density, and TSMC's " 7 nm" processes are dimensionally similar to Intel's "10 nm" process. Samsung Electronics taped out a "1 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

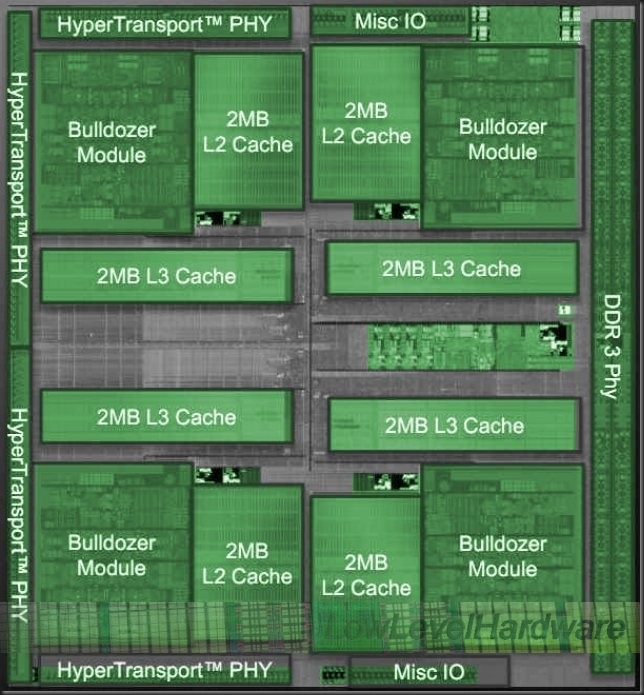

Bulldozer (microarchitecture)

The AMD Bulldozer Family 15h is a microprocessor microarchitecture for the FX and Opteron line of processors, developed by AMD for the desktop and server markets. Bulldozer is the codename for this family of microarchitectures. It was released on October 12, 2011, as the successor to the K10 microarchitecture. Bulldozer is designed from scratch, not a development of earlier processors. The core is specifically aimed at computing products with TDPs of 10 to 125 watts. AMD claims dramatic performance-per-watt efficiency improvements in high-performance computing (HPC) applications with Bulldozer cores. The ''Bulldozer'' cores support most of the instruction sets implemented by Intel processors ( Sandy Bridge) available at its introduction (including SSSE3, SSE4.1, SSE4.2, AES, CLMUL, and AVX) as well as new instruction sets proposed by AMD; ABM, XOP, FMA4 and F16C. Only Bulldozer GEN4 (Excavator) supports AVX2 instruction sets. Overview According to AMD, Bul ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |