|

Power4 Chip Schema

The POWER4 is a microprocessor developed by IBM, International Business Machines (IBM) that implemented the 64-bit PowerPC and PowerPC AS instruction set architectures. Released in 2001, the POWER4 succeeded the POWER3 and RS64 microprocessors, enabling RS/6000 and IBM AS/400, eServer iSeries models of AS/400 computer servers to run on the same processor, as a step toward converging the two lines. The POWER4 was a Multi-core processor, multicore microprocessor, with two cores on a single die, the first non-embedded microprocessor to do so. POWER4 Chip was first commercially available multiprocessor chip.William Stallings, ''Computer Organization and Architecture'', Seventh Edition, -pp 44 The original POWER4 had a clock speed of 1.1 and 1.3 GHz, while an enhanced version, the POWER4+, reached a clock speed of 1.9 GHz. The PowerPC 970 is a derivative of the POWER4. Functional layout The POWER4 has a unified L2 cache, divided into three equal parts. Each has its own in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC

PowerPC (with the backronym Performance Optimization With Enhanced RISC – Performance Computing, sometimes abbreviated as PPC) is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple Inc., Apple–IBM–Motorola alliance, known as AIM alliance, AIM. PowerPC, as an evolving instruction set, has been named Power ISA since 2006, while the old name lives on as a trademark for some implementations of Power Architecture–based processors. Originally intended for personal computers, the architecture is well known for being used by Apple's desktop and laptop lines from 1994 until 2006, and in several videogame consoles including Microsoft's Xbox 360, Sony's PlayStation 3, and Nintendo's GameCube, Wii, and Wii U. PowerPC was also used for the Curiosity (rover), Curiosity and Perseverance (rover), Perseverance rovers on Mars and a variety of satellites. It has since become a niche architecture for personal computers, particularly with A ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Power-on Reset

A power-on reset (PoR, POR) generator is a microcontroller or microprocessor peripheral that generates a reset signal when power is applied to the device. It ensures that the device starts operating in a known state. PoR generator In VLSI devices, the power-on reset (PoR) is an electronic device incorporated into the integrated circuit that detects the power applied to the chip and generates a reset impulse that goes to the entire circuit placing it into a known state. A simple PoR uses the charging of a capacitor, in series with a resistor, to measure a time period during which the rest of the circuit is held in a reset state. A Schmitt trigger may be used to deassert the reset signal cleanly, once the rising voltage of the RC network passes the threshold voltage of the Schmitt trigger. The resistor and capacitor values should be determined so that the charging of the RC network takes long enough that the supply voltage will have stabilised by the time the threshold is r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

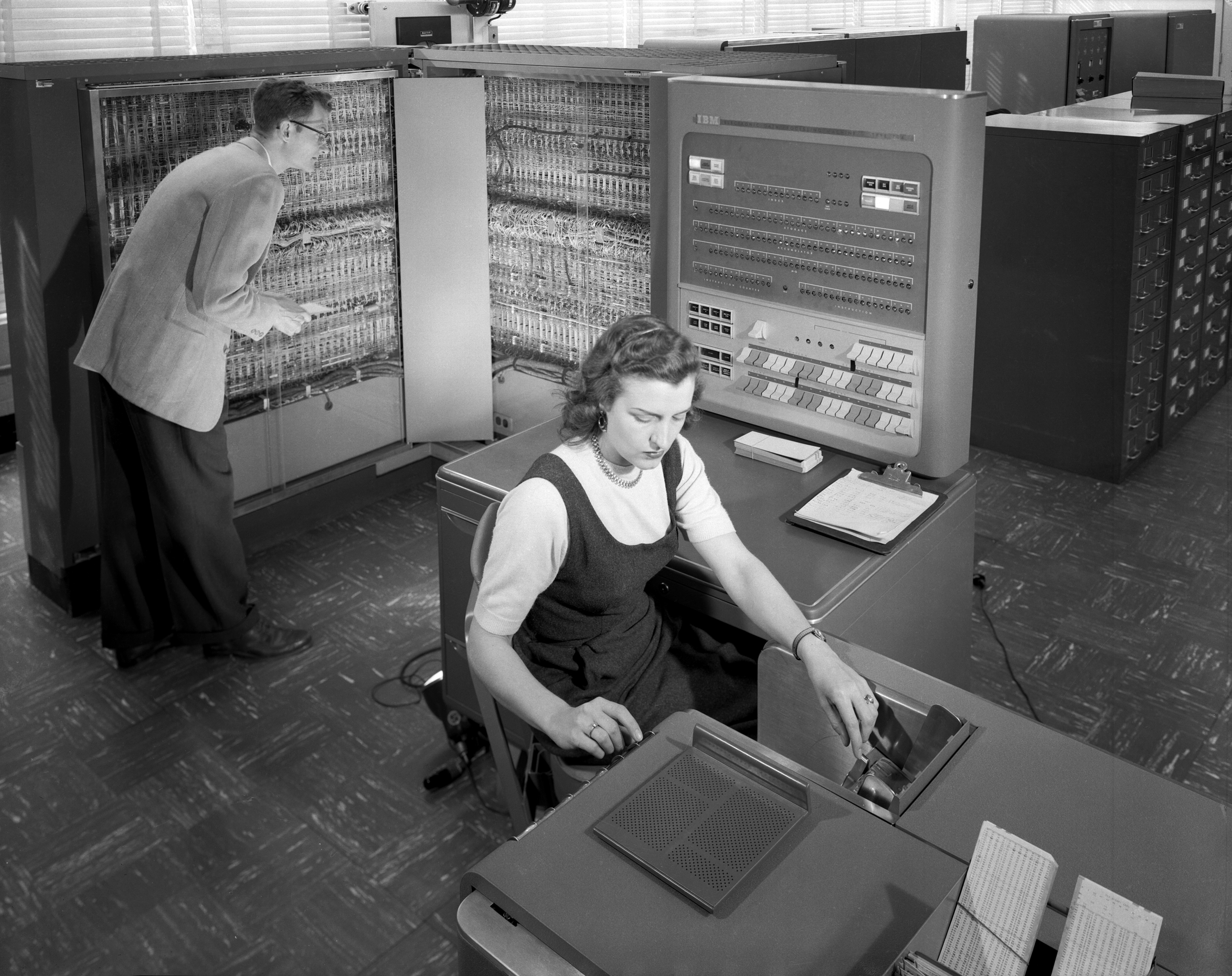

IBM Microprocessors

International Business Machines Corporation (using the trademark IBM), nicknamed Big Blue, is an American multinational technology company headquartered in Armonk, New York, and present in over 175 countries. It is a publicly traded company and one of the 30 companies in the Dow Jones Industrial Average. IBM is the largest industrial research organization in the world, with 19 research facilities across a dozen countries; for 29 consecutive years, from 1993 to 2021, it held the record for most annual U.S. patents generated by a business. IBM was founded in 1911 as the Computing-Tabulating-Recording Company (CTR), a holding company of manufacturers of record-keeping and measuring systems. It was renamed "International Business Machines" in 1924 and soon became the leading manufacturer of punch-card tabulating systems. During the 1960s and 1970s, the IBM mainframe, exemplified by the System/360 and its successors, was the world's dominant computing platform, with the company ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Microprocessor Report

''Microprocessor Report'' is a newsletter covering the microprocessor industry. The publication is accessible only to paying subscribers. To avoid bias, it does not take advertisements. The publication provides extensive analysis of new high-performance microprocessor chips. It also covers microprocessor design issues, microprocessor-based systems, memory and system logic chips, embedded processors, GPUs, DSPs, and intellectual property (IP) cores. History and profile ''Microprocessor Report'' was first published in 1987 by Michael Slater (engineer). Original board members included Bruce Koball, George Morrow, Brian Case, John Wakerly, Nick Tredennick, Bernard Peuto, Rich Belgard, Dennis Allison, and J H Wharton all of whom served for many years. Slater left MicroDesign Resources (MDR), at the end of 1999. Slater's company MDR, based in Sebastopol, California, originally published ''Microprocessor Report.'' MDR also hosted an annual conference, the Microprocessor Forum, and r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Power Microprocessors

Power microprocessors (originally POWER prior to Power10) are designed and sold by IBM for Server (computing), servers and supercomputers. The name "POWER" was originally presented as an acronym for "Performance Optimization With Enhanced RISC". The Power line of microprocessors has been used in IBM's RS/6000, IBM AS/400, AS/400, pSeries, iSeries, System p, System i, and IBM Power Systems, Power Systems lines of servers and supercomputers. They have also been used in data storage devices and workstations by IBM and by other server manufacturers like Groupe Bull, Bull and Hitachi. The Power family was originally developed in the late 1980s, and remains under active development. In the beginning, they implemented the IBM POWER Instruction Set Architecture, POWER instruction set architecture (ISA), which evolved into PowerPC and later into Power ISA. In August 2019, IBM announced it would open source the Power ISA. As part of the move, it was also announced that administration of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-chip Module

A multi-chip module (MCM) is generically an electronic assembly (such as a package with a number of conductor terminals or Lead (electronics), "pins") where multiple integrated circuits (ICs or "chips"), semiconductor Die (integrated circuit), dies and/or other discrete components are integrated, usually onto a unifying substrate, so that in use it can be treated as if it were a larger IC. Other terms for MCM packaging include "heterogeneous integration" or "hybrid integrated circuit". The advantage of using MCM packaging is it allows a manufacturer to use multiple components for modularity and/or to improve yields over a conventional monolithic IC approach. A Flip Chip Multi-Chip Module (FCMCM) is a multi-chip module that uses flip chip technology. A FCMCM may have one large die and several smaller dies all on the same module. Overview Multi-chip modules come in a variety of forms depending on the complexity and development philosophies of their designers. These can range from ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Fused Multiply–add

Fuse or FUSE may refer to: Devices * Fuse (electrical) In electronics and electrical engineering, a fuse is an electrical safety device that operates to provide overcurrent protection of an electrical circuit. Its essential component is a metal wire or strip that melts when too much current flows th ..., a device used in electrical systems to protect against excessive current ** Fuse (automotive), a class of fuses for vehicles * Fuse (hydraulic), a device used in hydraulic systems to protect against sudden loss of fluid pressure * Fuse (explosives) or fuze, the part of the device that initiates function * Fuze or fuse, a mechanism for exploding military munitions such as bombs, shells, and mines Computing * Fuse ESB, an open-source integration platform based on Apache Camel * Filesystem in Userspace, a virtual file system interface for Unix-like operating systems * Fuse (emulator), the Free Unix Spectrum Emulator of the ZX Spectrum * Fuse Internet Service, a former Ci ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Out-of-order Execution

In computer engineering, out-of-order execution (or more formally dynamic execution) is an instruction scheduling paradigm used in high-performance central processing units to make use of instruction cycles that would otherwise be wasted. In this paradigm, a processor executes instructions in an order governed by the availability of input data and execution units, rather than by their original order in a program. In doing so, the processor can avoid being idle while waiting for the preceding instruction to complete and can, in the meantime, process the next instructions that are able to run immediately and independently. History Out-of-order execution is a restricted form of dataflow architecture, which was a major research area in computer architecture in the 1970s and early 1980s. Early use in supercomputers The first machine to use out-of-order execution was the CDC 6600 (1964), designed by James E. Thornton, which uses a scoreboard to avoid conflicts. It permits ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Speculative Execution

Speculative execution is an optimization (computer science), optimization technique where a computer system performs some task that may not be needed. Work is done before it is known whether it is actually needed, so as to prevent a delay that would have to be incurred by doing the work after it is known that it is needed. If it turns out the work was not needed after all, most changes made by the work are reverted and the results are ignored. The objective is to provide more Concurrency (computer science), concurrency if extra Resource (computer science), resources are available. This approach is employed in a variety of areas, including branch predictor, branch prediction in instruction pipeline, pipelined CPU, processors, value prediction for exploiting value locality, prefetching Instruction prefetch, memory and File system, files, and optimistic concurrency control in Relational database management system, database systems. Speculative multithreading is a special case of specu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Microarchitecture

In electronics, computer science and computer engineering, microarchitecture, also called computer organization and sometimes abbreviated as μarch or uarch, is the way a given instruction set architecture (ISA) is implemented in a particular processor. A given ISA may be implemented with different microarchitectures; implementations may vary due to different goals of a given design or due to shifts in technology. Computer architecture is the combination of microarchitecture and instruction set architecture. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the instructions, execution model, processor registers, address and data formats among other things. The microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Superscalar

A superscalar processor (or multiple-issue processor) is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a superscalar processor can execute or start executing more than one instruction during a clock cycle by simultaneously dispatching multiple instructions to different execution units on the processor. It therefore allows more throughput (the number of instructions that can be executed in a unit of time which can even be less than 1) than would otherwise be possible at a given clock rate. Each execution unit is not a separate processor (or a core if the processor is a multi-core processor), but an execution resource within a single CPU such as an arithmetic logic unit. While a superscalar CPU is typically also pipelined, superscalar and pipelining execution are considered different performance enhancement techni ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |