|

Modified Harvard Architecture

A modified Harvard architecture is a variation of the Harvard computer architecture that, unlike the pure Harvard architecture, allows memory that contains instructions to be accessed as data. Most modern computers that are documented as Harvard architecture are, in fact, modified Harvard architecture. Harvard architecture The original Harvard architecture computer, the Harvard Mark I, employed entirely separate memory systems to store instructions and data. The CPU fetched the next instruction and loaded or stored data simultaneously and independently. This is in contrast to a von Neumann architecture computer, in which both instructions and data are stored in the same memory system and (without the complexity of a CPU cache) must be accessed in turn. The physical separation of instruction and data memory is sometimes held to be the distinguishing feature of modern Harvard architecture computers. With microcontrollers (entire computer systems integrated onto single chips) ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Harvard Architecture

The Harvard architecture is a computer architecture with separate computer storage, storage and signal pathways for Machine code, instructions and data. It is often contrasted with the von Neumann architecture, where program instructions and data share the same memory and pathways. This architecture is often used in real-time processing or low-power applications. The term is often stated as having originated from the Harvard Mark I relay-based computer, which stored instructions on punched tape (24 bits wide) and data in electro-mechanical counters. These early machines had data storage entirely contained within the central processing unit, and provided no access to the instruction storage as data. Programs needed to be loaded by an operator; the processor could not Booting, initialize itself. However, in the only peer-reviewed paper on the topic published in 2022 the author states that: * 'The term "Harvard architecture" was coined decades later, in the context of microcontr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

EEPROM

EEPROM or E2PROM (electrically erasable programmable read-only memory) is a type of non-volatile memory. It is used in computers, usually integrated in microcontrollers such as smart cards and remote keyless systems, or as a separate chip device, to store relatively small amounts of data by allowing individual bytes to be erased and reprogrammed. EEPROMs are organized as arrays of floating-gate transistors. EEPROMs can be programmed and erased in-circuit, by applying special programming signals. Originally, EEPROMs were limited to single-byte operations, which made them slower, but modern EEPROMs allow multi-byte page operations. An EEPROM has a limited life for erasing and reprogramming, reaching a million operations in modern EEPROMs. In an EEPROM that is frequently reprogrammed, the life of the EEPROM is an important design consideration. Flash memory is a type of EEPROM designed for high speed and high density, at the expense of large erase blocks (typically 512 b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Intel 8051

The Intel MCS-51 (commonly termed 8051) is a single-chip microcontroller (MCU) series developed by Intel in 1980 for use in embedded systems. The architect of the Intel MCS-51 instruction set was John H. Wharton.. Intel's original versions were popular in the 1980s and early 1990s, and enhanced binary compatible derivatives remain popular today. It is a complex instruction set computer with separate memory spaces for program instructions and data. Intel's original MCS-51 family was developed using N-type metal–oxide–semiconductor ( NMOS) technology, like its predecessor Intel MCS-48, but later versions, identified by a letter C in their name (e.g., 80C51) use complementary metal–oxide–semiconductor ( CMOS) technology and consume less power than their NMOS predecessors. This made them more suitable for battery-powered devices. The family was continued in 1996 with the enhanced 8-bit MCS-151 and the 8/ 16/32-bit MCS-251 family of binary compatible microcontrollers. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

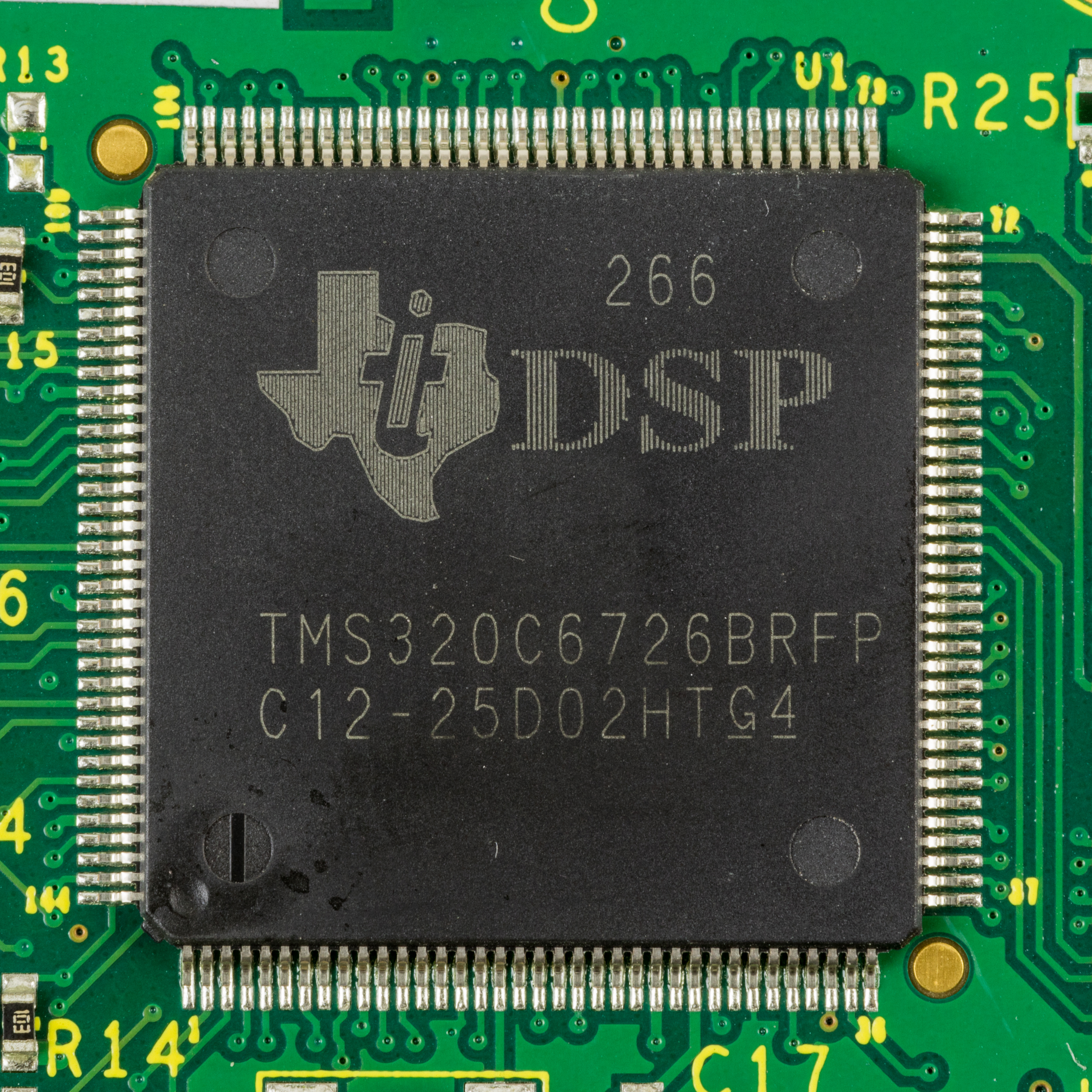

Texas Instruments TMS320

TMS320 is a blanket name for a series of digital signal processors (DSPs) from Texas Instruments. It was introduced on April 8, 1983, through the TMS32010 processor, which was then the fastest DSP on the market. The processor is available in many different variants, some with fixed-point arithmetic and some with floating-point arithmetic. The TMS320 processors were fabricated on MOS integrated circuit chips, including both NMOS and CMOS variants. The floating-point DSP TMS320C3x, which exploits delayed branch logic, has as many as three delay slots. This series of processors are used as a digital signal processing co-processor and as the main CPU in some applications. Newer implementations support standard IEEE JTAG control for boundary scan and/or in-circuit debugging. The original TMS32010 and its subsequent variants are an example of a CPU with a modified Harvard architecture, which features separate address spaces for instruction and data memory but the ability to read da ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

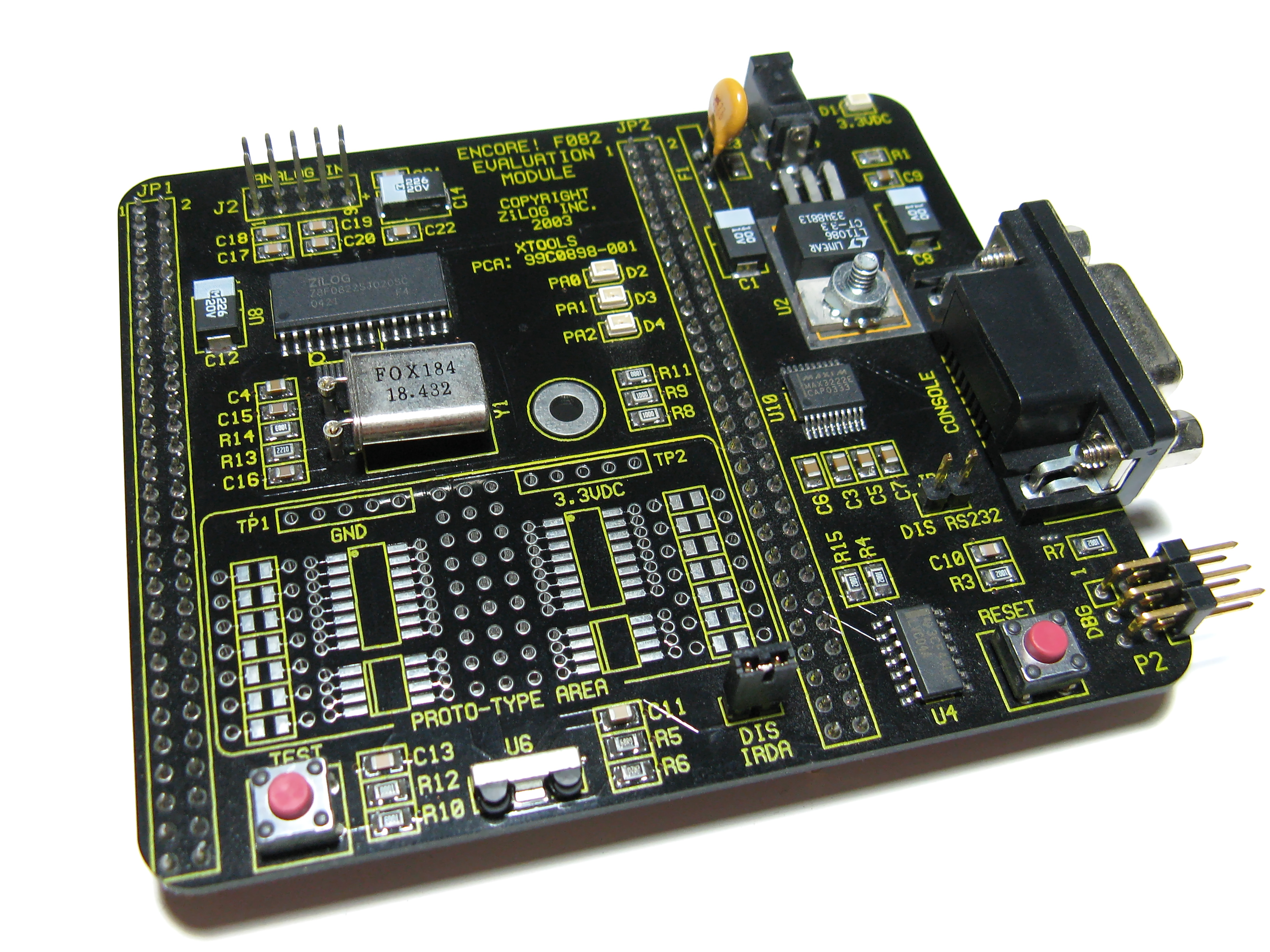

Z8 Encore!

The Zilog Z8 Encore! is a microcontroller based on the popular Z8 microcontroller A microcontroller (MC, uC, or μC) or microcontroller unit (MCU) is a small computer on a single integrated circuit. A microcontroller contains one or more CPUs (processor cores) along with memory and programmable input/output peripherals. Pro .... The Z8 Encore! offers a wide range of features for use in embedded applications, most notably the use of three DMA channels to read for example from the analog-to-digital converter (ADC). The Z8 Encore! instruction set is compatible with that of the Z8 but it provides some extensions for use with high-level languages. The Z8 Encore! features a single-pin debugging interface. External links Official site of ZiLOG, Inc.Z8 Encore! page on Zilog site Microcontrollers Zilog microprocessors {{Microcompu-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Atmel AVR

AVR is a family of microcontrollers developed since 1996 by Atmel, acquired by Microchip Technology in 2016. They are 8-bit RISC single-chip microcontrollers based on a modified Harvard architecture. AVR was one of the first microcontroller families to use on-chip flash memory for program storage, as opposed to Programmable read-only memory, one-time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time. AVR microcontrollers are used numerously as embedded systems. They are especially common in hobbyist and educational embedded applications, popularized by their inclusion in many of the Arduino line of open hardware development boards. The AVR 8-bit microcontroller architecture was introduced in 1997. By 2003, Atmel had shipped 500 million AVR flash microcontrollers. History The AVR architecture was conceived by two students at the Norwegian Institute of Technology (NTH), Alf-Egil Bogen and Vegard Wollan.Archived aGhostarchiveand thWayback Machine ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Digital Signal Processors

A digital signal processor (DSP) is a specialized microprocessor chip, with its architecture optimized for the operational needs of digital signal processing. DSPs are fabricated on metal–oxide–semiconductor (MOS) integrated circuit chips. They are widely used in audio signal processing, telecommunications, digital image processing, radar, sonar and speech recognition systems, and in common consumer electronic devices such as mobile phones, disk drives and high-definition television (HDTV) products. The goal of a DSP is usually to measure, filter or compress continuous real-world analog signals. Most general-purpose microprocessors can also execute digital signal processing algorithms successfully, but may not be able to keep up with such processing continuously in real-time. Also, dedicated DSPs usually have better power efficiency, thus they are more suitable in portable devices such as mobile phones because of power consumption constraints. DSPs often use special memor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

ARM9

ARM9 is a group of 32-bit RISC ARM processor cores licensed by ARM Holdings for microcontroller use. The ARM9 core family consists of ARM9TDMI, ARM940T, ARM9E-S, ARM966E-S, ARM920T, ARM922T, ARM946E-S, ARM9EJ-S, ARM926EJ-S, ARM968E-S, ARM996HS. ARM9 cores were released from 1998 to 2006, and no longer recommended for new IC designs; newer alternatives are ARM Cortex-M cores. Overview With this design generation, ARM moved from a von Neumann architecture (Princeton architecture) to a (modified; meaning split cache) Harvard architecture with separate instruction and data buses (and caches), significantly increasing its potential speed. Most silicon chips integrating these cores will package them as modified Harvard architecture chips, combining the two address buses on the other side of separated CPU caches and tightly coupled memories. There are two subfamilies, implementing different ARM architecture versions. Differences from ARM7 cores Key improvements over ARM7 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

ARM7TDMI

ARM7 is a group of 32-bit RISC ARM processor cores licensed by ARM Holdings for microcontroller use. The ARM7 core family consists of ARM700, ARM710, ARM7DI, ARM710a, ARM720T, ARM740T, ARM710T, ARM7TDMI, ARM7TDMI-S, ARM7EJ-S. The ARM7TDMI and ARM7TDMI-S were the most popular cores of the family. ARM7 cores were released from 1993 to 2001 and no longer recommended for new IC designs; newer alternatives are ARM Cortex-M cores. Overview This generation introduced the Thumb 16-bit instruction set providing improved code density compared to previous designs. The most widely used ARM7 designs implement the ARMv4T architecture, but some implement ARMv3 or ARMv5TEJ. ARM7TDMI has 37 registers (31 GPR and 6 SPR). All these designs use a Von Neumann architecture, thus the few versions containing a cache do not separate data and instruction caches. Some ARM7 cores are obsolete. One historically significant model, the ARM7DI"ARM7DI Data Sheet"; Document Number ARM DDI 0027D; Issued: De ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Static Random Access Memory

Static random-access memory (static RAM or SRAM) is a type of random-access memory (RAM) that uses latching circuitry (flip-flop) to store each bit. SRAM is volatile memory; data is lost when power is removed. The ''static'' qualifier differentiates SRAM from ''dynamic'' random-access memory (DRAM): * SRAM will hold its data permanently in the presence of power, while data in DRAM decays in seconds and thus must be periodically refreshed. * SRAM is faster than DRAM but it is more expensive in terms of silicon area and cost. * Typically, SRAM is used for the cache and internal registers of a CPU while DRAM is used for a computer's main memory. History Semiconductor bipolar SRAM was invented in 1963 by Robert Norman at Fairchild Semiconductor. Metal–oxide–semiconductor SRAM (MOS-SRAM) was invented in 1964 by John Schmidt at Fairchild Semiconductor. The first device was a 64-bit MOS p-channel SRAM. SRAM was the main driver behind any new CMOS-based technology fabrica ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

PIC Microcontroller

PIC (usually pronounced as /pɪk/) is a family of microcontrollers made by Microchip Technology, derived from the PIC1640 originally developed by General Instrument's Microelectronics Division. The name PIC initially referred to ''Peripheral Interface Controller'',"MOS DATA 1976", General Instrument 1976 Databook and was subsequently expanded for a short time to include ''Programmable Intelligent Computer'', though the name PIC is no longer used as an acronym for any term. The first parts of the family were available in 1976; by 2013 the company had shipped more than twelve billion individual parts, used in a wide variety of embedded systems. The PIC was originally designed as a peripheral for the General Instrument CP1600, the first commercially available single-chip 16-bit microprocessor. To limit the number of pins required, the CP1600 had a complex highly- multiplexed bus which was difficult to interface with, so in addition to a variety of special-purpose peripherals ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Punched Tape

file:PaperTapes-5and8Hole.jpg, Five- and eight-hole wide punched paper tape file:Harwell-dekatron-witch-10.jpg, Paper tape reader on the Harwell computer with a small piece of five-hole tape connected in a circle – creating a physical program loop Punched tape or perforated paper tape is a form of data storage that consists of a long strip of paper through which small holes are punched. It was developed from and was subsequently used alongside punched cards, the difference being that the tape is continuous. Punched cards, and chains of punched cards, were used for control of looms in the 18th century. Use for telegraphy systems started in 1842. Punched tapes were used throughout the 19th and for much of the 20th centuries for programmable looms, teleprinter communication, for input to computers of the 1950s and 1960s, and later as a storage medium for minicomputers and Numerical control, CNC machine tools. During the Second World War, high-speed punched tape systems using opti ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |