|

MCST-4R

The MCST R1000 (russian: МЦСТ R1000) is a 64-bit microprocessor developed by Moscow Center of SPARC Technologies (MCST) and fabricated by TSMC. During development this microprocessor was designated as MCST-4R. MCST R1000 Highlights *implements the SPARC V9 instruction set architecture (ISA) *quad-core *core specifications: **in-order, dual-issue superscalar **7-stage integer pipeline **9-stage floating-point pipeline ** VIS extensions 1 and 2 ** Multiply–accumulate unit **16 KB L1 instruction cache ( parity protection) **32 KB L1 data cache ( parity protection) **size 7.6 mm2 *shared 2MB L2 cache ( ECC protection) *integrated memory controller *integrated ccNUMA controller *1 GHz clock rate *90 nm process The 90 nm process refers to the level of MOSFET (CMOS) fabrication process technology that was commercialized by the 2003–2005 timeframe, by leading semiconductor companies like Toshiba, Sony, Samsung, IBM, Intel, Fujitsu, TSMC, Elpid ... *die size 1 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FPGA Prototype

Field-programmable gate array prototyping (FPGA prototyping), also referred to as FPGA-based prototyping, ASIC prototyping or system-on-chip (SoC) prototyping, is the method to prototype system-on-chip and application-specific integrated circuit designs on FPGAs for hardware verification and early software development. Verification methods for hardware design as well as early software and firmware co-design have become mainstream. Prototyping SoC and ASIC designs with one or more FPGAs and electronic design automation (EDA) software has become a good method to do this. Why prototyping is important #Running a SoC design on FPGA prototype is a reliable way to ensure that it is functionally correct. This is compared to designers only relying on software simulations to verify that their hardware design is sound. About a third of all current SoC designs are fault-free during first silicon pass, with nearly half of all re-spins caused by functional logic errors. A single proto ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instruction Pipeline

In computer engineering, instruction pipelining or ILP is a technique for implementing instruction-level parallelism within a single processor. Pipelining attempts to keep every part of the processor busy with some instruction by dividing incoming instructions into a series of sequential steps (the eponymous "pipeline") performed by different processor units with different parts of instructions processed in parallel. Concept and motivation In a pipelined computer, instructions flow through the central processing unit (CPU) in stages. For example, it might have one stage for each step of the von Neumann cycle: Fetch the instruction, fetch the operands, do the instruction, write the results. A pipelined computer usually has "pipeline registers" after each stage. These store information from the instruction and calculations so that the logic gates of the next stage can do the next step. This arrangement lets the CPU complete an instruction on each clock cycle. It is common for ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

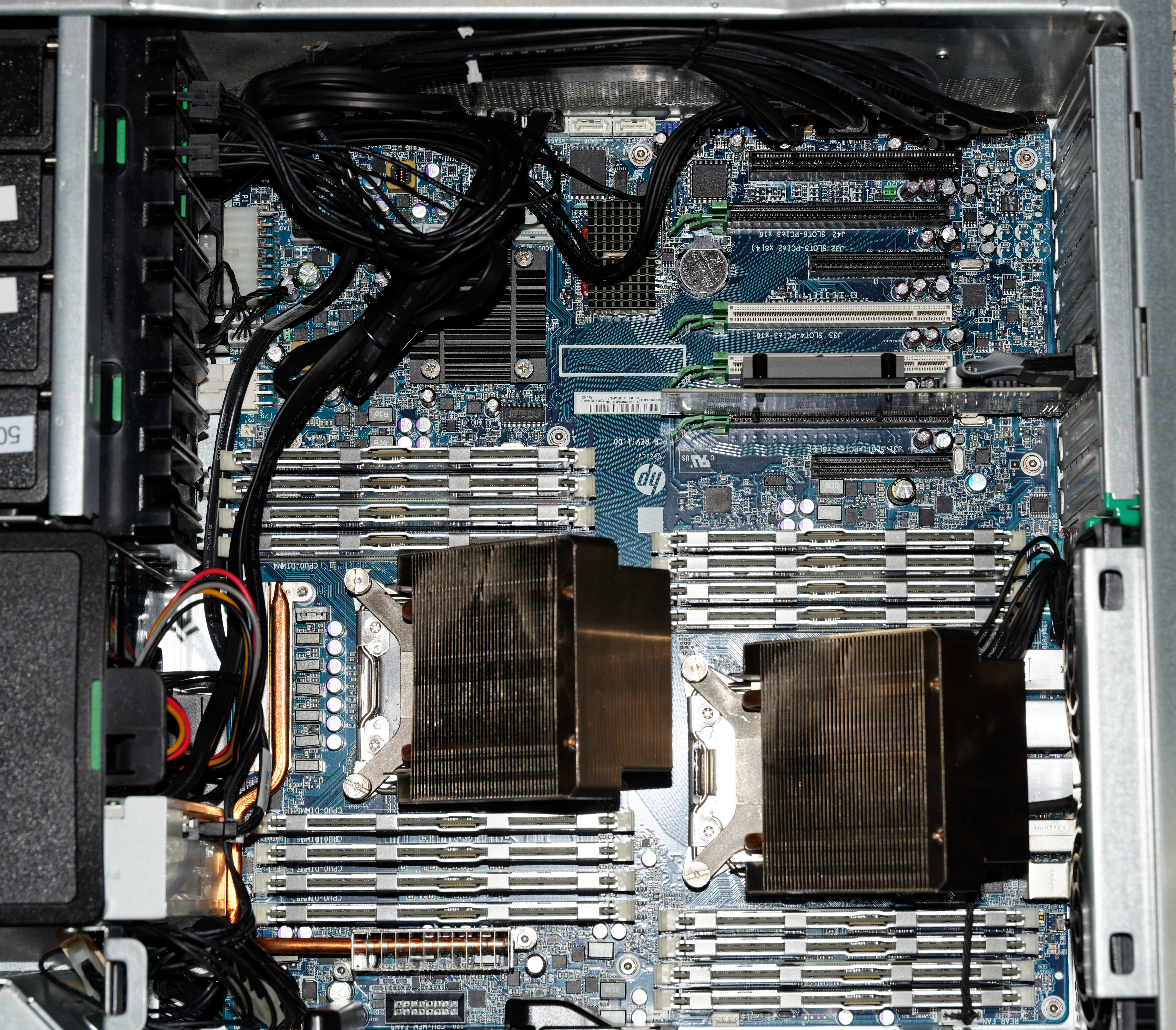

MCST-4R CcNUMA System

The MCST R1000 (russian: МЦСТ R1000) is a 64-bit microprocessor developed by Moscow Center of SPARC Technologies (MCST) and fabricated by TSMC. During development this microprocessor was designated as MCST-4R. MCST R1000 Highlights *implements the SPARC V9 instruction set architecture (ISA) *quad-core *core specifications: **in-order, dual-issue superscalar **7-stage integer pipeline **9-stage floating-point pipeline ** VIS extensions 1 and 2 ** Multiply–accumulate unit **16 KB L1 instruction cache ( parity protection) **32 KB L1 data cache ( parity protection) **size 7.6 mm2 *shared 2MB L2 cache ( ECC protection) *integrated memory controller *integrated ccNUMA controller *1 GHz clock rate *90 nm process The 90 nm process refers to the level of MOSFET ( CMOS) fabrication process technology that was commercialized by the 2003–2005 timeframe, by leading semiconductor companies like Toshiba, Sony, Samsung, IBM, Intel, Fujitsu, TSMC, El ... *die size ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MCST-4R Diagram

The MCST R1000 (russian: МЦСТ R1000) is a 64-bit microprocessor developed by Moscow Center of SPARC Technologies (MCST) and fabricated by TSMC. During development this microprocessor was designated as MCST-4R. MCST R1000 Highlights *implements the SPARC V9 instruction set architecture (ISA) *quad-core *core specifications: **in-order, dual-issue superscalar **7-stage integer pipeline **9-stage floating-point pipeline ** VIS extensions 1 and 2 ** Multiply–accumulate unit **16 KB L1 instruction cache ( parity protection) **32 KB L1 data cache ( parity protection) **size 7.6 mm2 *shared 2MB L2 cache ( ECC protection) *integrated memory controller *integrated ccNUMA controller *1 GHz clock rate *90 nm process The 90 nm process refers to the level of MOSFET ( CMOS) fabrication process technology that was commercialized by the 2003–2005 timeframe, by leading semiconductor companies like Toshiba, Sony, Samsung, IBM, Intel, Fujitsu, TSMC, El ... *die size ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MCST-4R Pipeline

The MCST R1000 (russian: МЦСТ R1000) is a 64-bit microprocessor developed by Moscow Center of SPARC Technologies (MCST) and fabricated by TSMC. During development this microprocessor was designated as MCST-4R. MCST R1000 Highlights *implements the SPARC V9 instruction set architecture (ISA) *quad-core *core specifications: **in-order, dual-issue superscalar **7-stage integer pipeline **9-stage floating-point pipeline ** VIS extensions 1 and 2 ** Multiply–accumulate unit **16 KB L1 instruction cache ( parity protection) **32 KB L1 data cache ( parity protection) **size 7.6 mm2 *shared 2MB L2 cache ( ECC protection) *integrated memory controller *integrated ccNUMA controller *1 GHz clock rate *90 nm process The 90 nm process refers to the level of MOSFET ( CMOS) fabrication process technology that was commercialized by the 2003–2005 timeframe, by leading semiconductor companies like Toshiba, Sony, Samsung, IBM, Intel, Fujitsu, TSMC, El ... *die size ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MCST-4R Core

The MCST R1000 (russian: МЦСТ R1000) is a 64-bit microprocessor developed by Moscow Center of SPARC Technologies (MCST) and fabricated by TSMC. During development this microprocessor was designated as MCST-4R. MCST R1000 Highlights *implements the SPARC V9 instruction set architecture (ISA) *quad-core *core specifications: **in-order, dual-issue superscalar **7-stage integer pipeline **9-stage floating-point pipeline ** VIS extensions 1 and 2 ** Multiply–accumulate unit **16 KB L1 instruction cache ( parity protection) **32 KB L1 data cache ( parity protection) **size 7.6 mm2 *shared 2MB L2 cache ( ECC protection) *integrated memory controller *integrated ccNUMA controller *1 GHz clock rate *90 nm process The 90 nm process refers to the level of MOSFET ( CMOS) fabrication process technology that was commercialized by the 2003–2005 timeframe, by leading semiconductor companies like Toshiba, Sony, Samsung, IBM, Intel, Fujitsu, TSMC, El ... *die size ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

90 Nanometer

The 90 nm process refers to the level of MOSFET ( CMOS) fabrication process technology that was commercialized by the 2003–2005 timeframe, by leading semiconductor companies like Toshiba, Sony, Samsung, IBM, Intel, Fujitsu, TSMC, Elpida, AMD, Infineon, Texas Instruments and Micron Technology. The origin of the 90 nm value is historical, it reflects a trend of 70% scaling every 2–3 years. The naming is formally determined by the International Technology Roadmap for Semiconductors (ITRS). The 193 nm wavelength was introduced by many (but not all) companies for lithography of critical layers mainly during the 90 nm node. Yield issues associated with this transition (due to the use of new photoresists) were reflected in the high costs associated with this transition. Even more significantly, the 300 mm wafer size became mainstream at the 90 nm node. The previous wafer size was 200 mm diameter. History A 90nm silicon MOSFET was fabric ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Clock Rate

In computing, the clock rate or clock speed typically refers to the frequency at which the clock generator of a processor can generate pulses, which are used to synchronize the operations of its components, and is used as an indicator of the processor's speed. It is measured in the SI unit of frequency hertz (Hz). The clock rate of the first generation of computers was measured in hertz or kilohertz (kHz), the first personal computers (PCs) to arrive throughout the 1970s and 1980s had clock rates measured in megahertz (MHz), and in the 21st century the speed of modern CPUs is commonly advertised in gigahertz (GHz). This metric is most useful when comparing processors within the same family, holding constant other features that may affect performance. Determining factors Binning Manufacturers of modern processors typically charge premium prices for processors that operate at higher clock rates, a practice called binning. For a given CPU, the clock rates are determined at th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CcNUMA

Non-uniform memory access (NUMA) is a computer memory design used in multiprocessing, where the memory access time depends on the memory location relative to the processor. Under NUMA, a processor can access its own local memory faster than non-local memory (memory local to another processor or memory shared between processors). The benefits of NUMA are limited to particular workloads, notably on servers where the data is often associated strongly with certain tasks or users. NUMA architectures logically follow in scaling from symmetric multiprocessing (SMP) architectures. They were developed commercially during the 1990s by Unisys, Convex Computer (later Hewlett-Packard), Honeywell Information Systems Italy (HISI) (later Groupe Bull), Silicon Graphics (later Silicon Graphics International), Sequent Computer Systems (later IBM), Data General (later EMC, now Dell Technologies), and Digital (later Compaq, then HP, now HPE). Techniques developed by these companies later fea ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

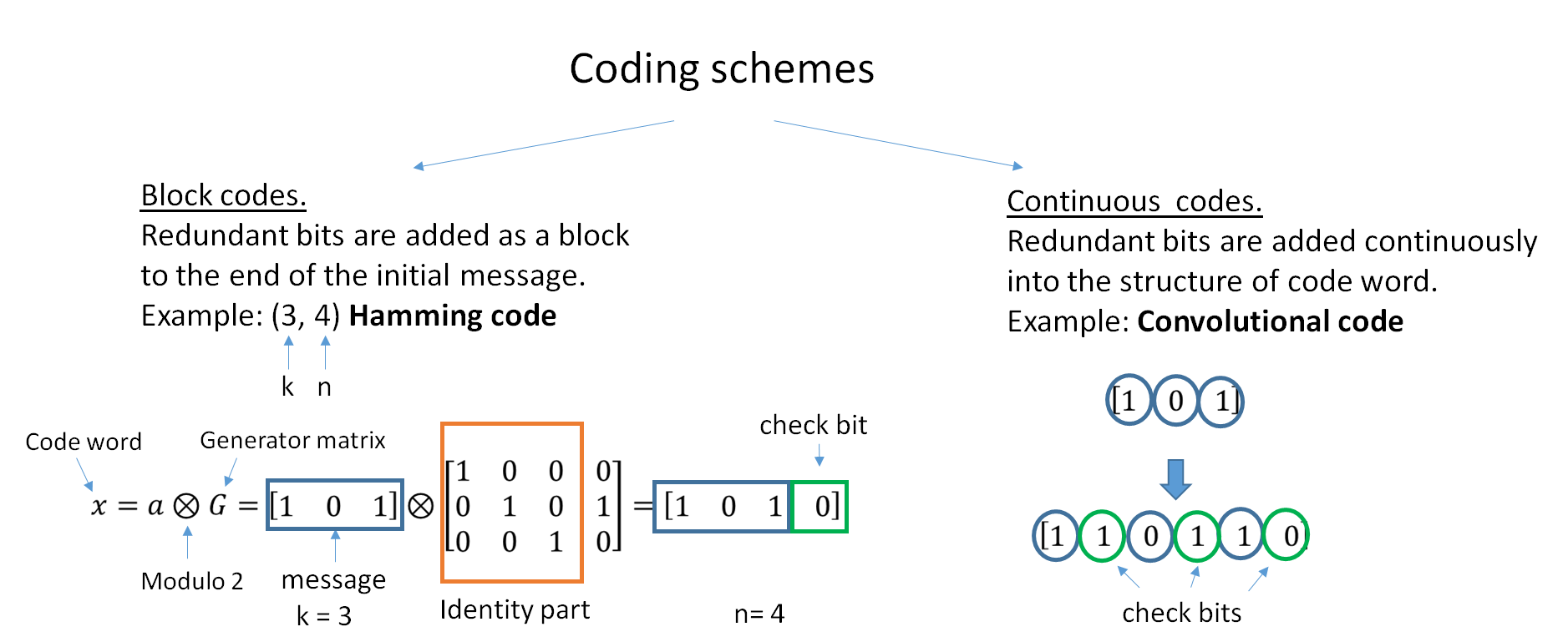

Error-correcting Code

In computing, telecommunication, information theory, and coding theory, an error correction code, sometimes error correcting code, (ECC) is used for controlling errors in data over unreliable or noisy communication channels. The central idea is the sender encodes the message with redundant information in the form of an ECC. The redundancy allows the receiver to detect a limited number of errors that may occur anywhere in the message, and often to correct these errors without retransmission. The American mathematician Richard Hamming pioneered this field in the 1940s and invented the first error-correcting code in 1950: the Hamming (7,4) code. ECC contrasts with error detection in that errors that are encountered can be corrected, not simply detected. The advantage is that a system using ECC does not require a reverse channel to request retransmission of data when an error occurs. The downside is that there is a fixed overhead that is added to the message, thereby requiring a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Parity (telecommunication)

A parity bit, or check bit, is a bit added to a string of binary code. Parity bits are a simple form of error detecting code. Parity bits are generally applied to the smallest units of a communication protocol, typically 8-bit octets (bytes), although they can also be applied separately to an entire message string of bits. The parity bit ensures that the total number of 1-bits in the string is even or odd. Accordingly, there are two variants of parity bits: even parity bit and odd parity bit. In the case of even parity, for a given set of bits, the bits whose value is 1 are counted. If that count is odd, the parity bit value is set to 1, making the total count of occurrences of 1s in the whole set (including the parity bit) an even number. If the count of 1s in a given set of bits is already even, the parity bit's value is 0. In the case of odd parity, the coding is reversed. For a given set of bits, if the count of bits with a value of 1 is even, the parity bit value is set ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |