|

List Of AMD Accelerated Processing Unit Microprocessors

This is a list of microprocessors designed by AMD, under the AMD Accelerated Processing Unit product series. Features overview Graphics API overview Desktop APUs Lynx: "Llano" (2011) * Socket FM1 * CPU: K10 (or ''Husky'' or K10.5) with no L3 cache cores with an upgraded architecture known as ''Stars'' ** L1 Cache: 64 KB Data per core and 64 KB Instructions per core * ''MMX, Enhanced 3DNow!, SSE, SSE2, SSE3, SSE4a, ABM, NX bit, AMD64, Cool'n'Quiet'', ''AMD-V'' * GPU: TeraScale 2 (Evergreen); all A and E series models feature ''Redwood''-class integrated graphics on die (''BeaverCreek'' for the dual-core variants and ''WinterPark'' for the quad-core variants). Sempron and Athlon models exclude integrated graphics. * List of embedded GPU's * Support for up to four DIMMs of up to DDR3-1866 memory * Fabrication 32 nm on GlobalFoundries SOI process; Die size: , with 1.178 billion transistors * 5 GT/s UMI * Integrated PCIe 2.0 controller * Select models suppo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD Accelerated Processing Unit

AMD Accelerated Processing Unit (APU), formerly known as Fusion, is a series of 64-bit microprocessors from Advanced Micro Devices (AMD), combining a general-purpose AMD64 central processing unit ( CPU) and integrated graphics processing unit (IGPU) on a single die. AMD announced the first generation APUs, ''Llano'' for high-performance and ''Brazos'' for low-power devices, in January 2011. The second generation ''Trinity'' for high-performance and ''Brazos-2'' for low-power devices were announced in June 2012. The third generation ''Kaveri'' for high performance devices were launched in January 2014, while ''Kabini'' and ''Temash'' for low-power devices were announced in the summer of 2013. Since the launch of the Zen microarchitecture, Ryzen and Athlon APUs have released to the global market as Raven Ridge on the DDR4 platform, after Bristol Ridge a year prior. AMD has also supplied semi-custom APUs for consoles starting with the release of Sony PlayStation 4 and Microsoft ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR3

Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth ("double data rate") interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors. DDR3 is a DRAM interface specification. The actual DRAM arrays that store the data are similar to earlier types, with similar performance. The primary benefit of DDR3 SDRAM over its immediate predecessor DDR2 SDRAM, is its ability to transfer data at twice the rate (eight times the speed of its internal memory arrays), enabling higher bandwidth or peak data rates. The DDR3 standard permits DRAM chip capacities of up to 8 gigabits (Gbit), and up to four ranks o ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

L1 Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) whic ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GFLOPS

In computing, floating point operations per second (FLOPS, flops or flop/s) is a measure of computer performance, useful in fields of scientific computations that require floating-point calculations. For such cases, it is a more accurate measure than measuring instructions per second. Floating-point arithmetic Floating-point arithmetic is needed for very large or very small real numbers, or computations that require a large dynamic range. Floating-point representation is similar to scientific notation, except everything is carried out in base two, rather than base ten. The encoding scheme stores the sign, the exponent (in base two for Cray and VAX, base two or ten for IEEE floating point formats, and base 16 for IBM Floating Point Architecture) and the significand (number after the radix point). While several similar formats are in use, the most common is ANSI/IEEE Std. 754-1985. This standard defines the format for 32-bit numbers called ''single precision'', as well as 64-b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cache Memory

In computing, a cache ( ) is a hardware or software component that stores data so that future requests for that data can be served faster; the data stored in a cache might be the result of an earlier computation or a copy of data stored elsewhere. A ''cache hit'' occurs when the requested data can be found in a cache, while a ''cache miss'' occurs when it cannot. Cache hits are served by reading data from the cache, which is faster than recomputing a result or reading from a slower data store; thus, the more requests that can be served from the cache, the faster the system performs. To be cost-effective and to enable efficient use of data, caches must be relatively small. Nevertheless, caches have proven themselves in many areas of computing, because typical computer applications access data with a high degree of locality of reference. Such access patterns exhibit temporal locality, where data is requested that has been recently requested already, and spatial locality, where d ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Thread (computing)

In computer science, a thread of execution is the smallest sequence of programmed instructions that can be managed independently by a scheduler, which is typically a part of the operating system. The implementation of threads and processes differs between operating systems. In Modern Operating Systems, Tanenbaum shows that many distinct models of process organization are possible.TANENBAUM, Andrew S. Modern Operating Systems. 1992. Prentice-Hall International Editions, ISBN 0-13-595752-4. In many cases, a thread is a component of a process. The multiple threads of a given process may be executed concurrently (via multithreading capabilities), sharing resources such as memory, while different processes do not share these resources. In particular, the threads of a process share its executable code and the values of its dynamically allocated variables and non- thread-local global variables at any given time. History Threads made an early appearance under the name of "tasks ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-core Processor

A multi-core processor is a microprocessor on a single integrated circuit with two or more separate processing units, called cores, each of which reads and executes program instructions. The instructions are ordinary CPU instructions (such as add, move data, and branch) but the single processor can run instructions on separate cores at the same time, increasing overall speed for programs that support multithreading or other parallel computing techniques. Manufacturers typically integrate the cores onto a single integrated circuit die (known as a chip multiprocessor or CMP) or onto multiple dies in a single chip package. The microprocessors currently used in almost all personal computers are multi-core. A multi-core processor implements multiprocessing in a single physical package. Designers may couple cores in a multi-core device tightly or loosely. For example, cores may or may not share caches, and they may implement message passing or shared-memory inter-core communica ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Thermal Design Power

The thermal design power (TDP), sometimes called thermal design point, is the maximum amount of heat generated by a computer chip or component (often a CPU, GPU or system on a chip) that the cooling system in a computer is designed to dissipate under any workload. Some sources state that the peak power rating for a microprocessor is usually 1.5 times the TDP rating. Intel has introduced a new metric called ''scenario design power'' (SDP) for some Ivy Bridge Y-series processors. Calculation The ''average CPU power'' (ACP) is the power consumption of central processing units, especially server processors, under "average" daily usage as defined by Advanced Micro Devices (AMD) for use in its line of processors based on the K10 microarchitecture ( Opteron 8300 and 2300 series processors). Intel's thermal design power (TDP), used for Pentium and Core 2 processors, measures the energy consumption under high workload; it is numerically somewhat higher than the "average" ACP rat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Stepping (version Numbers)

In integrated circuits, the stepping level or revision level is a version number that refers to the introduction or revision of one or more photolithographic photomasks within the set of photomasks that is used to pattern an integrated circuit. The term originated from the name of the equipment ( "steppers") that exposes the photoresist to light. Integrated circuits have two primary classes of mask sets: firstly, "base" layers that are used to build the structures, such as transistors, that comprise circuit logic and, secondly, "metal" layers that connect the circuit logic. Typically, when an integrated circuit manufacturer such as Intel or AMD produces a new stepping (i.e. a revision to the masks), it is because it has found bugs in the logic, has made improvements to the design that permit faster processing, has found a way to increase yield or improve the "bin splits" (i.e. create faster transistors and thus faster CPUs), has improved maneuverability to more easily identify ma ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

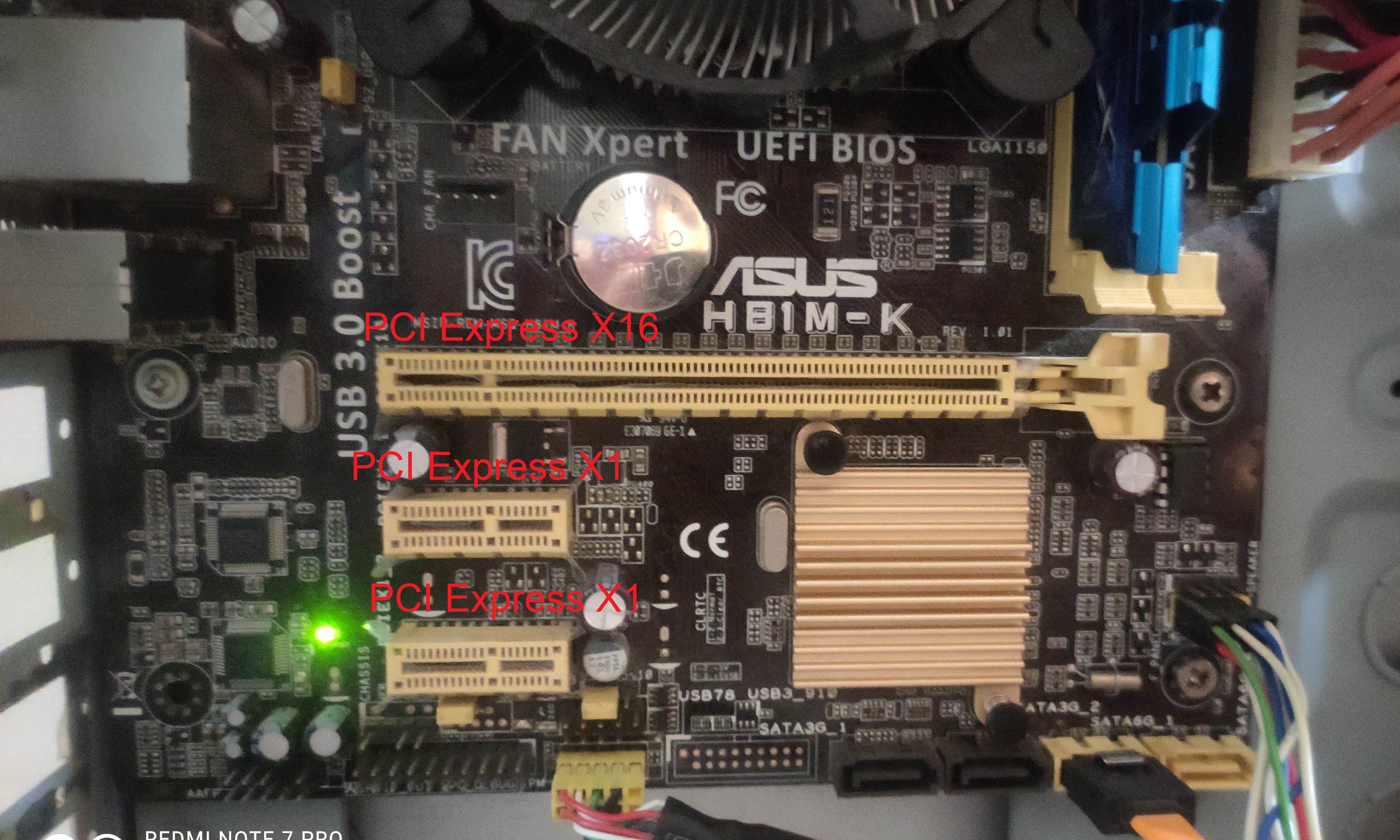

PCIE

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directions.) T ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

UMI AMD

The UMI (Unified Media Interface) interconnect is the link between an AMD Accelerated Processing Unit (APU) and the FCH (Fusion Controller Hub).. It is similar to Intel Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 seri ...'s DMI. The Fusion Controller Hub is similar to the Southbridge of earlier chipsets. References AMD technologies Computer buses {{computer-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Die (integrated Circuit)

A die, in the context of integrated circuits, is a small block of semiconducting material on which a given functional circuit is fabricated. Typically, integrated circuits are produced in large batches on a single wafer of electronic-grade silicon (EGS) or other semiconductor (such as GaAs) through processes such as photolithography. The wafer is cut (diced) into many pieces, each containing one copy of the circuit. Each of these pieces is called a die. There are three commonly used plural forms: ''dice'', ''dies'' and ''die''. To simplify handling and integration onto a printed circuit board, most dies are packaged in various forms. Manufacturing process Most dies are composed of silicon and used for integrated circuits. The process begins with the production of monocrystalline silicon ingots. These ingots are then sliced into disks with a diameter of up to 300 mm. [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

-top_PNr°0359.jpg)