|

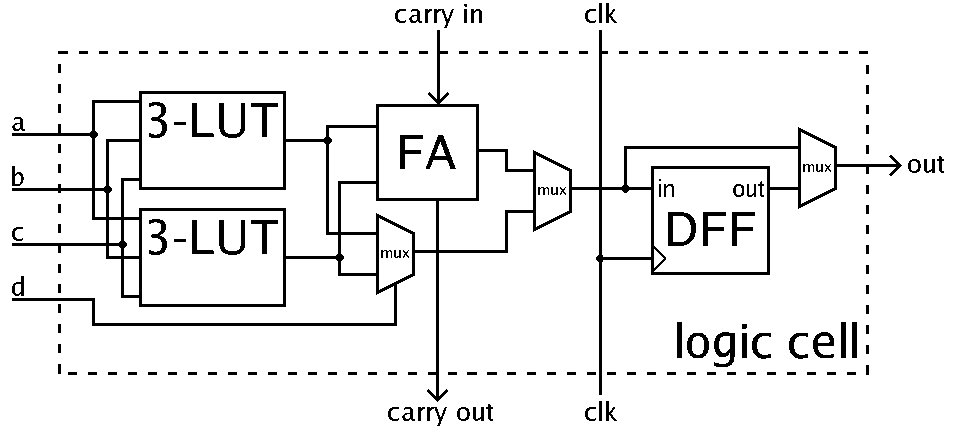

Logic Block

In computing, a logic block or configurable logic block (CLB) is a fundamental building block of field-programmable gate array (FPGA) technology. Logic blocks can be configured by the engineer to provide reconfigurable logic gates. Logic blocks are the most common FPGA architecture, and are usually laid out within a logic block array. Logic blocks require I/O pads (to interface with external signals), and routing channels (to interconnect logic blocks). Programmable logic blocks were invented by David W. Page and LuVerne R. Peterson, and defined within their 1985 patents.Google Patent Search,Re-programmable PLA. Filed January 11, 1983. Granted April 2, 1985. Retrieved February 5, 2009.Google Patent Search,Dynamic data re-programmable PLA. Filed January 11, 1983. Granted June 18, 1985. Retrieved February 5, 2009. Applications An application circuit must be mapped into an FPGA with adequate resources. While the number of logic blocks and I/Os required is easily determined from the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Computing

Computing is any goal-oriented activity requiring, benefiting from, or creating computing machinery. It includes the study and experimentation of algorithmic processes, and development of both hardware and software. Computing has scientific, engineering, mathematical, technological and social aspects. Major computing disciplines include computer engineering, computer science, cybersecurity, data science, information systems, information technology and software engineering. The term "computing" is also synonymous with counting and calculating. In earlier times, it was used in reference to the action performed by mechanical computing machines, and before that, to human computers. History The history of computing is longer than the history of computing hardware and includes the history of methods intended for pen and paper (or for chalk and slate) with or without the aid of tables. Computing is intimately tied to the representation of numbers, though mathematical ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Interposer

An interposer is an electrical interface routing between one socket or connection to another. The purpose of an interposer is to spread a connection to a wider pitch or to reroute a connection to a different connection. Interposer comes from the Latin word "interpōnere", meaning "to put between". They are often used in BGA packages, multi-chip modules and high bandwidth memory. A common example of an interposer is an integrated circuit die to BGA, such as in the Pentium II. This is done through various substrates, both rigid and flexible, most commonly FR4 for rigid, and polyimide for flexible. Silicon and glass are also evaluated as an integration method. Interposer stacks are also a widely accepted, cost-effective alternative to 3D ICs. There are already several products with interposer technology in the market, notably the AMD Fiji/Fury GPU, and the Xilinx Virtex-7 FPGA. In 2016, CEA Leti demonstrated their second generation 3D-NoC technology which combines small ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Jitter

In electronics and telecommunications, jitter is the deviation from true periodicity of a presumably periodic signal, often in relation to a reference clock signal. In clock recovery applications it is called timing jitter. Jitter is a significant, and usually undesired, factor in the design of almost all communications links. Jitter can be quantified in the same terms as all time-varying signals, e.g., root mean square (RMS), or peak-to-peak displacement. Also, like other time-varying signals, jitter can be expressed in terms of spectral density. Jitter period is the interval between two times of maximum effect (or minimum effect) of a signal characteristic that varies regularly with time. Jitter frequency, the more commonly quoted figure, is its inverse. ITU-T G.810 classifies jitter frequencies below 10 Hz as wander and frequencies at or above 10 Hz as jitter. Jitter may be caused by electromagnetic interference and crosstalk with carriers of other signals. Jitte ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

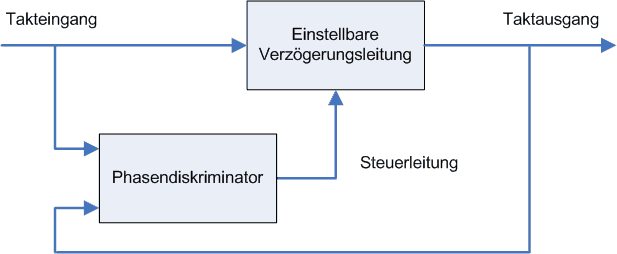

Delay-locked Loop

In electronics, a delay-locked loop (DLL) is a pseudo-digital circuit similar to a phase-locked loop (PLL), with the main difference being the absence of an internal voltage-controlled oscillator, replaced by a delay line. A DLL can be used to change the phase of a clock signal (a signal with a periodic waveform), usually to enhance the ''clock rise''-to-''data output valid'' timing characteristics of integrated circuits (such as DRAM devices). DLLs can also be used for clock recovery (CDR). From the outside, a DLL can be seen as a negative delay gate placed in the clock path of a digital circuit. The main component of a DLL is a delay chain composed of many delay gates connected output-to-input. The input of the chain (and thus of the DLL) is connected to the clock that is to be negatively delayed. A multiplexer is connected to each stage of the delay chain; a control circuit automatically updates the selector of this multiplexer to produce the negative delay effect. The output ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Phase-locked Loop

A phase-locked loop or phase lock loop (PLL) is a control system that generates an output signal whose phase is related to the phase of an input signal. There are several different types; the simplest is an electronic circuit consisting of a variable frequency oscillator and a phase detector in a feedback loop. The oscillator's frequency and phase are controlled proportionally by an applied voltage, hence the term voltage-controlled oscillator (VCO). The oscillator generates a periodic signal of a specific frequency, and the phase detector compares the phase of that signal with the phase of the input periodic signal, to adjust the oscillator to keep the phases matched. Keeping the input and output phase in lockstep also implies keeping the input and output frequencies the same. Consequently, in addition to synchronizing signals, a phase-locked loop can track an input frequency, or it can generate a frequency that is a multiple of the input frequency. These properties are u ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Clock Skew

Clock skew (sometimes called timing skew) is a phenomenon in synchronous digital circuit systems (such as computer systems) in which the same sourced clock signal arrives at different components at different times due to gate or, in more advanced semiconductor technology, wire signal propagation delay. The instantaneous difference between the readings of any two clocks is called their skew. The operation of most digital circuits is synchronized by a periodic signal known as a " clock" that dictates the sequence and pacing of the devices on the circuit. This clock is distributed from a single source to all the memory elements of the circuit, which for example could be registers or flip-flops. In a circuit using edge-triggered registers, when the clock edge or tick arrives at a register, the register transfers the register input to the register output, and these new output values flow through combinational logic to provide the values at register inputs for the next clock tick. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

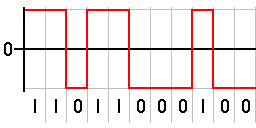

Line Code

In telecommunication, a line code is a pattern of voltage, current, or photons used to represent digital data transmission (telecommunications), transmitted down a communication channel or written to a storage medium. This repertoire of signals is usually called a constrained code in data storage systems. Some signals are more prone to error than others as the physics of the communication channel or storage medium constrains the repertoire of signals that can be used reliably. Common line encodings are Unipolar encoding, unipolar, Polar encoding, polar, Bipolar encoding, bipolar, and Manchester code. Transmission and storage After line coding, the signal is put through a physical communication channel, either a transmission medium or data storage medium.Karl Paulsen"Coding for Magnetic Storage Mediums".2007. The most common physical channels are: * the line-coded signal can directly be put on a transmission line, in the form of variations of the voltage or current (often usin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

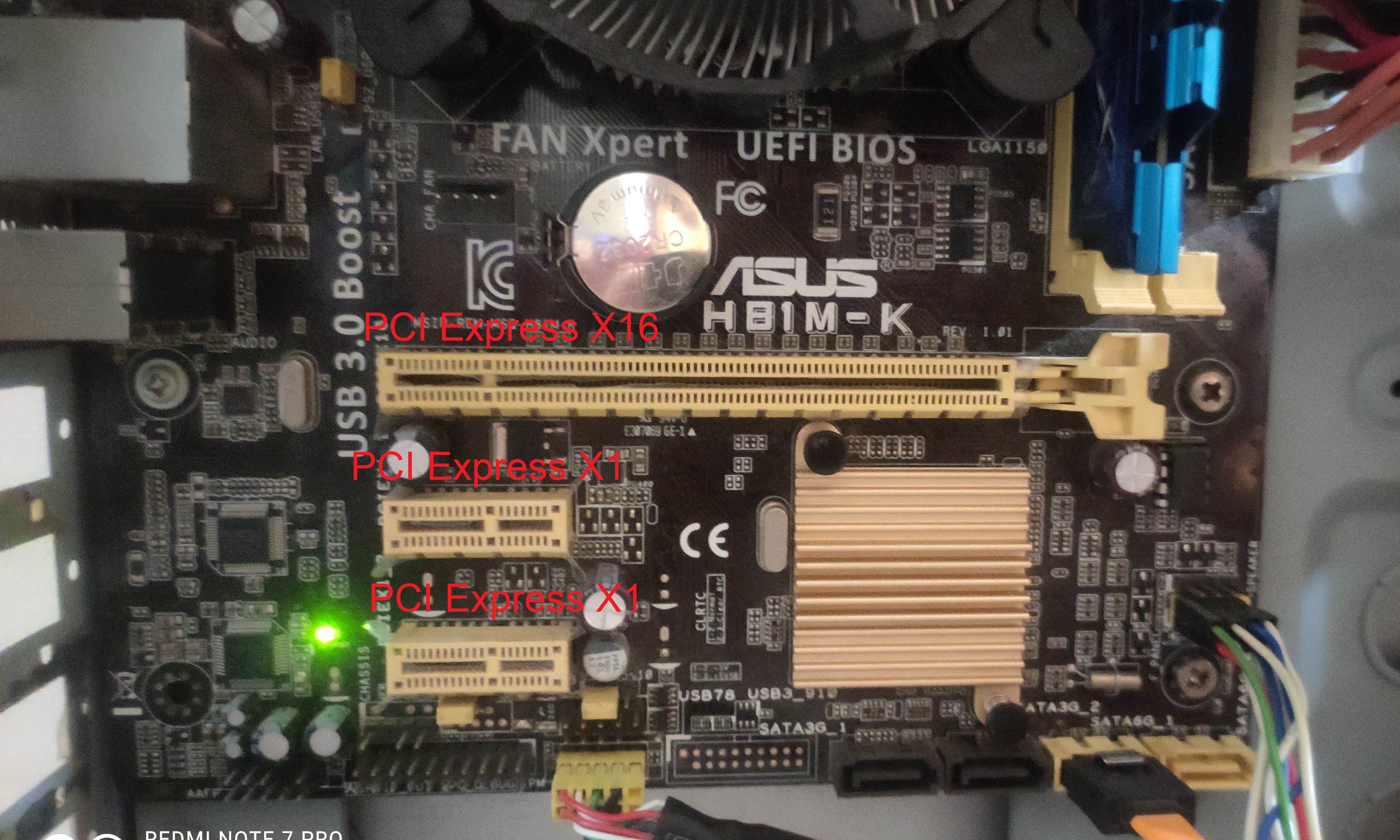

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both direc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Conventional PCI

Peripheral Component Interconnect (PCI) is a local computer bus for attaching hardware devices in a computer and is part of the PCI Local Bus standard. The PCI bus supports the functions found on a processor bus but in a standardized format that is independent of any given processor's native bus. Devices connected to the PCI bus appear to a bus master to be connected directly to its own bus and are assigned addresses in the processor's address space. It is a parallel bus, synchronous to a single bus clock. Attached devices can take either the form of an integrated circuit fitted onto the motherboard (called a ''planar device'' in the PCI specification) or an expansion card that fits into a slot. The PCI Local Bus was first implemented in IBM PC compatibles, where it displaced the combination of several slow Industry Standard Architecture (ISA) slots and one fast VESA Local Bus (VLB) slot as the bus configuration. It has subsequently been adopted for other computer types ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Media Access Control

In IEEE 802 LAN/MAN standards, the medium access control (MAC, also called media access control) sublayer is the layer that controls the hardware responsible for interaction with the wired, optical or wireless transmission medium. The MAC sublayer and the logical link control (LLC) sublayer together make up the data link layer. The LLC provides flow control and multiplexing for the logical link (i.e. EtherType, 802.1Q VLAN tag etc), while the MAC provides flow control and multiplexing for the transmission medium. These two sublayers together correspond to layer 2 of the OSI model. For compatibility reasons, LLC is optional for implementations of IEEE 802.3 (the frames are then "raw"), but compulsory for implementations of other IEEE 802 physical layer standards. Within the hierarchy of the OSI model and IEEE 802 standards, the MAC sublayer provides a control abstraction of the physical layer such that the complexities of physical link control are invisible to the LLC and upp ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ethernet

Ethernet () is a family of wired computer networking technologies commonly used in local area networks (LAN), metropolitan area networks (MAN) and wide area networks (WAN). It was commercially introduced in 1980 and first standardized in 1983 as IEEE 802.3. Ethernet has since been refined to support higher bit rates, a greater number of nodes, and longer link distances, but retains much backward compatibility. Over time, Ethernet has largely replaced competing wired LAN technologies such as Token Ring, FDDI and ARCNET. The original 10BASE5 Ethernet uses coaxial cable as a shared medium, while the newer Ethernet variants use twisted pair and fiber optic links in conjunction with switches. Over the course of its history, Ethernet data transfer rates have been increased from the original to the latest , with rates up to under development. The Ethernet standards include several wiring and signaling variants of the OSI physical layer. Systems communicating over ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Switch Box

A KVM switch (with KVM being an abbreviation for "keyboard, video, and mouse") is a hardware device that allows a user to control multiple computers from one or more sets of keyboards, video monitors, and mice. Name Switches to connect multiple computers to one or more peripherals have had a variety of names. The earliest name was Keyboard Video Switch (KVS). With the advent of the mouse, the Keyboard, Video and Mouse (KVM) switch became popular. The name was introduced by Remigius Shatas, the founder of Cybex, a peripheral switch manufacturer, in 1995. Some companies call their switches Keyboard, Video, Mouse and Peripheral (KVMP). Types With the popularity of USB—USB keyboards, mice, and I/O devices are still the most common devices connected to a KVM switch. The classes of KVM switches that are reviewed, are based on different types of core technologies in terms of how the KVM switch handles USB I/O devices—including keyboards, mice, touchscreen displays, etc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |